TSEK11 - Evaluation of an Integrated Circuit

Period 1

Credits: 2 HP

News

| 9 Oct. 2017 | Website updated for the 2017 course. |

| 13 Sept. 2016 | Website updated for the 2016 course. |

| 16 Sept. 2015 | Website updated for the 2015 course. |

| 17 Oct. 2014 | The chip photos for chip 1 are available. |

| 11 Aug. 2014 | Website updated for the 2014 course. |

| 25 Sep. 2013 | The chip photos are available. |

| 6 Sep. 2013 | Website updated for the 2013 course. |

Course Description

This course is a follow-up to TSEK06 VLSI Design Project and gives the students a possibility to test and evaluate their chip designs.

Required Background

The student must have attended TSEK06 VLSI Design Project and sent a chip for fabrication.

Examination

The only grades given are fail and pass. These will be based on both the evaluation effort and a written report that describes the evaluation and the outcome of it. Also a short presentation of the measurment is required.

The report should be handed in to the supervisors by the end of the course. The exact date will be posted on this page later.

Staff

-

Instructor

Atila Alvandpour, Professor

Electronic Devices, Department of Electrical Engineering (ISY)

Office 3D:523, B-huset

Tel: 013-285818

E-mail: atila@isy.liu.se -

Head Teaching Assistant

Martin Nielsen-Lönn, Ph.D. Student

Electronic Devices, Department of Electrical Engineering (ISY)

Office 3D:535, B-huset

E-mail: martin.nielsen.lonn@liu.se

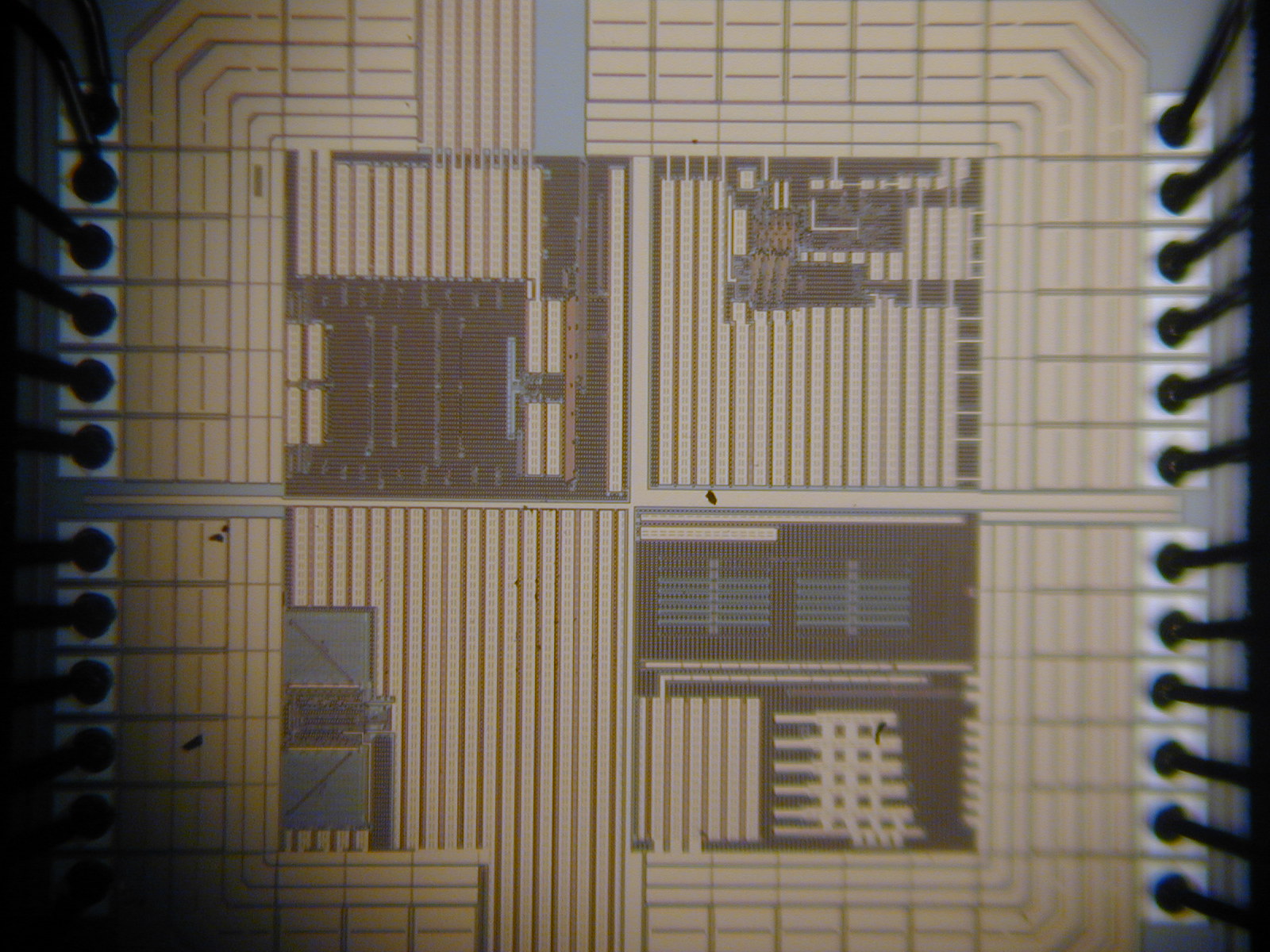

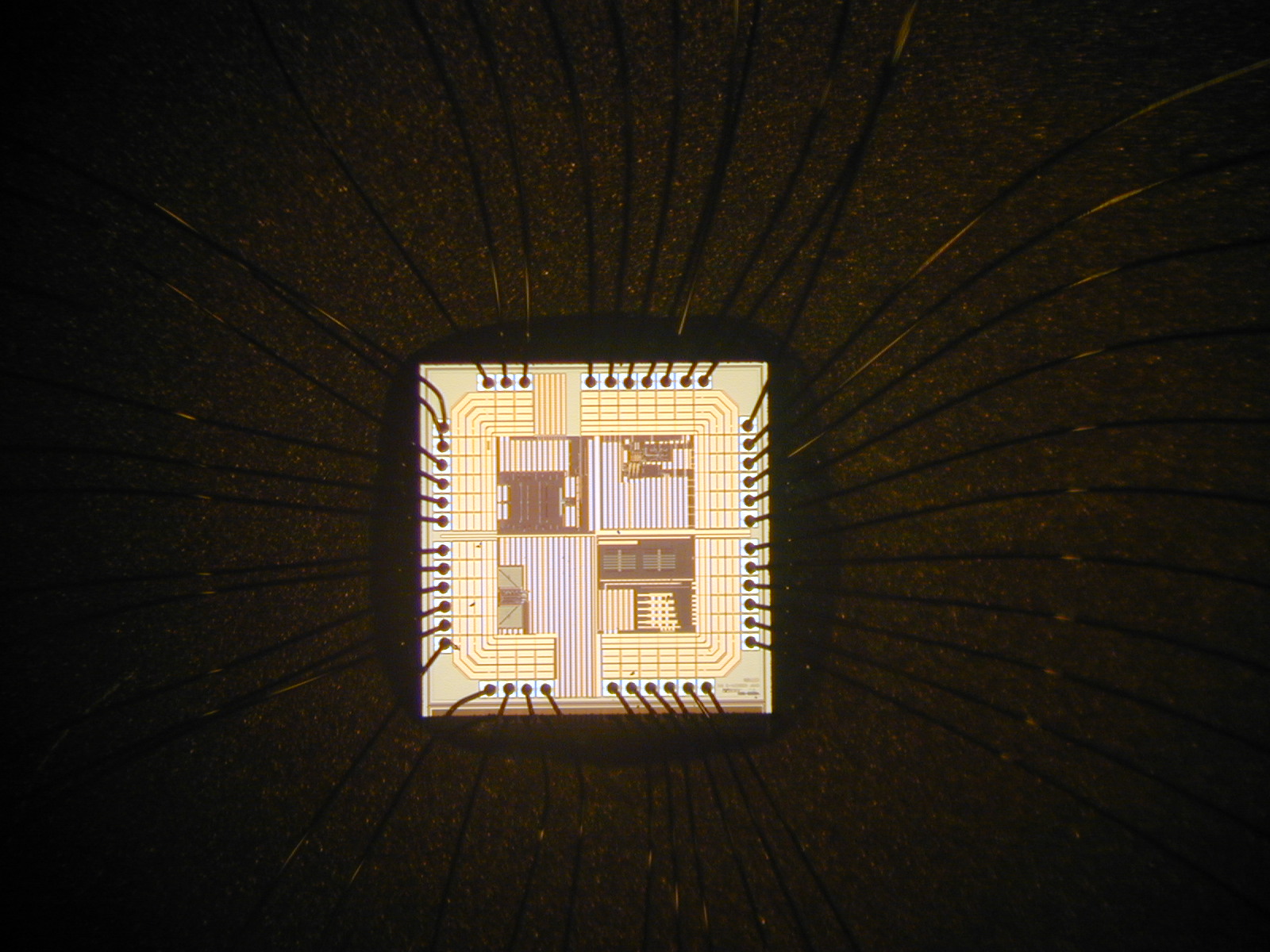

Chip photos 2016

Chip 1 - group 1, 2, 4, 5

Chip 1 - group 1, 2, 4, 5

Chip 1 - group 1, 2, 4, 5

Chip 1 - group 1, 2, 4, 5

PCB information

You can find the PCB schematic, layout, and bonding diagram under course material here on the website or in the folder /site/edu/eks/TSEK11/2017/pub/ on ISY servers.

Schematic Chip 1 - Group 2, 3, 4, and 6

Layout Chip 1 - Group 2, 3, 4, and 6

Bonding Diagram Chip 1 - Group 2, 3, 4, and 6

Schematic Chip 2 - Group 1 and 5

Bonding Diagram Chip 2 - Group 1 and 5

Mead Lab Bookings

The Mead lab will be used for soldering of your printed circuit board (PCB) as well as the actual measurement of your chip.

Each day consists of two time slots, morning (8-12) and afternoon (13-17). This is done to make it easier to fit in your schedules, but for efficiency reasons, you will probably want to book complete days if possible. Each group is allowed to book two complete days, ie. four slots. Aim to finish during those. Should there be need for more time after that, we will discuss it at that point in time.

The procedure to book a slot is to first find times where the group and the supervisor are available; then check for the availability of those times in the table below; and finally send an e-mail to the head TA with a booking request for those slots.

| Slots | Monday | Tuesday | Wednesday | Thursday | Friday |

|---|---|---|---|---|---|

| Week 42 | 16/10 | 17/10 | 18/10 | 19/10 | 20/10 |

| 8-12 | Available | Available | Available | Available | Available |

| 13-17 | Available | Available | Available | Available | Available |

| Week 43 | 23/10 | 24/10 | 25/10 | 26/10 | 27/10 |

| 8-12 | Available | Available | Available | Group 5 | Group 5 |

| 13-17 | Available | Available | Available | Group 5 | Group 5 |

| Week 44 | 30/10 | 31/10 | 1/11 | 2/11 | 3/11 |

| 8-12 | Available | Available | Available | Group 6 | Group 6 |

| 13-17 | Available | Available | Available | Group 6 | Group 6 |

| Week 45 | 6/11 | 7/11 | 8/11 | 9/11 | 10/11 |

| 8-12 | Group 6 | Available | Available | Available | Group 3 |

| 13-17 | Group 6 | Available | Available | Available | Group 3 |

| Week 46 | 13/11 | 14/11 | 15/11 | 16/11 | 17/11 |

| 8-12 | Group 3 | Available | Available | DAC | Available |

| 13-17 | Group 3 | Available | Available | DAC | Available |

| Week 47 | 20/11 | 21/11 | 22/11 | 23/11 | 24/11 |

| 8-12 | DAC | Available | Group 1 | Group 4 | Available |

| 13-17 | DAC | Available | Group 1 | Group 4 | Available |

| Week 48 | 27/11 | 28/11 | 29/11 | 30/11 | 1/12 |

| 8-12 | Group 4 | Group 1 | Available | Available | Available |

| 13-17 | Group 4 | Group 1 | Available | Available | Available |

Page responsible: Martin Nielsen-Lönn

Last updated: 2017-10-30

LiU startsida

LiU startsida