### Agenda

- Practical issues

- Design process

- FPGA vs ASIC

- Code style

<page-header>

2023 3

Contraction of Digital Systems, Lecture 9

Contraction 2023 3

Contracti

TSTE12 Design of Digital Systems, Lecture 9

2024-09-23 4

### TSTE12 Deadlines MELE, erasmus

- Design sketch, project plan, time plan

- What building blocks in the design (design sketch)

- Who and when should these be implemented (project plan, time plan)

- Wednesday 25 September 21.00: Lab 2 soft deadline

- Lab 2 results will be checked after project completed

2024-09-23 5

# Handin (homework), Individual!

- 1<sup>st</sup> handin deadline today Monday 23 September 23:30

- Use only plan text editor (emacs, vi, modelsim or similar) for code entry.

- Solve tasks INDIVIDUALLY

- Submit answers using Lisam assignment function

- 4 different submissions for code, one for each code task

- 1 submission for all theory question answers

- Use a special terminal window when working with handins

module load TSTE12 ; TSTE12handin

TSTE12 Design of Digital Systems, Lecture 9

#### 2024-09-23 6

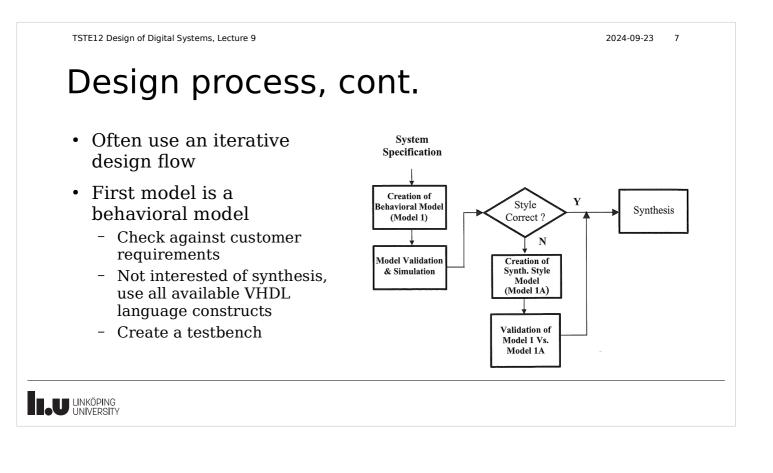

#### Design process

- Best would be to write a direct synthesizable model direct

Hard to do

- First create executable model

- Validate system (check for correct behavior)

- Use complex data types, real values

- Not synthesizable, may use full power of the VHDL language

#### 2024-09-23 8

### Design process, cont.

- Model 1A (after modification to match expected code style)

- Synthesizable

- Fixed point number systems

- Limited memory size

- Difference in behavior

- Noise like errors in signal processing systems

- Timing differences

- Need to know the effect of these errors on the overall behavior

- Need to know what can be and not be done in the model, i.e., application area knowledge is needed, not only implementation in general (Karnough maps, VHDL etc.)

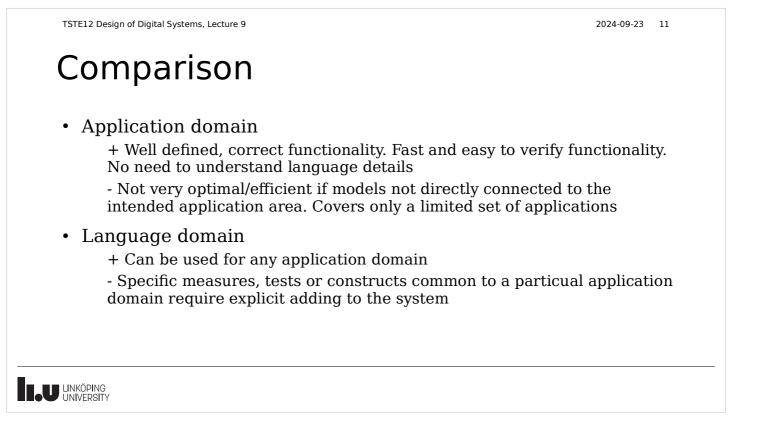

| pplication Specific vs                                                                        | Lunguage                            |

|-----------------------------------------------------------------------------------------------|-------------------------------------|

| Application specific                                                                          |                                     |

| - Use description formats common in the application                                           | domain                              |

| - Models often simulated and/or translated to other of                                        | computer languages                  |

| - Example representations                                                                     |                                     |

| • Dataflow diagram, e.g., DSP                                                                 |                                     |

| - Tools                                                                                       |                                     |

| • SPW, Simulink (Matlab), DSP station, DSP builder                                            |                                     |

| - Only suitable for the application domain                                                    |                                     |

| <ul> <li>Demonstrate working algorithm in simulation</li> </ul>                               |                                     |

| <ul> <li>Often supports statistical calculations to evaluate p<br/>wordlength etc.</li> </ul> | erformance reduction due to limited |

| Describe operations and how they communicate                                                  | ite                                 |

| - Not every block corresponds to a hardware block, o                                          | only describes a function           |

2024-09-23 10

### Language-Domain modeling

- Models described in a computer language instead of graphical entry

- System-C, VHDL, Verilog, C++, Java

- Hierarchy important to reduce complexity of the description

- Application specific information must be added by the designer - No/little help with application specific functions

- Support any application domain

2024-09-23 12

# Synthesis and simulation

- Synthesis style is tools dependent

- Something working in one tool may not work in another tool!

- Continuous development, new features added in each new release

- A standard also exist specifying a common set of expected synthesis constructs

- Lower limit of features, tools may support other/additional language features

- Wordlength and data types: Real -> Integer -> bitvectors

- Real values must first be translated into integer computations

- Integer computations must be translated into bitvectors of limited length

#### 2024-09-23 13

# ASIC design flow (standard cell)

- Behavoural model development

- Behavoural model validation

- testbench design

- Logic synthesis

- Post synthesis simulation

gate delay, no wire delay alternatively only a coarse wire delay estimation

- System partitioning

- divide into chips or large blocks on chip

- I/O is limiting chip size and data speed

TSTE12 Design of Digital Systems, Lecture 9

2024-09-23 14

# ASIC design flow, cont.

- Floor planning

- where to put modules/subsystems on chip

- Placement

- detailed description on where each cell is placed on the chip

- Routing

- connect cells with wires

- Clock tree, power routing

- Circuit extraction

- extract more detailed timing from circuit

#### 2024-09-23 15

### ASIC design flow, cont.

- Post layout simulation

- including wire capacitance, cross talk etc.

- Verify function for all combinations of manufacturer and environment tolerances (fast, slow, typical transistor speed, high/low voltage, high/low temperature, etc.)

- Send masks to manufacturer

- One or more masks for each type of layer on the chip (doping, metal, etc.)

- Turn around time at least 4 weeks, probably 1-3 month

- Evaluate recieved circuit

TSTE12 Design of Digital Systems, Lecture 9

### FPGA design flow

- Behavoural model development

- Behavoural model validation (testbench)

- Logic synthesis

- Slightly different goal structure (lookup tables and flipflops) for FPGA

- Mapping to CLBs

- What logic and flipflop to combine into one unit

- Placement

- Select one of a large set of

- Routing

- Select wire segment in space between CLBs for connecting them together

- Circuit level extraction

- Post layout simulation

- Generation of a POF/SOF/BIT file

2024-09-23 17

# Design manager design flow (Xilinx)

- Translate: Convert to local database format. Some mapping into technology dependent mappings (e.g., memories).

- Map: Allocate CLB, IOB, etc.

- Place & route: Place and route, timing limitations may be included.

- Timing: Extract timing. Performed through static timing analysis (Sum contributing delays from flip-flop outputs to flip-flop inputs).

- Configure: Translate layout information into a POF/SOF (bit) file to program the FPGA. May be stored in ROM or load through a processor/PC.

TSTE12 Design of Digital Systems, Lecture 9

2024-09-23 18

# Synthesis design flow Precision logic

- Analyse

- Parse HDL

- Find libraries and cells

- Check dependencies

- Resolve generics

- Elaborate

- Translate into a generic RTL + black box operators

- Create hierarchy, infer flipflops & latches, memory, operators, FSM

- Pre-optimization

- Boundary optimization

- propagating constants, remove unused outputs, shared input signals

- Constant propagation

- Resource sharing

2024-09-23 19

#### TSTE12 Design of Digital Systems, Lecture 9 Synthesis design flow Precision logic, cont.

- Operator implementation - Adders, counters etc.

- Hierarchy manipulations

- Flatten

- Tristate handling

- DRC checking (Design Rule Checking) - Short circuits, multiple output driving one node etc.

- Technology mapping

- Register retiming

TSTE12 Design of Digital Systems, Lecture 9

2024-09-23 20

# Control of the synthesis process

- Additional information required by synthesis

- Pin assignment

- Timing requirements

- General placement information

- Precompiled netlists

- VHDL attributes

- No standard yet

- Synthesis tool control scripts

- Tools dependent

- Optimization, hierarchy

2024-09-23 21

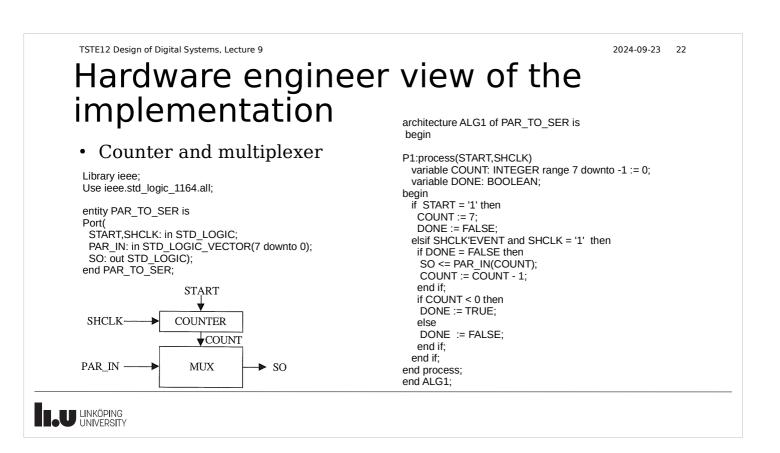

# Syntheis example

- Parallel to serial converter

- Shift out parallel input data from PAR\_IN onto SO once START = '1'

- Lower abstraction level, bit datatypes

Library ieee; Use ieee.std\_logic\_1164.all;

entity PAR\_TO\_SER is Port( START,SHCLK: in STD\_LOGIC; PAR\_IN: in STD\_LOGIC\_VECTOR(7 downto 0); SO: out STD\_LOGIC); end PAR\_TO\_SER;

LINKÖPING UNIVERSITY

2024-09-23 23

### **Programmer implementation**

- Uses waveform assignment with delay information

- Same behavior, less obvious how to implement

Library IEEE; use IEEE.std\_logic\_1164.all;

entity PAR\_TO\_SER\_SCHED is generic(PERIOD: TIME); Port( START: in STD\_LOGIC; PAR\_IN: in STD\_LOGIC\_VECTOR(7 downto 0); SO: out STD\_LOGIC); end PAR\_TO\_SER\_SCHED;

LINKÖPING UNIVERSITY

```

architecture ALG2 of PAR_TO_SER_SCHED is

begin

P1:process(START)

variable COUNT: INTEGER;

begin

if START = '1' then

COUNT := 7;

while COUNT >= 0 loop

SO <= transport PAR_IN(COUNT)

after (7-COUNT)*PERIOD;

COUNT := COUNT - 1;

end loop;

end if;

end process;

end ALG2;

```

TSTE12 Design of Digital Systems, Lecture 9

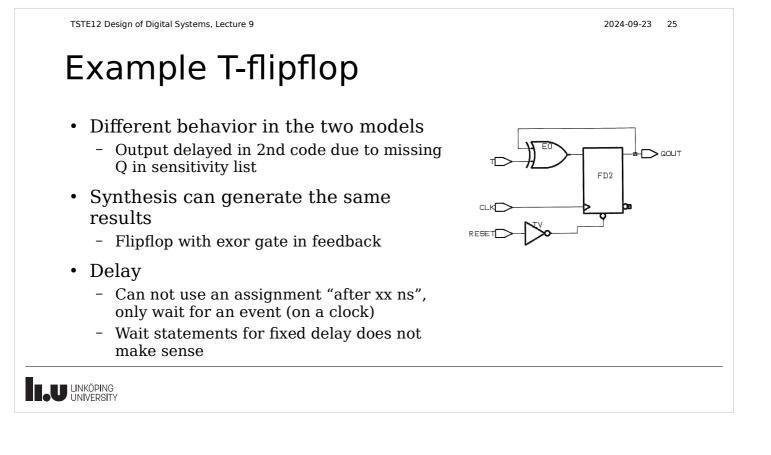

### Sensitivity list issues

- Used in simulation to trigger processes

- In synthesis it only indicates inputs, often without affecting the synthesis

- Example:

- Different simulation

- Same synthesis result

architecture ALG of T\_FF is signal Q: STD\_LOGIC; begin process(RESET,T,CLK) begin if (RESET = '1') then Q <= '0'; elsif (CLK'EVENT and CLK = '1') then if T = '1' then Q <= not Q; end if; end process; QOUT <= Q;</pre>

end ALG;

architecture ALG of T\_FF2 is signal Q: STD\_LOGIC; begin

process(RESET,T,CLK) begin if (RESET = '1') then  $Q \le 0'$ ; elsif (CLK'EVENT and CLK = '1') then if T = '1' then  $Q \le not Q$ ; end if;  $QOUT \le Q$ ; end process;

2024-09-23 24

end ALG;

2024-09-23 26

TSTE12 Design of Digital Systems, Lecture 9

### Data types

- Std logic is prefered

- Helps finding reset issues and similar

- Bit works, but the synthesized model will use std\_logic

- Testbenches require changes to support run of synthesis netlist

| ge detection                 |

|------------------------------|

| GE<br>I no edge, 0->H edge!) |

|                              |

|                              |

|                              |

| TSTE12 Design of Digital S | Systems, Lecture 9 |

|----------------------------|--------------------|

|----------------------------|--------------------|

# Gated clocks

- Generally not a good idea

- Glitch in control signal may produce glitch on clock!

- Wrong timing on control signal may give errornous trigger

- Clock buffers may introduce large delays

- Less time left for the calculation of the control signal value  $% \left( {{{\boldsymbol{x}}_{i}}} \right)$

- Do not combine clock edge detection with logic in the same expression

if clk'event and clk='1' and enable = '1' then

if clk'event and clk = '1' then if enable = '1' then

2024-09-23 28

- Some hardware supports gated clocks

- Special forms of flipflops

TSTE12 Design of Digital Systems, Lecture 9

#### Reset of internal states entity EODET is Port( I,CLK: in STD LOGIC; TEQDET: inout STD LOGIC :='0'); What to do if no asynchronous reset? end EQDET; - Initial data must be clocked in using a architecture ALG of EQDET is control signal begin process Code example without reset variable EQ,IBK1,IBK2: STD LOGIC; begin Works in simulation due to initialisation wait until (CLK'EVENT and CLK = '1'); of TEQDET if(IBK1 =IBK2) and (IBK2 = I) then EQ := '1'; Simulation of synthesis error due to • else EQ := '0'; initialisation to 'U' end if; TEQDET <= (EQ xor TEQDET); IBK2 := IBK1; IBK1 := I; end process; end ALG;

Using explicit reset architecture ALG of EQDET is begin process(RESET,CLK) Asynchronous reset variable EQ,IBK1,IBK2: STD\_LOGIC; begin if (RESET = '1') then Possible to use synchronous IBK1 := '0'; IBK2 := '0'; reset instead TEQDET <= '0'; elsif (CLK'EVENT and CLK = '1') then if (IBK1 = I) and (IBK1 = IBK2) then EQ := '1'; else entity EQDET is EQ := '0'; Port( end if; RESET,I,CLK: in STD\_LOGIC; TEQDET <= (EQ xor TEQDET); TEQDET: inout STD LOGIC); IBK2 := IBK1; end EQDET; IBK1 := I; end if; end process; end ALG;

```

2024-09-23 30

```

2024-09-23 31

# Simulation and Synthesis results

- Order of IBK1 and IBK2 updates are important if variables are used

- Update order not important if signals are used

- EQ still a variable!

- Both descriptions give same synthesis result

```

architecture ALG of EQDET is

signal IBK1, IBK2: STD LOGIC;

begin

process(RESET,CLK)

variable EQ: STD_LOGIC;

begin

if (RESET = '1') then

IBK1 <= '0':

IBK2 <= '0';

TEQDET \leq 0';

elsif (CLK'EVENT and CLK = '1') then

if (IBK1 = I) and (IBK1 = IBK2) then

EQ := '1';

else

EQ := '0';

end if;

TEQDET <= (EQ xor TEQDET);

IBK1 <= I;

IBK2 <= IBK1;

end if;

end process;

end ALG:

```

LINKÖPING UNIVERSITY

TSTE12 Design of Digital Systems, Lecture 9

### Arithmetic operations

- Add, sub supported

- Translates into full adder before simplified

- Operands are not extended

- Multiplication

- Translated into combinational expressions

- Multiple possible structures: Wallace, Carry Save array.

- Constant values usually produces add and shift implementations (simplified multiplications)

- Division usually not supported

```

2024-09-23 33

```

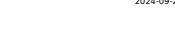

#### TSTE12 Design of Digital Systems, Lecture 9 Hierarchical arithmetic: BCD to binary conversion

- Want to implement a 4 digit BCD to binary converter - describe decimal number using 4 bits for each digit

- Use Horners rule:  $d_3x10^3 + d_2x10^2 + d_1x10 + d_0 = (d_3x10+d_2)x10+d_1)x10+d_0$ , i.e., by arbitrary length converter can be built by repeated multiplication by 10 and addition

- Implement the multiply add

```

TSTE12 Design of Digital Systems, Lecture 9

2024-09-23 34

Multiply and add operators

ibrary IEEE:

use IEEE.STD LOGIC 1164.all;

use IEEE.NUMERIC_STD.all;

entity SIMP_ADD is _____

port(A,B: in STD_LOGIC_VECTOR(3 downto 0);

Use unsigned datatype

CIN: in STD_LOGIC;

library IEEE

C: out STD_LOGIC_VECTOR(3 downto 0);

use IEEE.STD LOGIC 1164.all:

CAR_OUT: out STD_LOGIC);

use IEEE.NUMERIC_STD.all;

end SIMP ADD;

architecture ALG of SIMP ADD is

entity MULT10 is

port(DATA IN: in STD LOGIC VECTOR(3 downto 0);

begin

P1:process(A,B,CIN)

PRODUCT: out STD LOGIC VECTOR(7 downto 0));

variable PADDED_CIN: STD_LOGIC_VECTOR(3 downto 0);

end MULT10;

variable A_UNSIGNED: UNSIGNED(3 downto 0);

variable C UNSIGNED: UNSIGNED(4 downto 0);

architecture ALG of MULT10 is

begin

beain

A UNSIGNED := UNSIGNED(A);

process(DATA_IN)

variable PROD_ÚS: UNSIGNED(7 downto 0);

PADDED_CIN :="000"&CIN;

C_UNSIGNED := (A_UNSIGNED(3) & A_UNSIGNED,5) +

begin

UNSIGNED(B) + UNSIGNED(PADDED_CIN);

PROD US :=

C <= STD_LOGIC_VECTOR(C_UNSIGNED(3 downto 0));

UNSIGNED(DATA_IN)*10;

CAR OUT \leq C UNSIGNED(4);

PRODUCT <= STD LOGIC VECTOR(PROD US);

end process;

end process;

end ALG:

end ALG;

U LINKÖPING

UNIVERSITY

```

2024-09-23 35

# Combined add and mult

Varying word length library IEEE; use IEEE.STD\_LOGIC\_1164.all; use IEEE.NUMERIC\_STD.all; entity MADD is generic(IN WIDTH: NATURAL := 4); port(DI: in STD\_LOGIC\_VECTOR(IN\_WIDTH-1 downto 0); DJ: in STD\_LOGIC\_VECTOR(3 downto 0); MSUM: out STD\_LOGIC\_VECTOR(IN\_WIDTH+3 downto 0)); end MADD; architecture ALG of MADD is begin P1: process(DI,DJ) variable MSUM\_US: UNSIGNED(IN\_WIDTH+3 downto 0); variable PROD:UNSIGNED(2\*IN\_WIDTH-1 downto 0); begin PROD := UNSIGNED(DI)\*to\_unsigned(10,IN\_WIDTH); MSUM\_US := PROD(IN\_WIDTH+3 downto 0)+ UNSIGNED(DJ); MSUM <= STD\_LOGIC\_VECTOR(MSUM\_US); end process; end ALG:

library IEEE use IEEE.STD\_LOGIC\_1164.all; entity BCDCONV is port(D0,D1,D2,D3: in STD\_LOGIC\_VECTOR(3 downto 0); BIN\_OUT: out STD\_LOGIC\_VECTOR(15 downto 0)); end BCDCONV: architecture STRUCTURAL of BCDCONV is component MADD generic(IN\_WIDTH: NATURAL := 4); port(DI: In STD\_LOGIC\_VECTOR(IN\_WIDTH-1 downto 0); DJ: in STD\_LOGIC\_VECTOR(3 downto 0); MSUM: out STD\_LOGIC\_VECTOR(IN\_WIDTH+3 downto 0)); end component; signal MSUM2: STD\_LOGIC\_VECTOR(7 downto 0); signal MSUM1: STD\_LOGIC\_VECTOR(11 downto 0); begin C1: MADD generic map(4) port map(D3,D2,MSUM2); C2: MADD generic map(8) port map(MSUM2,D1,MSUM1); C3: MADD generic map(12) port map(MSUM1,D0,BIN\_OUT); end STRUCTURAL;

TSTE12 Design of Digital Systems, Lecture 9

2024-09-23 36

### Hierarchical circuit synthesis

- Ungrouping

- remove artificial boarders between blocks

- Allows optimize common subcalculation

- Improves synthesis results

- Example BCD: 342 -> 309 cells and 30.34 -> 30.11 ns delay.

#### • Uniquify

- Create different instances different implementations by repeating netlists

- Allows different optimization of different parts

| <ul> <li>Bottom up <ul> <li>uniquify</li> <li>Build each sub block, then combine</li> <li>Requires good estimate of timing requirement</li> </ul> </li> </ul> |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>Top down <ul> <li>Synthesize all to get initial requirements</li> <li>Resynthesize parts not meeting requirements</li> </ul> </li> </ul>             |  |

| <ul> <li>Golden instance</li> <li>Synthesize one block, reuse</li> </ul>                                                                                      |  |

| TSTE12 Design of Digital Systems, Lecture 9 |

|---------------------------------------------|

|---------------------------------------------|

#### 2024-09-23 38

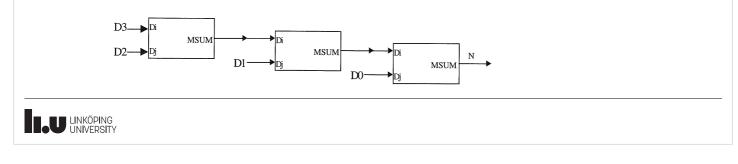

# Example: 12 bit adder register

- Design based on the 4-bit adder

- Different requirement on sum and carry speed

TSTE12 Design of Digital Systems, Lecture 9

2024-09-23 40

### Inferred latches and don't cares

- Synthesis may find that latches are needed

- Example: incomplete if

PROCESS(a,b,c,d)

BEGIN

IF (a = '1') THEN

out\_sig <= x;

ELSIF (b = '1') THEN

out\_sig <= y;

ENDIF;

END PROCESS;</pre>

out\_sig not defined if a and b = 0! Require latch!

2024-09-23 41

#### Latch and undefined examples (SEL=11 not expected)

entity INFERRED is

Dort(IN\_DAT,IN\_EN: in STD\_LOGIC; SEL: in STD\_LOGIC\_VECTOR(1 downto 0); A\_LATCHED,A\_COMB,B\_LATCHED,B\_COMB\_0,B\_COMB\_1,B\_COMB\_2: out STD\_LOGIC); --pragma dc\_script\_begin P B LATCHED: process(IN DAT,SEL) --set\_flatten true begin --pragma dc\_script\_end case (SEL) is when "00" => B\_LATCHED <= IN\_DAT; end INFERRED: when "01" => B\_LATCHED <= not architecture ALG of INFERRED is IN\_DAT; when "10" => B\_LATCHED <= '0'; begin when "11" => null; P\_A\_LATCHED: process(IN\_DAT,IN\_EN) when others => null; begin if IN\_EN = '1' then end case: A LATCHED <= IN DAT; end process end if; P\_B\_COMB\_0: process(IN\_DAT,SEL) end process; P\_A\_COMB: process(IN\_DAT,IN\_EN) begin case (SEL) is when "00" => B\_COMB\_0 <= IN\_DAT; when "01" => B\_COMB\_0 <= not IN\_DAT; when "10" => B\_COMB\_0 <= not IN\_DAT; when "10" => B\_COMB\_0 <= '0'; when "11" => B\_COMB\_0 <= '1'; begin if IN\_EN = '1' then A\_COMB <= IN\_DAT; else A\_COMB <= '0'; when others => null; end if: end case; end process; end process;

P\_B\_COMB\_1: process(IN\_DAT,SEL) begin B COMB 1 <= '1'; case (SEL) is when "00" => B\_COMB\_1 <= IN\_DAT; when "01" => B\_COMB\_1 <= not IN\_DAT; when "10" => B\_COMB\_1 <= not IN\_DAT; when "10" => B\_COMB\_1 <= '0'; when "11" => null; when others => null; end case; end process; P\_B\_COMB\_2: process(IN\_DAT,SEL) beain case (SEL) is when "00" => B\_COMB\_2 <= IN\_DAT; when "01" => B\_COMB\_2 <= not IN\_DAT; when "10" => B\_COMB\_2 <= 10'; when "11" => B\_COMB\_2 <= '-'; when others => null; end case; end process; end ALG;

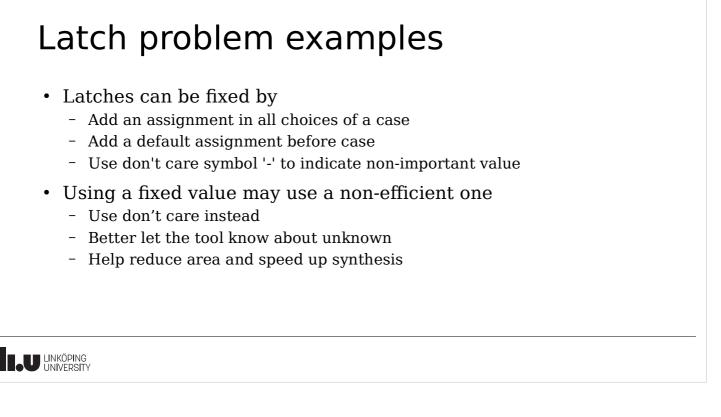

TSTE12 Design of Digital Systems, Lecture 9 2024-09-23 42 Synthesis results Synthesis sometimes generate latches A\_COMB IN\_DAT -A\_LATCHED IN EN à B\_COMB\_2  $\sim$  $\sim$ SEI **B** LATCHED B\_COMB\_0 B\_COMB\_1 tB

| DOM structure                                                                                                                                                                                                                                                                                                                     | with don't care        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| ROM-Structure                                                                                                                                                                                                                                                                                                                     | with don't care        |

| library IEEE;<br>use IEEE.std_logic_1164.all;<br>use IEEE.std_logic_unsigned.all;<br>entity FUNCS is<br>port(X: in STD_LOGIC_VECTOR(2 downto 0); 2<br>end FUNCS;                                                                                                                                                                  | Z1,Z2: out STD_LOGIC); |

| architecture ROM of FUNCS is<br>type ROM_1D is array(0 to 7) of STD_LOGIC;<br>begin<br>FULLY_SPECIFIED: process(X)<br>constant ROM1: ROM_1D:= "01101000";<br>begin<br>Z1 <=ROM1(CONV_INTEGER(X));<br>end process;<br>PARTIALLY_SPECIFIED: process(X)<br>constant ROM2: ROM_1D:= "011010";<br>begin<br>Z2 <=ROM2(CONV_INTEGER(X)); |                        |

TSTE12 Design of Digital Systems, Lecture 9 2024-09-23 46 Tristate gates Some technologies does not support tristate internally in library IEEE; PROCB: process(B,ENB) begin if (ENB = '1') then BUS\_SIG <= B; use IEEE.STD\_LOGIC\_1164.all; entity TRISTATE is the design port(A,B,ENA,ENB: in STD LOGIC; else BUS\_SIG <= 'Z'; BUS\_SIG: out STD\_LOGIC); end TRISTATE: Floating wires may produce end if; architecture ALG of TRISTATE is end process; high power consumption due begin PROCA: process(A,ENA) end ALG: to short circuit current in begin if (ENA = '1') then BUS\_SIG <= A; inputs ENB else BUS\_SIG <= 'Z'; BUS\_SIG Possible to change a tristate • end if: end process; version into a multiplexer based version (done automatically by some tools)

2024-09-23 47

# Clock buffers and other aspects

- Attributes used to indicate clock signals

- Information used to select special layout methods or hardware resources to reduce clock skew

- Automatically detected in general

- High fanout signals

- Buffer cells will be added

- Logic duplications

- Allow larger fan-out without adding separate buffers

- Retiming/pipelining

Switch order between calculation and storage

- Multipliers/DSP blocks

TSTE12 Design of Digital Systems, Lecture 9

2024-09-23 48

### **Resource sharing**

- · Chose one of two sums. May add both or chose inputs first

- Mux+add => 51 area, 8.47 delay

- Add+mux => 73 area, 7.09 delay

- Flattening and structure. (logic level, not hierarchy)

- Logic can be flattened to e.g., two levels instead of three. Different results of area and logic

2024-09-23 49

# How is timing requirements defined?

- Often derived from a symbolic clock

- Signals are defined from edges of the clock

- Fix setup and hold time. Include clock skew

- Usually defined as maximum delay

- Expensive to guarantee minimum delay

- Delay pin to flipflop, flipflop to pin

- Time from flipflop to flipflop

- Possible to specify multi cycle delay

- False paths

LINKÖPING UNIVERSITY

TSTE12 Design of Digital Systems, Lecture 9

### Results

- Time reports

- Generated by analysis of netlist/layout

- Critical path reports

- Area reports

- Resource reports

- Routing, flipflops, LUT, multipliers etc.

- VHDL simulation models

- Post synthesis, post layout

- Layout possible to modify (edit at bit level)

Synthesis is based on different types of pattern matching

Support most constructs

Behavour may still be different

Often adds complicated patterns that are then simplified

Example: D flip flop with Qinvers output, but without Q in the sensitivity list. Generally generates a single flipflop, but timing of Qinvers differs between simulation of VHDL and synthesized design.

TSTE12 Design of Digital Systems, Lecture 9

TSTE12 Design of Digital Systems, Lecture 9

2024-09-23 52

2024-09-23 51

### **Recommended patterns**

- Style guide exists (patterns)

- Specific to the synthesis tools

- Specify patterns that are allowed and recommended

- Important to produce efficient implementations

- Example units: counters, memories, tristate buffers

- These manuals are available online