### Agenda

- Practical issues

- Hardware description

- FPGA

- HDL based design

2023-09-14 3

### TSTE12 Deadlines Y,D,ED

- Final version of design sketch and project plan this week

- Show implementation ideas, show sequence of implementation and task partitioning between group members

- Weekly meetings should start

- Internal weekly meeting with transcript sent to supervisor

- Lab 2 results will be checked after the project ends

TSTE12 Design of Digital Systems, Lecture 8

2023-09-14 4

### TSTE12 Deadlines MELE, erasmus

- Final requirement specification this week

- Wednesday 20 September 21.00: Lab 2 soft deadline

- Lab 2 results will be checked after project completed

2023-09-14 5

2023-09-14

6

# Handin (homework), Individual!

- 1<sup>st</sup> handin deadline Monday 18 September 23:30

- Use only plan text editor (emacs, vi, modelsim or similar) for code entry.

- Solve tasks INDIVIDUALLY

- Submit answers using Lisam assignment function

- 4 different submissions for code, one for each code task

- 1 submission for all theory question answers

- Use a special terminal window when working with handins

module load TSTE12 ; TSTE12handin

TSTE12 Design of Digital Systems, Lecture 8

#### Hardware overview

- Detailed description of Hardware

- Standard parts

- TTL (SSI, MSI LSI)

- Memories, microprocessors, I/O

- ASIC (Application Specific Integrated Circuit)

- Integrated circuit that has been produced for a specific application and (often) produced in small numbers

- Memories and microprocessors are general application devices

2023-09-14 7

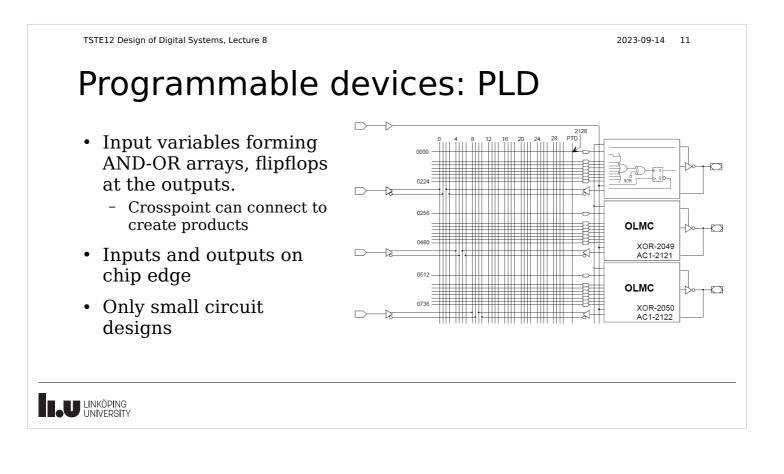

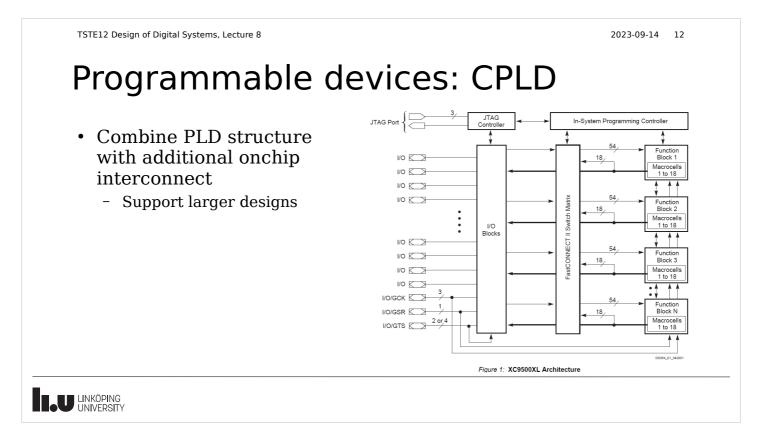

# ASIC technologies

- May use different technologies for ASIC: PLD, Gate array, FPGA, Standard cell, custom. ASIC is however limited to Standard cell and gate array. Custom design is also used.

- CMOS switch. Power consumption:  $P \thicksim CV^2 f$

- Use low power supply, reduce clock, reduce area

- Transistor channel length (old measure of chip manufacturing process) shorter than 0.01 um (so called 5 nm used today, e.g. TSMC N5 process in Ryzen 7000 series CPUs, 4 nm in Apple A16 Bionic in Iphone 14)

| TSTE12 Design of Digital Systems, Lecture 8                                                                                                                                                                                                                                                                                | 2023-09-14 8 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Gate array, mask pr                                                                                                                                                                                                                                                                                                        | ogrammable   |

| <ul> <li>Predefined pattern of transistors <ul> <li>Add interconnect metal for each design</li> <li>Fast manufacture (weeks)</li> <li>No transistor sizing</li> </ul> </li> <li>Example shows inverter design</li> <li>Combined with library of existing cells <ul> <li>Basic gates, flipflops etc.</li> </ul> </li> </ul> | Poly Gates   |

|                                                                                                                                                                                                                                                                                                                            |              |

| TSTE12 Design of Digital Systems, Lecture 8<br>Standard cell                                                           | 2023-09-14 9                                                 |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| <ul> <li>Transistor placement and<br/>metal layers unique for<br/>each design, needs to be<br/>manufactured</li> </ul> | to power metal connection to power pads pads vss VDD VSS VDD |

| • Limited number of layout cell types (Cell library)                                                                   | feedthrough cell A.11                                        |

| <ul> <li>Cells already<br/>characterized</li> </ul>                                                                    | cell A.14 cell A.23 cell A.132 metal2 spacer cells           |

| <ul> <li>Slow manufacture<br/>(month)</li> </ul>                                                                       | metal2 11 power cell metal1                                  |

2023-09-14 10

TSTE12 Design of Digital Systems, Lecture 8

#### Full custom layout

- Full custom

- Individual placement and scaling of transistors

- Full control of wires and connections

- Maximum control, maximum effort

- Complete freedom to place and route transistors

- Not limited to existing logic style/library

- Slow manufacture (months)

- Higher performance than standard cells

- Requires more testing (simulation)

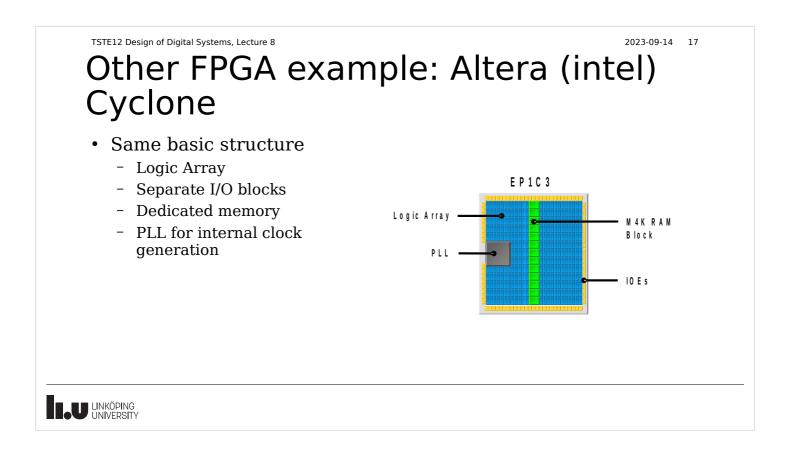

| FPGA structure                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Field Programmable Gate<br/>Array</li> <li>Cells in an array, special I/O<br/>blocks around the edges.</li> <li>Between cells (CLBs or LEs)<br/>are routing wires located<br/>(interconnect)</li> </ul> | BLOCK RAM<br>BLOCK |

|                                                                                                                                                                                                                  | / 0200000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LINKÖPING<br>UNIVERSITY                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

TSTE12 Design of Digital Systems, Lecture 8

#### 2023-09-14 14

2023-09-14 13

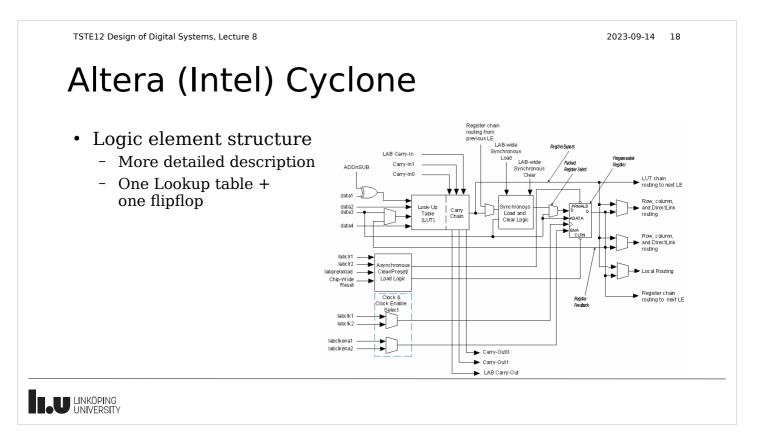

# FPGA building blocks

- CLB/Logic Element

- Different name in different manufacturers designs

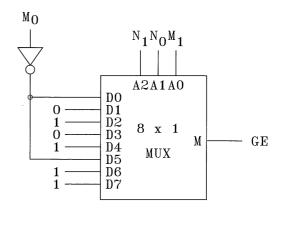

- In many cases are they based on lookup tables (i.e., no simple gates, instead more advanced functions) => less need for routing channels (that are expensive). Lookup table can be viewed as a small RAM or a MUX with fixed inputs.

- Trade off between big lookup tables and utilization. Optimal around 4-6 bits address.

- Often a flip-flop included in the CLB/LE

2023-09-14 15

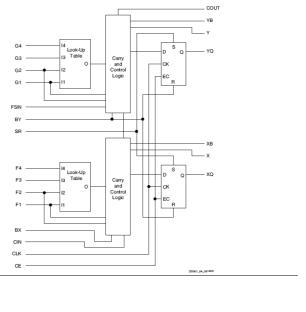

# CLB Example: Xilinx (AMD) Spartan II

- Choose positive or negative clock edge

- May combine lookup tables

- CLB may be rearranged into a memory or shift register

2023-09-14

16

TSTE12 Design of Digital Systems, Lecture 8

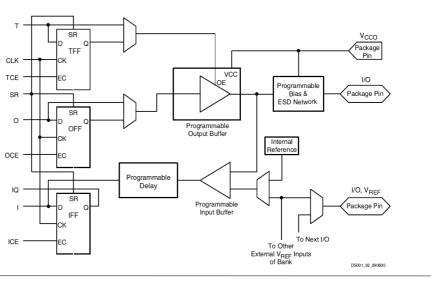

# Xilinx Spartan II I/O logic

- Support multiple I/O standards

- 3.3V, 1.8V, 1.2V etc.

- Differential

- Flipflops located close to pin

- Reduce delays due to routing signal to pin

- Different drive strength

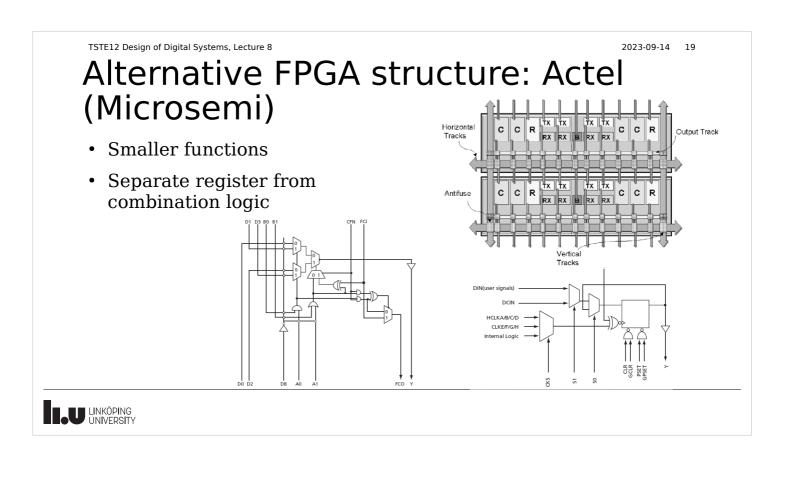

# Programming of FPGA

- Two types: reprogrammable or one-time programmable

- Control a CMOS-switch using a RAM/EPROM/EEPROM-cell. The CMOS switch is slow (compared to the alternative)

- The alternative is fuse/Antifuse (burn together two wires by using high voltage)

2023-09-14

#### 2023-09-14 21

#### Important aspects

- Speed of the switched (impedance, capacitans). Many switches in series ruins the performance

- Reprogrammable? Needs any design changes to be done?

- Volatile designs? What happens at power failure? How is the design put into the chip? How long delay from power on to working design?

- Area of the switches? Needs many switches?

TSTE12 Design of Digital Systems, Lecture 8

#### 2023-09-14 22

no

yes

large

large

average

Antifuse EPROM EEPROM/FLASH

no

yes

small

large

large

# Technology comparison table

Re-programmable

R (routing nets)

Volatile

С

Chip area

- Most common

- SRAM

- EEPROM/FLASH

- Xilinx/Altera

- SRAM/EEPROM

- Actel

- Antifuse

- Do also create classic FPGA (SRAM/EEPROM based)

- SRAM based FPGA usually support automatic configuration from serial flash memory at power-on

SRAM

yes

yes

large

large

large

no

no

small

small

small

2023-09-14 23

# How to configure the FPGA

- Non-volatile technology

- FLASH, EEPROM, PROM, etc.

- External programmer

- Software on PC to program device

- External ROM/FLASH

- Standard FLASH

- Serial FLASH

- Embedded microcontroller

- Boot application configures FPGA

- Not possible if flash needed for CPU operation

TSTE12 Design of Digital Systems, Lecture 8

2023-09-14 24

### FPGA configuration, cont.

- Large volumes may use non-programmable devices based on FPGA

- Resynthesize: may give different behavior

- Strip FPGA: Remove configuration logic

<section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item>

TSTE12 Design of Digital Systems, Lecture 8

TSTE12 Design of Digital Systems, Lecture 8

#### 2023-09-14 26

#### FPGA hardware options, cont.

- Clock circuits

- Phase locked loops (PLL), Delay locked loops (DLL)

- Clock tree distribution

- Serializer/deserializer

- Support modern PC bus standards such as PCI Express

- Dedicated block to send/recieve high speed (> Gbit/s) serial data

- Reduce number of I/O pins

2023-09-14 27

2023-09-14 28

# FPGA hardware options, cont.

- A/D and D/A converters

- Memory units

- CPU

- e.g., physical powerpc or ARM core inside FPGA

- Usually combined with external memory interfaces and CPU-based I/O support (e.g. wired ethernet, SD-card reader etc.)

- Alternative to dedicated CPU hardware: soft cpu

- VHDL design of a processor

- Allows for modification of processor structure

TSTE12 Design of Digital Systems, Lecture 8

### ASIC vs FPGA

- ASIC have a large NRE cost

- Non-Recurring Engineering cost, price of 1st unit

- FPGA have large per unit cost

- Selection of technology depend on

- Performance requirements

- Number of units

- Time to market

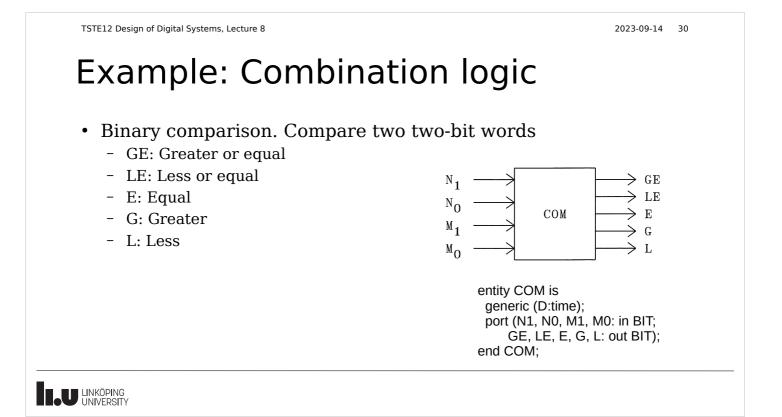

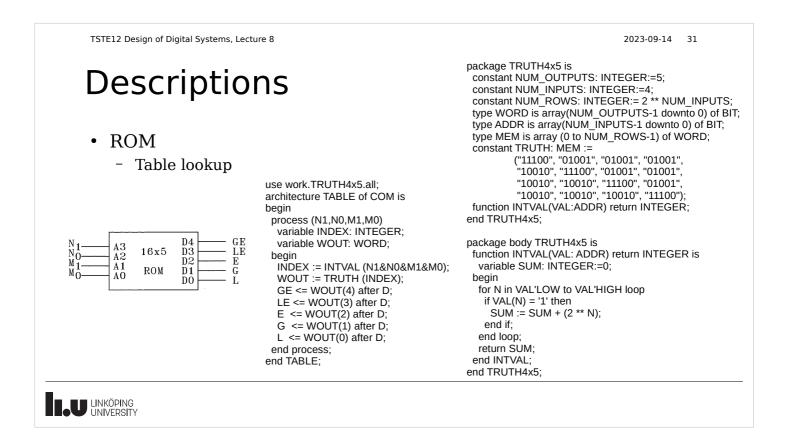

# HDL based design

- Structured design using HDL

- FSM descriptions

| TSTE12 Design of Digital Systems, Lecture                                                        | e 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2023-09-14 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Descriptior                                                                                      | ns, CASE statem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| • One multiplexer<br>for each output<br>$ \begin{array}{c}                                     $ | $ \begin{array}{l} E <= '0' \mbox{ after D; } G <= '1' \mbox{ after D; } L <= '0' \mbox{ after D; } when "0101" => GE <= '1' \mbox{ after D; } LE <= '1' \mbox{ after D; } E <= '1' \mbox{ after D; } G <= '0' \mbox{ after D; } L <= '0' \mbox{ after D; } When "0110" => GE <= '0' \mbox{ after D; } LE <= '1' \mbox{ after D; } E <= '0' \mbox{ after D; } G <= '0' \mbox{ after D; } LE <= '1' \mbox{ after D; } GE <= '0' \mbox{ after D; } LE <= '1' \mbox{ after D; } H <= '0' \mbox{ after D; } GE <= '0' \mbox{ after D; } LE <= '1' \mbox{ after D; } H <= '1' \mbox{ after D; } H <= '0' \mbox{ after D; } H <= '1' \$ | when "1000" => GE <= '1' after D; LE <= '0' after D;<br>E <= '0' after D; G <= '1' after D; L <= '0' after D;<br>When "1001" => GE <= '1' after D; L <= '0' after D;<br>E <= '0' after D; G <= '1' after D; L <= '0' after D;<br>When "1010" => GE <= '1' after D; LE <= '1' after D;<br>E <= '1' after D; G <= '0' after D; L <= '0' after D;<br>When "1011" => GE <= '0' after D; L <= '1' after D;<br>E <= '0' after D; G <= '0' after D; L <= '1' after D;<br>E <= '0' after D; G <= '0' after D; L <= '0' after D;<br>When "1100" => GE <= '1' after D; L <= '0' after D;<br>When "1100" => GE <= '1' after D; L <= '0' after D;<br>When "1100" => GE <= '1' after D; L <= '0' after D;<br>When "1101" => GE <= '1' after D; L <= '0' after D;<br>When "1110" => GE <= '1' after D; L <= '0' after D;<br>E <= '0' after D; G <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '0' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D;<br>When "1111" => GE <= '1' after D; L <= '0' after D; E <= '1' |

| Descriptions, improved                                                                                                | architecture MUX3 of COM is                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Remove one variable in the selection of the case statement</li> </ul>                                        | begin<br>process (N1, N0, M1, M0)<br>begin<br>case N1&N0&M1 is<br>when "000" => GE <= not M0 after D; LE <= '1' after D<br>E <= not M0 after D; G <= '0' after D; L <= M0 after D;<br>when "001" => GE <= '0' after D; LE <= '1' after D;<br>E <= '0' after D; G <= '0' after D; L <= '1' after D;                                                            |

| <ul> <li>Use the removed variable<br/>as output value or its<br/>inverse</li> </ul>                                   | when "010" => GE <= '1' after D; LE <= M0 after D;<br>E <= M0 after D; G <= not M0 after D; L <= '0' after D<br>when "011" => GE <= '0' after D; LE <= '1' after D;<br>E <= '0' after D; G <= '0' after D; L <= '1' after D;<br>when "100" => GE <= '1' after D; LE <= '0' after D;<br>E <= '0' after D; G <= '1' after D; L <= '0' after D;                  |

| <ul> <li>More variables can be<br/>removed <ul> <li>Increase logic in front of<br/>multiplexer</li> </ul> </li> </ul> | when "101" => GE <= not M0 after D; LE <= '1' after D<br>E <= not M0 after D; G <= '0' after D; L <= M0 after D;<br>when "110" => GE <= '1' after D; LE <= '0' after D;<br>E <= '0' after D; G <= '1' after D; L <= '0' after D;<br>when "111" => GE <= '1' after D; LE <= M0 after D;<br>E <= M0 after D; G <= not M0 after D; L <= '0' after D<br>end case; |

|                                                                                                                       | end process;<br>end MUX3;                                                                                                                                                                                                                                                                                                                                     |

#### 2023-09-14 34

#### Hardware, improved Case statement

- One mux plus inverter

- Every output have its own multiplexer (same as for nonimproved case statement)

| , sharing comi      | ion subexpression   |            |

|---------------------|---------------------|------------|

|                     |                     |            |

| <u>-</u>            |                     |            |

| 2                   |                     |            |

| ions followed b     | y simple generation | n of E, G, |

| ic synthesis ins    | tead of tool        |            |

| till modify descrip | tion                |            |

|                     |                     |            |

| E<br>S              | jic synthesis ins   |            |

TSTE12 Design of Digital Systems, Lecture 8

### **Two-level** logic

- Many different choices

- Can be described as structure

architecture POSDF of COM is signal Z1,Z0: BIT; begin Z1 <= (not N0 or M1 or M0) and (not N1 or M1) and (not N1 or not N0 or MÓ); Z0 <= (N1 or N0 or not M0) and (N1 or not M1) and (N0 or not M1 or not M0);  $LE \stackrel{\sim}{<}= Z1$  after D; GE <= Z0 after D; E <= Z1 and Z0 after D; G <= Z0 and not Z1 after D; L <= Z1 and not Z0 after D; end POSDF;

| Structural description<br>architecture TWO_LEVEL_OR_AND of COM is<br>signal Z10,Z11,Z12,Z00,Z01,Z02: BIT;<br>signal X0BAR,NIBAR,MUBAR,MIBAR: BIT;<br>signal Z0,Z1,Z0NOT,Z1NOT: BIT;<br>component NOT2G<br>generic (D: TIME);<br>port (I: in BIT; O: out BIT);<br>end component;<br>for all: NOT2G use entity NOT2(BEHAVIOR);<br>component AND2G<br>generic (D: TIME);<br>port (I, 12: in BIT; O: out BIT);<br>end component;<br>for all: AND2G use entity AND2(BEHAVIOR);<br>component AND3G<br>generic (D: TIME);<br>port (I, 1,2,13: in BIT; O: out BIT);<br>end component;<br>for all: AND3G use entity AND3(BEHAVIOR);<br>component OR2G<br>generic (D: TIME);<br>port(1, 1,2,13: in BIT; O: out BIT);<br>end component;<br>for all: OR2G use entity OR2(BEHAVIOR);<br>component OR2G<br>generic (D: TIME);<br>port (1, 1,2,13: in BIT; O: out BIT);<br>end component;<br>for all: OR2G use entity OR2(BEHAVIOR);<br>component OR3G<br>generic (D: TIME);<br>port (1, 1, 2, 13: in BIT; O: out BIT);<br>end component;<br>for all: OR3G use entity OR3(BEHAVIOR); | begin<br>C1: NOT2G<br>generic map (2 ns)<br>port map (N0, NOBAR);<br>C2: NOT2G<br>generic map (2 ns)<br>port map (N1, NIBAR);<br>C3: NOT2G<br>generic map (2 ns)<br>port map (M0, MOBAR);<br>C4: NOT2G<br>generic map (2 ns)<br>port map (M1, M1BAR);<br>C5: OR3G<br>generic map (2 ns)<br>port map (NOBAR, M1, M0, Z10);<br>C6: OR2G<br>generic map (2 ns)<br>port map (NIBAR, M1, Z11);<br>C7: OR3G<br>generic map (2 ns)<br>port map (NIBAR, NOBAR, M0, Z12);<br>C8: AND3G<br>generic map (2 ns)<br>port map (M1BAR, NOBAR, M0, Z12);<br>C9: OR3G<br>generic map (2 ns)<br>port map (M1, Z11, Z12, Z1);<br>C9: OR3G<br>generic map (2 ns)<br>port map (M1, N0, MOBAR, Z00); | C10:OR2G<br>generic map (2 ns)<br>port map (N1, M1BAR, Z01);<br>C11:OR3G<br>generic map (2 ns)<br>port map (N0, M1BAR, M0BAR, Z02);<br>C12:AND3G<br>generic map (2 ns)<br>port map (200, Z01, Z02, Z0);<br>C13:NOT2G<br>generic map (2 ns)<br>port map (21, Z1NOT);<br>C14:NOT2G<br>generic map (2 ns)<br>port map (20, Z1, E);<br>C16:AND2G<br>generic map (2 ns)<br>port map (20, Z1, E);<br>C16:AND2G<br>generic map (2 ns)<br>port map (20, Z1NOT, G);<br>C17:AND2G<br>generic map (2 ns)<br>port map (Z1, Z0NOT, L);<br>C18:WIREG<br>port map (Z0, GE);<br>C19: WIREG<br>port map (Z0, GE);<br>C19: WIREG |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSTE12 Design of Digital Systems, Lecture 8                                                                                                                                                                    | 2023-09-14 38 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Finite state machi                                                                                                                                                                                             | nes (FSM)     |

| <ul> <li>Example: serial/parallel conv</li> <li>A indicates start of data</li> <li>Output Z only during one clock</li> </ul>                                                                                   |               |

|                                                                                                                                                                                                                | CLK           |

| $\begin{array}{c c} R & \longrightarrow \\ A & \longrightarrow \\ \end{array} & \qquad \qquad$ | R             |

| $\begin{array}{c c} D & \longrightarrow \\ CLK & \longrightarrow \end{array} \qquad \qquad$    | A             |

| entity STOP is                                                                                                                                                                                                 | D             |

| port (R, A, D, CLK: in BIT;<br>Z: out BIT_VECTOR(3 downto 0);<br>DONE: out BIT);                                                                                                                               | DONE          |

| end STOP;                                                                                                                                                                                                      | Z[4]          |

|                                                                                                                                                                                                                |               |

2023-09-14 39

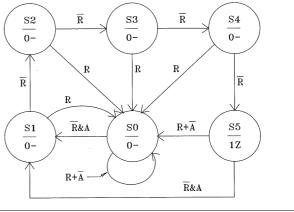

# FSM design, cont.

- First: Select type of state machine (Moore, Mealy)

- Moore machine have stable output after a few gate delays

- Moore machine can not produce output dependent on current input values

- Moore machine may require more states than Mealy machines

- Mealy machine may sometimes be required due to direct respons from FSM on input signal change

TSTE12 Design of Digital Systems, Lecture 8

2023-09-14 40

#### FSM Design, cont.

- Second: Create a state diagram. Good start is reset-state S0.

- S1: First data on D, Done=0, Z unspecified

- S2: Second data on D, Done =0, Z unspecified

- S3: Third data on D, Done = 0, Z unspecified

- S4: Fourth data on D, Done = 0, Z unspecified

- S5: Output on Z, Done= 1

- In S5 can A also be 1 (indicating new data)

- Next clock cycle must take care data, i.e., use S1 without passing through S0

2023-09-14 41

## FSM state diagram

• Some tools can translate state diagram automatically to VHDL (e.g., HDL Designer)

| Alte   | rna      | ate d                      | esri          | ption             |                             |             |  |

|--------|----------|----------------------------|---------------|-------------------|-----------------------------|-------------|--|

| • Tran | sitio    | n list                     |               |                   |                             |             |  |

| - Te   | extual   | descriptio                 | n of the      | FSM               |                             |             |  |

|        |          | or large st                |               |                   |                             |             |  |

|        |          | 0                          | -             |                   | when number of state        | es increase |  |

|        | -        |                            |               |                   | use of hierarchy            | ,o morouso  |  |

| 10     | 1        | t Transition<br>Expression | Next<br>State | Data<br>Transfers | Output                      |             |  |

|        | S0<br>S0 | R+A<br>R & A               | S0<br>S1      | None              | DONE=0, Z unspecified       |             |  |

|        | S1<br>S1 | R                          | S2<br>S0      | Store bit 1       | DONE=0, Z unspecified       |             |  |

|        | :        | :                          | :             | :                 | :                           |             |  |

|        | S5<br>S5 | R & A<br>R + A             | S1            | None              | DONE=1, Z=parallel data out |             |  |

|        |          | R + A                      | S0            |                   |                             |             |  |

2023-09-14 44

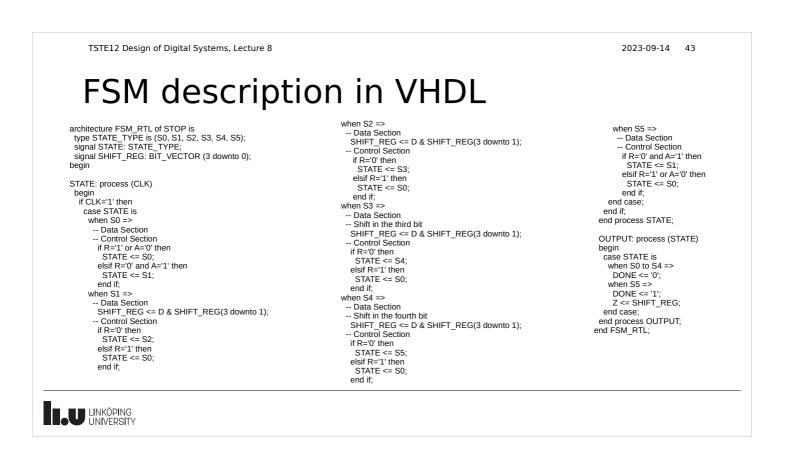

# State machine partitioning

- State machines partitioned into multiple processes

- Updating (clocked), i.e., the state register

- Next state calculation

- Output calculation

- May find different combinations of these

- Single process

- Two processes (nextstate + output, state update)

- Three processes (nextstate, output, state update)

- Multiple processes to avoid creating Mealy instead of Moore machine

2023-09-14 45

TSTE12 Design of Digital Systems, Lecture 8

#### State assignment

- States are not coded in VHDL

- Use enumeration

- Allows synthesis tools do a better work

- Powerful computer algorithms usually find better state assignment

- Possible to control state minimisation and assignment in synthesis tool

- E.g. one-hot encoding may be more suitable in same cases

TSTE12 Design of Digital Systems, Lecture 8

entity TWO\_CONSECUTIVE is

2023-09-14 46

### Alternative description: table based

- Small statemachine, one input X and one output Z

- Code the state table as an array with nextstate and output

```

port(CLK,R,X: in BIT; Z: out BIT);

end TWO_CONSECUTIVE;

beain

architecture FSM of TWO CONSECUTIVE is

process(R,X,CLK,FSM_STATE)

type STATE is (S0,S1,S2);

begin

signal FSM_STATE: STATE := S0;

if R = '0' then -- Reset

type TRANSITION is record

FSM_STATE <= S0;

elsif CLK'EVENT and CLK ='1' then -- Clock event

OUTPUT: BIT;

FSM_STATE <= STATE_TRANS(FSM_STATE,X).NEXT_STATE;

NEXT_STATE: STATE;

end record;

end if

type TRANSITION_MATRIX is array(STATE,BIT) of TRANSITION;

if FSM STATE'EVENT or X'EVENT then -- Output Function

constant STATE_TRANS: TRANSITION_MATRIX :=

(S0 => ('0' => ('0',S1), '1' => ('0',S2)),

S1 => ('0' => ('1',S1), '1' => (0',S2)),

Z <= STATE_TRANS(FSM_STATE,X).OUTPUT;

end if;

end process;

S2 => ('0' => ('0',S1), '1' => ('1',S2)));

end FSM:

```