TSTE12 Design of Digital Systems, Lecture 7

# Agenda

- Practical issues

- Algorithm level design

- Larger models

- Time multiplexing

- RTL level models - Control units

- Gate level models

2023-09-11 2

# TSTE12 Deadlines Y,D,ED

- Initial version design sketch and project plan tuesday 12 September

- Weekly meetings should start

- Internal weekly meeting with transcript sent to supervisor

- Lab 2 soft deadline Wednesday 13 September at 21.00

- Lab 2 results will be checked after project end

TSTE12 Design of Digital Systems, Lecture 7

2023-09-11 4

2023-09-11

3

# TSTE12 Deadlines MELE, erasmus

- First project meeting no later than today Monday 11 September

- Tuesday 12 September: First version of requirement specification

- Wednesday 13 September 21.00: Lab 1 deadline

- Pass required to be allowed continued project participation

2023-09-11 5

# Handin (homework), Individual!

- 1<sup>st</sup> handin published today Monday 11 September

- Deadline Monday 18 September 23:30

- Use only plan text editor (emacs, vi, modelsim or similar) for code entry.

- Solve tasks INDIVIDUALLY

- Submit answers using Lisam assignment function

- 4 different submissions for code, one for each code task

- 1 submission for all theory question answers

- Use a special terminal window when working with handins

module load TSTE12; TSTE12handin

TSTE12 Design of Digital Systems, Lecture 7

2023-09-11 6

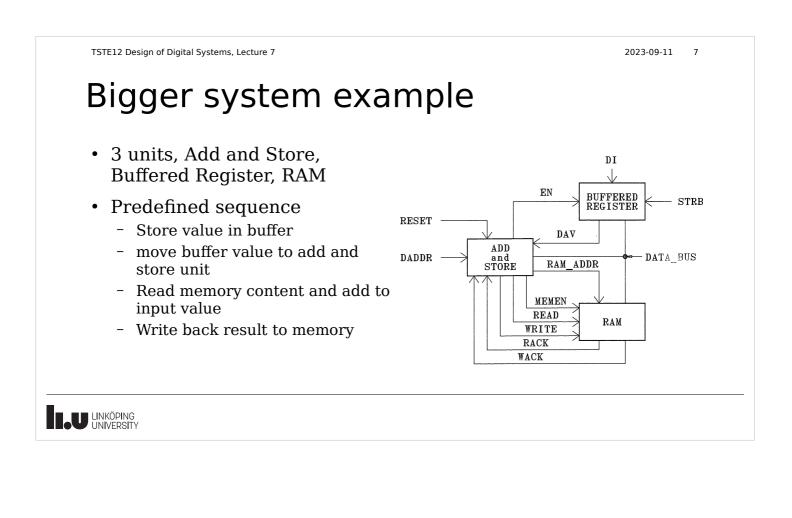

# Algorithm level design

- Focus on functions at high abstraction level

- Subsystems

- Algorithms to use

- Ignore timing, datapaths etc.

```

TSTE12 Design of Digital Systems, Lecture 7

```

# Bigger system example, cont.

- DATA\_BUS driven by all modules

- Requires a resolution function

- Preset to ZZZ to get a useful value (X will always give X)

- Note this is done in the entity! Reason: inout => Driver on the entity

2023-09-11

8

```

entity RAM is

generic(RDEL,DISDEL,ACK_DEL,ACK_PW: TIME);

port(DATA: inout BUS1(7 downto 0):="ZZZZZZZZ";

ADDR: in MVL4_VECTOR(4 downto 0);

RD,WRITE,CS: in MVL4;

RACK,WACK: out MVL4);

end RAM;

```

2023-09-11 10

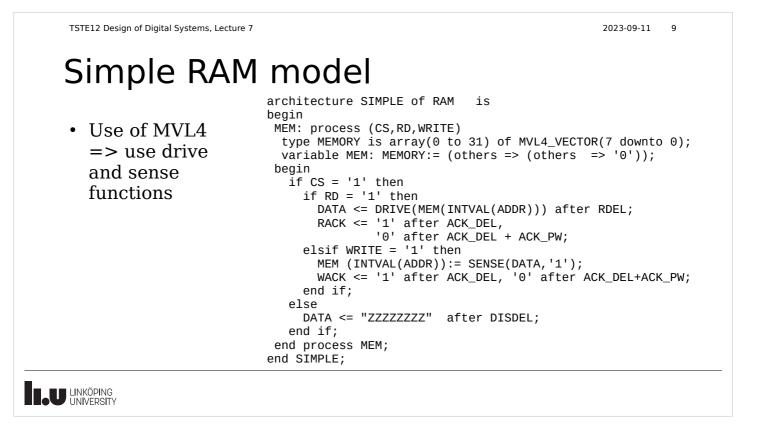

### Bigger example, cont.

- The RAM-model uses an aggregate to initialize all elements to zero

- ADD and Store is a form of a state machine

- Go through a sequence step by step

- Execute some function in each step

- Each step ends in a wait

- Divide system into datapath and control

- Clock generation as earlier (loop with run)

| Bigger example, co                                                                                                                                   | ont.                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| CON: process<br>variable DATA_REG:<br>MVL4_VECTOR(7 downto 0);<br>begin<br>if RESET = '1' thenCS0<br>DATA <= "ZZZZZZZZ"after DIS_DEL;                | DATA_REG :=<br>ADD8(SENSE(DATA,'1'),DATA_REG);<br>READ <= '0'after CON_DEL;<br>MEMEN <= '0'after CON_DEL;CS4<br>wait for CLK_PER;     |

| end if;<br>wait on DAV until DAV = '1';<br>EN <= '1' after CON_DEL;CS1<br>wait for CLK_PER;                                                          | DATA <= DRIVE(DATA_REG) after DO_DEL;<br>WRITE <= '1'after CON_DEL;<br>MEMEN <= '1'after CON_DEL;CS5<br>wait on WACK until WACK ='1'; |

| EN <= '0' after CON_DEL;<br>DATA_REG := SENSE(DATA,'1');CS2<br>wait for CLK_PER;                                                                     | WRITE <= '0'after CON_DEL;<br>MEMEN <= '0'after CON_DEL;CS6<br>DATA <= "ZZZZZZZ" after DIS_DEL;<br>wait for CLK PER;                  |

| <pre>MADDR &lt;= DADDR after MA_DEL;<br/>MEMEN &lt;= '1' after CON_DEL;CS3<br/>READ &lt;= '1' after CON_DEL;<br/>wait on RACK until RACK ='1';</pre> | end process CON;                                                                                                                      |

#### 2023-09-11 12

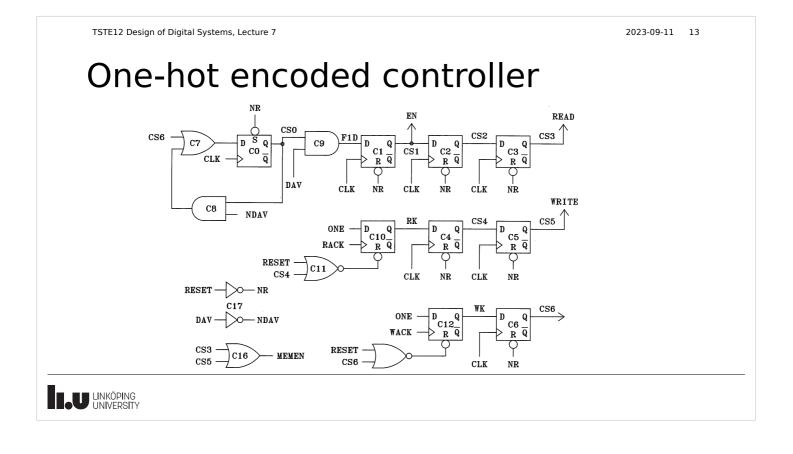

### Control state machine

- Hardware aspects on the control machine

- Wait can not be used in synthesis

- Use a manual direct translation technique

- One-hot encoding

- Simple and straight forward

- Suitable for FPGA implementation

- Low complexity decoding of state

| TSTE12 | Design  | of Digital  | Systems,     | Lecture 7 |

|--------|---------|-------------|--------------|-----------|

| IOILIE | Debigii | or brightan | . oj scenno) | Eccence / |

#### 2023-09-11 14

### Control step classes

- Automatic increase

- From step  $c_i \mbox{ to } c_{i+1}$  after some time

- Handshake

- Wait for DAV, CS1 => EN = 1, Buffer resets DAV when EN = 1

- Asynchronous stepping

- CS3 to CS4: Wait for external RACK edge, RACK may be shorter than 1 clock period!

2023-09-11 15

## Hardware vs Behavioral model

- Important to have same behavior of hardware and VHDL model

- Reset behavior is different

- The model only checks for reset in CS0

- Hardware checked reset everywhere

- Different behavior between model and HW! Bad.

- Add reset check in every control step

TSTE12 Design of Digital Systems, Lecture 7

2023-09-11 16

# Why single clock domainn

- Reset problems

- Even single clock domain should synchronize asynchronous reset inputs

- Must guarantee that whole circuit releases from reset at the same time

#### • Communication problems

- Possible race between data and clock

- Metastability

| TSTE12 Design of Digital Systems, Lecture 7                                                                                                                                                                 | 2023-09-11 17                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Control branching                                                                                                                                                                                           |                                              |

| <ul> <li>Want a control machine able to handle conditional execution of sequences</li> <li>Similar to hierarchical finite state machine (FSM)</li> <li>VHDL cannot do jumps, only breaking loops</li> </ul> | Proc_A<br>X=1 X=0                            |

| <ul> <li>Working implementation approach</li> <li>Sequences in individual processes</li> <li>Check at end of process which process to start next</li> </ul>                                                 | Proc_B Proc_C                                |

| <ul> <li>Output signals from state machine</li> <li>Require Resolution function as assignment done in<br/>multiple processes (need to turn off non-active processes)</li> </ul>                             | Each processes<br>should control<br>signal S |

| Control branching usi                            | ng multiple                                    |

|--------------------------------------------------|------------------------------------------------|

| •                                                | B: process                                     |

| processes                                        | begin<br>SINT <= null:                         |

| architecture TWO of WAIT_STEPS is                | wait on TRIGGERB;                              |

| signal TRIGGERB, TRIGGERBA,                      | SINT <= 2;Step 2                               |

| TRIGGERC,TRIGGERCA: DOT1 := '0';                 | wait for CLK_DEL;<br>SINT <= 3;Step 3          |

| signal SINT: RINTEGER register;                  | wait for CLK_DEL;                              |

| begin                                            | SINT <= null;<br>TRIGGERBA <= not(TRIGGERBA);  |

| A: process                                       | end process B;                                 |

| begin<br>SINT <= null:                           | C: process                                     |

| wait on RUN,TRIGGERBA,TRIGGERCA until RUN = '1'; | begin                                          |

| SINT <= 0;Step 0<br>wait for CLK_DEL;            | SINT <= null;<br>wait on TRIGGERC;             |

| SINT <= 1;Step 1                                 | SINT <= 4;Step 4                               |

| wait for CLK_DEL;<br>SINT <= null:               | wait for CLK_DEL;<br>SINT <= 5;Step 5          |

| if $X = 11$ then                                 | wait for CLK_DEL;                              |

| TRIGGERB <= not(TRIGGERB);                       | SINT <= null;                                  |

| else<br>TRIGGERC <= not(TRIGGERC);               | TRIGGERCA <= not(TRIGGERCA);<br>end process C; |

| end if;                                          | S <= SINT;                                     |

| end process A;                                   | end TWO;                                       |

```

TSTE12 Design of Digital Systems, Lecture 7

```

```

2023-09-11 20

```

# Time Multiplexing, non-working

- Two-phase clock

- One pulse each alternating

- Resolved output signal Z

- Allows multiple assignment

- Problem

- Z = 'X' when PH\_TWO assign '1'

- Assignment from PH\_ONE will not turn off

- Each driver always outputs last assigned value

```

entity TIME_MUX is

generic(DEL1,DEL2: TIME);

port(PHASE_ONE,PHASE_TWO: in MVL4;

Z: out DOTX := '0');

end TIME MUX;

architecture PROCESS IF 0 of TIME MUX is

begin

PH ONE:process(PHASE ONE)

beain

if PHASE_ONE = '1' then

Z \le 0' after DEL1:

end if:

end process;

PH_TWO:process(PHASE_TWO)='1')

begin

if PHASE_TWO = '1' then

Z <= '1' after DEL2;

end if

end PH_TWO;

end PROCESS_IF_0;

```

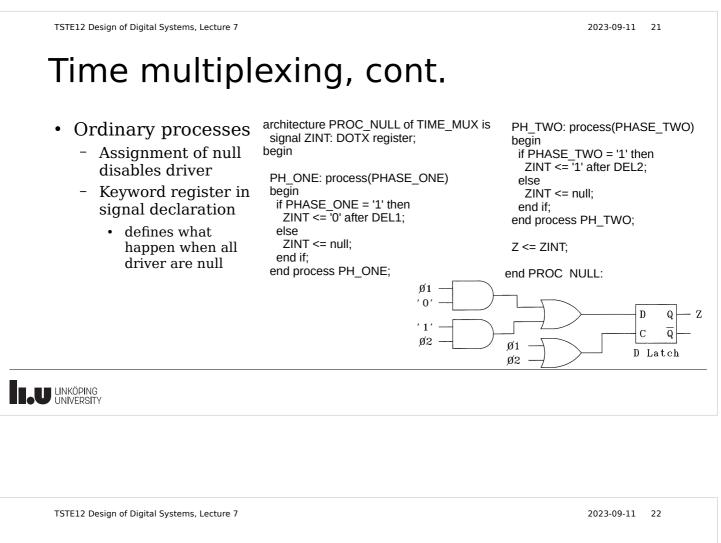

## Time multiplexing, cont.

- Use bus instead of register

- Default resolution function used if not driven

- Resolution function recieves an empty input

- MVL4 resolution function start with 'Z' value!

architecture PROC NULL of TIME MUX is PH TWO: process(PHASE TWO) signal ZINT: DOTX bus; begin if PHASE TWO = '1' then begin ZINT <= '1' after DEL2; PH\_ONE: process(PHASE\_ONE) else begin ZINT <= null; if PHASE ONE = '1' then end if:  $ZINT \le 0'$  after DEL1; end process PH TWO; else ZINT <= null; Z <= ZINT; end if: end process PH\_ONE; Ø1 end PROC\_NULL; ' O ' Ζ '1'· Ø2 Ø1 Ø2

TSTE12 Design of Digital Systems, Lecture 7 Time multiplexing, cont. entity TIME\_MUX is • Without the use of PH TWO: process(PHASE TWO) generic(DEL1,DEL2: TIME); begin Register/Bus. port(PHASE\_ONE,PHASE\_TWO: in if PHASE TWO = '1' then MVL4;  $Z2 \le 1^{-1}$  after DEL2; Z: buffer MVL4); • Separate signals, end if: end TIME MUX; end process PH\_TWO; check 'QUIET to architecture QUIET MUX of TIME MUX is find active Z <= Z1 when not Z1'quiet else signal PH1,PH2,Z1,Z2: MVL4; begin Z2 when not Z2'quiet else assignment 7: PH ONE: process(PHASE ONE) end QUIET\_MUX; begin if PHASE\_ONE = '1' then Z1 <= '0' after DEL1; end if end process PH ONE;

TSTE12 Design of Digital Systems, Lecture 7

# Register transfer level (RTL)

- At this level can the following aspects be analysed

- Compare timing between different units at register level

- Delay in subfunctions, etc.

- Resource allocation

- Number of buses, registers, processing elements etc.

- Scheduling (when to perform an operation)

- Control structure (e.g., microcoded control units)

- Bus design

2023-09-11 24

| <ul> <li>Difference between be</li></ul> | <pre>entity REG_SYS is<br/>port(C: in BIT;<br/>COM: in BIT_VECTOR(0 to 1);<br/>INP: in BIT_VECTOR(0 to 7));<br/>end REG_SYS;<br/>architecture ALG of REG_SYS is<br/>signal R1,R2: BIT_VECTOR(0 to 7);<br/>begin<br/>process(C)<br/>begin<br/>if C='1' then<br/>case COM is<br/>when "00" =&gt; R1 &lt;= INP;<br/>when "01" =&gt; R2 &lt;= INP;<br/>when "01" =&gt; R1 &lt;= ADD8(R1,R2);<br/>when "11" =&gt;<br/>R1 &lt;= ADD8(R1,INC8(not(R2)));<br/>end case;</pre> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | end if;<br>end process;<br>end ALG;                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### 2023-09-11 26

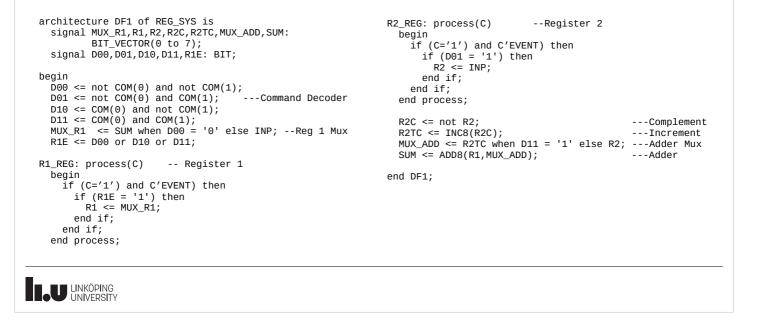

### Behavioral vs Dataflow, cont.

- Dataflow model

- More signals (many for communication)

- Operations are registers, multiplexes, or arithmetic/logic operations

- Global decoding using signals D00 to D11

- Corresponds to a data flow graph

2023-09-11 27

### Behavioral vs Dataflow, cont.

| TSTE12 Design of Digital Systems, Lecture 7 | 2023-09-11 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Described Dataflow impl                     | ementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| • One-to-one mapping                        | <pre>MUX_R1 &lt;= SUM when D00 = '0'<br/>else INP;<br/>R1E &lt;= D00 or D10 or D11;<br/>R1_REG: process(C) begin<br/>if (C='1') and C'EVENT and<br/>(R1E='1') then<br/>R1 &lt;= MUX_R1;<br/>end if; end process;<br/>R2_REG: process(C) begin<br/>if (C='1') and C'EVENT and<br/>(D01='1') then<br/>R2 &lt;= INP;<br/>end if; end process;<br/>R2C &lt;= not R2;<br/>R2TC &lt;= INC8(R2C);<br/>MUX_ADD &lt;= R2TC when D11 = '1'<br/>else R2;<br/>SUM &lt;= ADD8(R1,MUX_ADD);</pre> |

| TSTE12 Design of Digital Systems, Lecture 7                                                                                                                                | 2023-09-11 29                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Control units                                                                                                                                                              |                                 |

| <ul> <li>Hard wired</li> <li>Moore (output only dependent on state)</li> <li>Mealy (output dependent on state and input)</li> <li>Fast</li> <li>Custom designed</li> </ul> |                                 |

| <ul> <li>Microcoded</li> <li>Cheap</li> <li>Standardized (easy to reuse)</li> </ul>                                                                                        |                                 |

|                                                                                                                                                                            |                                 |

| LINKÖPING<br>UNIVERSITY                                                                                                                                                    |                                 |

|                                                                                                                                                                            | 2023-09-11 30                   |

| TSTE12 Design of Digital Systems, Lecture 7                                                                                                                                | 2023-09-11 30                   |

| TSTE12 Design of Digital Systems, Lecture 7                                                                                                                                | 2023-09-11 30                   |

| <ul> <li>AG = Adress generator</li> <li>MAR = Memory Adress Register</li> <li>MIR = Memory Instruction register</li> </ul>                                                 | t<br>lress<br>'ormation<br>trol |

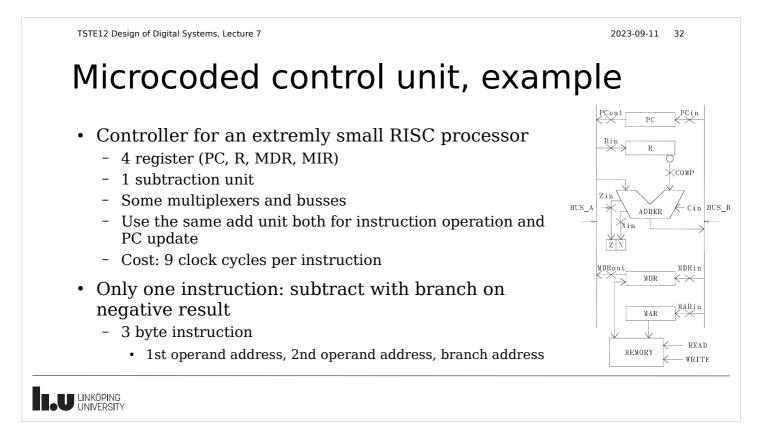

Microcoded control unit

#### Advantages

- Easy to create a generic design

- Only ROM contents needs to be replaced

- Easy to change existing design

- Short design time (low design cost)

- May use compiler to create ROM contents

- Drawbacks

- Slower in many cases (ROM must be read)Only Moore type of controllers

- Small controllers are more expensive due to extra register and ROM

- Must be designed for worst case regarding required features

2023-09-11 31

#### 2023-09-11 34

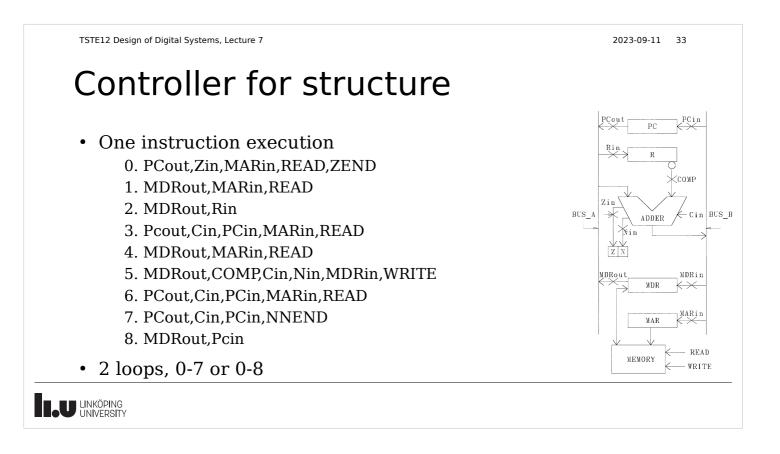

### Control with two jumps, microcoded

- All control steps described in a ROM table

- Easy to understand

- · Easy to redesign

| The microinstructions | ROM |

|-----------------------|-----|

| ROM: process(C)       |     |

| ROM: proce  | ess(C | )           |          |        |        |        |               |  |

|-------------|-------|-------------|----------|--------|--------|--------|---------------|--|

| type SQ     | _ARRA | Y is array  | (0 to 8  | ,0 to  | 8) o   | f BIT; |               |  |

| constant    | t MEM | : SQ_ARRAY  | £ :=     |        |        |        |               |  |

| 0           | 1     | 2 3         | 4        | 5      | 6      | 7      | 8 COLUMN      |  |

| MDR_OUT, MA | AR_IN | ,N_IN,R_IN, | , PC_IN, | ZEND,  | C_IN,  | WRITE, | NNEND, micins |  |

| (('0',      | '1',  | '0', '0',   | '0',     | '1',   | '0',   | 'O',   | '0'),0        |  |

| ('1',       | '1',  | '0', '0',   | '0',     | 'O',   | '0',   | '0',   | '0'),1        |  |

| ('1',       | '0',  | '0', '1',   | 'O',     | 'O',   | '0',   | '0',   | '0'),2        |  |

| ('0',       | '1',  | '0', '0',   | '1',     | '0',   | '1',   | '0',   | '0'),3        |  |

| ('1',       | '1',  | '0', '0',   | '0',     | '0',   | '0',   | '0',   | '0'),4        |  |

| ('1',       |       | '1', '0',   |          |        |        |        |               |  |

| ('0',       | '1',  | '0', '0',   | '1',     | '0',   | '1',   | '0',   | '0'),6        |  |

| ('0',       | '0',  | '0', '0',   | '1',     | '0',   | '1',   | 'O',   | '1'),7        |  |

| ('1',       | '0',  | '0', '0',   | '1',     | 'O',   | '0',   | '0',   | '0'));8       |  |

| begin       |       |             |          |        |        |        |               |  |

| MDR_OUT     | <=    | MEM (INTVA  | AL(C),0  | ) afte | er ROI | M_DEL; |               |  |

| MAR_IN      | <=    | MEM (INTVA  | AL(C),1  | ) afte | er ROI | M_DEL; |               |  |

| N IN        | <=    | MEM (INTVA  | AL(C).2  | ) afte | er ROI | M DEL: |               |  |

|    | N_IN       | <=    | MEM(INTVAL(C),2) | aiter ROM_DEL; |  |

|----|------------|-------|------------------|----------------|--|

|    | R_IN       | <=    | MEM(INTVAL(C),3) | after ROM_DEL; |  |

|    | PC_IN      | <=    | MEM(INTVAL(C),4) | after ROM_DEL; |  |

|    | ZEND       | <=    | MEM(INTVAL(C),5) | after ROM_DEL; |  |

|    | C_IN       | <=    | MEM(INTVAL(C),6) | after ROM_DEL; |  |

|    | WRITE      | <=    | MEM(INTVAL(C),7) | after ROM_DEL; |  |

|    | NNEND      | <=    | MEM(INTVAL(C),8) | after ROM_DEL; |  |

| e: | nd process | s ROM | i                |                |  |

2023-09-11 35

# URISC controller, Mealy

• Inclear sequence

TSTE12 Design of Digital Systems, Lecture 7

- Hard to modify

- Faster

```

-Hard Wired Control Unit

--Decoder

--First Stage Decoding

ST0 <= not C(2) and not C(1) and not C(0) after AND_DEL;

ST1 <= not C(2) and not C(1) and C(0) after AND_DEL;

ST2 <= not C(2) and C(1) and not C(0) after AND_DEL;

ST3 <= not C(2) and C(1) and C(0) after AND_DEL;

ST4 <= C(2) and not C(1) and not C(0) after AND_DEL;

ST5 <= C(2) and not C(1) and C(0) after AND_DEL;</pre>

ST6 <= C(2) and C(1) and not C(0) after AND_DEL;

ST7 <= C(2) and C(1) and C(0) after AND DEL;

-Second Stage Decoding

ST07 <= ST0 or ST7 after OR_DEL;

ST25 <= ST2 or ST5 after OR_DEL;

ST36 <= ST3 or ST6 after OR_DEL;

ST57 <= ST5 or ST7 after OR DEL;

ST78 <= ST7 or C(3) after OR DEL;

-Control Signals

PC_OUT <= (ST07 or ST36) and not C(3)

after (OR_DEL + AND_DEL);

C_IN <= ST36 or ST57 after OR_DEL;</pre>

FC_IN <= ST36 or ST78 after OR_DEL;

MAR_IN <= not(ST25 or ST78) after (OR_DEL + INV_DEL);</pre>

MDR_OUT <=not PC_OUT after INV_DEL;

READ <= MAR_IN; COMP <= ST5; N_IN <= ST5; MDR_IN <= ST5;

WRITE <= ST5; R_IN <= ST2; ZIN <= ST0; ZEND <=ST0;

NNEND <= ST7;

```

TSTE12 Design of Digital Systems, Lecture 7

```

2023-09-11 36

```

## More on microcoded controllers

- Lecture 11 will cover more details on microcoded controller structures

- Introduces also lab 3

- Lab 3 includes an example of a microcoded controller structure

- Controller used to control a user interface and a datapath

- Y and D program students have seen this approach in computer technology courses

- Used there for creating machine instruction implementations

2023-09-11 38

### How accurate can a gate model be?

• Example: 2 input OR-gate

Entity OR2 IS Port (I1, I2 : in bit; O : out bit); END OR2; Architecture DELTA\_DEL of OR2 IS BEGIN O <= I1 OR I2; END DELTA\_DEL; Architecture FIXED\_DEL OF OR2 IS BEGIN O <= I1 OR I2 after 3 ns; END FIXED\_DEL;

ENTITY OR2G IS Generic (DEL: TIME)M Port (I1, I2 : in bit; O : out bit); END OR2G; Architecture GNR\_DEL of OR2G IS BEGIN O <= I1 OR I2 after DEL; END GNR\_DEL;

### Model accuracy

- Models are better and better, but not good enough

- Multiple timing models required

- typical delay, max, min

- Want single model, only changing one constant

- Timing\_CONTROL

- Set one constant to define type of timing (min, max, typical)

LINKÖPING UNIVERSITY

```

TSTE12 Design of Digital Systems, Lecture 7

2023-09-11 40

Code example

package TIMING_CONTROL is type TIMING is (MIN,MAX,TYP,DELTA);

constant TIMING SEL: TIMING := TYP

function T_CHOICE(TIMING_SEL: TIMING;

TMIN, TMAX, TTYP: TIME)

return TIME;

end TIMING_CONTROL;

package body TIMING_CONTROL is

use work.TIMING_CONTROL.all;

function T_CHOICE(TIMING_SEL: TIMING;

TMIN, TMAX, TTYP: TIME)

entity OR2_TV is

generic(TMIN,TMAX,TTYP: TIME);

return TIME is

port(I1,I2: in BIT; O: out BIT);

begin

end OR2_TV;

case TIMING SEL is

when DELTA => return 0 ns;

architecture VAR_T of OR2_TV is

when TYP => return TTYP;

begin

when MAX => return TMAX;

O <= I1 or I2 after T_CHOICE(TIMING_SEL,

when MIN => return TMIN;

TMIN,TMAX,TTYP);

end case;

end VAR T;

end T_CHOICE;

end TIMING CONTROL;

```

LINKÖPING UNIVERSITY 2023-09-11 39

2023-09-11 41 TSTE12 Design of Digital Systems, Lecture 7 Additional timing details entity OR2GV is • Timing is asymmetric generic(TPLH,TPHL: TIME); port(I1,I2: in BIT; O: out BIT); - Different rise and fall times end OR2GV; - Needs modeling architecture VAR\_DEL of OR2GV is begin process(I1,I2) variable OR\_NEW,OR\_OLD:BIT; begin OR NEW := 11 or 12; if OR\_NEW = '1' and OR\_OLD = '0' then  $O \stackrel{-}{<=} OR_NEW$  after TPLH; elsif OR\_NEW = '0' and OR\_OLD = '1' then  $O \le OR_NEW$  after TPHL; end if; OR\_OLD := OR\_NEW; end process; end VAR\_DEL;

| TSTE12 Design of Digital Systems, Lecture 7                                                                                                                                                                                      | 2023-09-11 | 42 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|

| Load dependency                                                                                                                                                                                                                  |            |    |

| <ul> <li>Every attached gate input slows the output speed</li> <li>Large fan-out</li> <li>Load is gate dependent <ul> <li>Number of transistor gates connected</li> <li>Size of transistors on input gate</li> </ul> </li> </ul> |            |    |

| <ul> <li>Each connection corresponds to a small delay</li> <li>Model each individual input wire delay</li> <li>Gate delay included in output wire delay</li> </ul>                                                               |            |    |

| <ul> <li>Not good enough still</li> <li>Delay depends on edge slope, temperature, etc.</li> </ul>                                                                                                                                |            |    |

|                                                                                                                                                                                                                                  |            |    |

2023-09-11 43

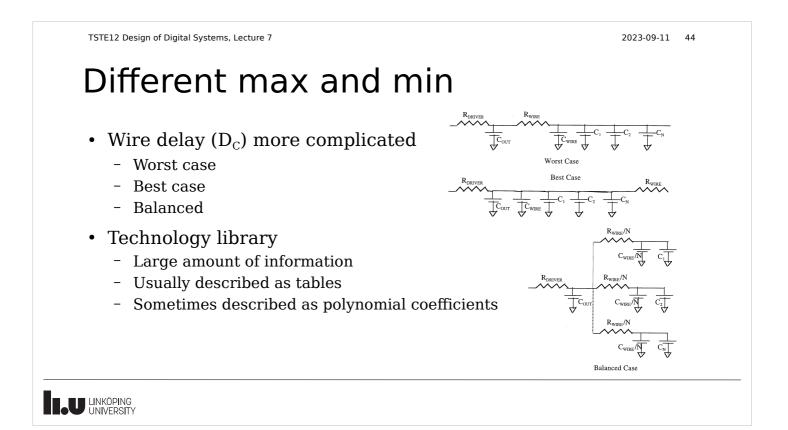

### Common model used in synopsis library compiler

- $D_{TOTAL} = D_I + D_S + D_T + D_C$

- $D_I$  = Intrinsic delay inherent in gate and independent of where/how it is used

- $D_s$  = Slope delay caused by ramp time of the input signal

- $D_T$  Transition delay caused by loading of the output pin (approx  $R_{driver}$  ( $C_{wire}+C_{pin}$ ))

- D<sub>c</sub> Connect media delay to an input pin (wire delay).

|  | LINKÖPING<br>UNIVERSITY |

|--|-------------------------|

|  | UNIVERSITY              |

2023-09-11 45

TSTE12 Design of Digital Systems, Lecture 7

## **Back annotation**

- The process of abstraction

- adding more details to a high level model by analyzing a lower abstraction level model

- Example: Layout information used to generate timing information in a gate netlist

- Standardized way: SDF

- Add timing info from layout to gate level

- Useful for general timing requirements and properties)

- Delays module path, device, interconnect, and port

LINKÖPING UNIVERSITY

```

TSTE12 Design of Digital Systems, Lecture 7

2023-09-11 46

SDF file format

• Timing checks: setup, hold,

(CELL

(CELLTYPE "DFF")

recovery, removal, skew, width,

(INSTANCE top/b/c)

(DELAY

period, and no change

(ABSOLUTE

(IOPATH (posedge clk) q (2:3:4) (5:6:7))

• Timing constraints: path, skew,

(PORT clr (2:3:4) (5:6:7))

)

period, sum, and diff

)

(TIMINGCHECK

(SETUPHOLD d (posedge clk) (3:4:5) (-1:-1:-1))

Each trippel defines min, typical,

(WIDTH clk (4.4:7.5:11.3))

and max delay

)

)

- One for positive edge

- One for negative edge

```

# SDF File format, cont.

- Design/instance-specific or type/library-specific data

- Timing environment:

- intended operating timing environment

- Scaling, environmental, and technology parameters

- Incremental delay builds on the previous models timing by adding/subtracting timing information

2023-09-11 47

2023-09-11 48

• Absolute replaces timing information

TSTE12 Design of Digital Systems, Lecture 7

# Gate models of increasing complexity

- Creating accurate library models is time consuming

- Delay, timechecks etc. can be done in many different ways

- A standard has evolved that defines what parameters to use

- Simplifies back annotation

- Allows for accelerated models (hard-coded)

| VITAL models of gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Three parts: Input delay, Functional<br/>and Path delay</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BEHAVIOR SECTION<br>VITALBehavior : process (A_ipd, B_ipd, C_ipd, D_ipd)<br>functionality results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <pre>library IEEE;<br/>use IEEE.VITAL_Primitives.all;<br/>library LIBVUOF;<br/>use LIBVUOF.VTABLES.all;<br/>architecture VITAL of ONAND is<br/>attribute VITAL_LEVEL1 of VITAL : architecture is TRUE;<br/>SIGNAL A_ipd : STD_ULOGIC := 'X';<br/>SIGNAL C_ipd : STD_ULOGIC := 'X';<br/>SIGNAL D_ipd : STD_ULOGIC := 'X';<br/>begin<br/> INPUT PATH DELAYS<br/>WireDelay : block<br/>begin<br/>vitalWireDelay (A_ipd, A, tipd_A);<br/>vitalWireDelay (B_ipd, B, tipd_B);<br/>vitalWireDelay (C_ipd, C, tipd_C);<br/>vitalWireDelay (D_ipd, D, tipd_D);<br/>end block;</pre> | <pre> Functionality Section<br/>Y_zd := (NOT ((D_ipd) AND ((B_ipd) OR (A_ipd) OR C_ipd))<br/> Path Delay Section<br/>VitalPathDelay01 (<br/>OutSignal =&gt; Y,<br/>GlitchData =&gt; Y_GlitchData,<br/>OutSignalName =&gt; "Y",<br/>OutTemp =&gt; Y_zd,<br/>Paths =&gt; (0 =&gt; (A_ipd'last_event, tpd_A_Y, TRUE),<br/>1 =&gt; (B_ipd'last_event, tpd_B_Y, TRUE),<br/>2 =&gt; (C_ipd'last_event, tpd_C_Y, TRUE),<br/>3 =&gt; (D_ipd'last_event, tpd_D_Y, TRUE)),<br/>Mode =&gt; OnDetect,<br/>Xon =&gt; Xon,<br/>MsgOn =&gt; MsgOn,<br/>MsgSeverity =&gt; WARNING);<br/>end process;<br/>end VITAL;</pre> |

2023-09-11 50

# Detection of timing errors

- Input path delay: Transport delay dependent on previous value and wire delay

- Functional part. Boolean expression or lookup tables for fast simulation

- Path delay: output delay, glitch handling

- Models often includes error detection

- Short spikes, short setup/hold timing etc.

- Unacceptable values (Z or X)

- Unacceptable input combinations (both set and reset active on SR flipflop)