#### Agenda

- Practical issues

- Short tool overview

- Introduction to VHDL, continued

- Timing

- Testbench

2022-09-05

2022-09-05 3

#### TSTE12 Deadlines Y,D,ED

- First meeting with supervisor should happen no later than today!

- Determine project manager (contact person)

- Questions (short meeting)

- Lab 1 deadline Wednesday 7 September at 21.00

- Tuesday 6 September: First version of requirement specification

- We use LIPS "light", want to capture expected behavior of final result in requirement specification

TSTE12 Design of Digital Systems, Lecture 4

2022-09-05 4

#### TSTE12 Deadlines MELE, erasmus

- Group definition Wednesday 7 September (afternoon)

- On web, include supervisor assignment

- Friday 9 September: First meeting with supervisor

- Determine project manager (contact person)

- Question (short meeting)

- Tuesday 13 September: First version of requirement specification

#### MUX lab access

- LiU-card should now give access to MUX1 lab

- Email me if you can not get into the lab

- Lab available 5-23 every day

- Make sure to verify in schedule server if lab is available outside course schedule

- MUX1 mostly used only for TSTE12

- MUX2 also sometimes available (used more by other courses)

- Remote login: use thinlinc

TSTE12 Design of Digital Systems, Lecture 4

#### Project issues

- Expected project participation conduct

- Do no be late to meetings

- Inform the rest of the group if you have problem attending a meeting (in advance if possible)

- Keep track of your project work, noting amount and type of task

- Documents should be discussed and approved by supervisor

- Possible to fail project even if design works

- Possible for individual to fail project even if rest of group get a pass!

2022-09-05 5

<section-header>

Project hints

9. Hints about Requirement specification

9. Possible subsystem: control, display, audio processing

9. Add plenty of features

9. Set priority (low, medium, high)

9. Avoid multiple requirements in one requirement statement

9. Hints about design specification

9. Should indicate idea about general building blocks

9. Interfaces (signals/data to communicate)

9. Behavior

2022-09-05

2022-09-05

8

7

TSTE12 Design of Digital Systems, Lecture 4

TSTE12 Design of Digital Systems, Lecture 4

#### Design flow and tools

- Three types of examined activities in the course

- Handin

- Lab

- Project

- For handins (start next week): use simple text editor + modelsim

- Start the TSTE12handin shell

- Write code, compile, simulate, finally upload code

- Chapter 2 tutorial notes shows how to use modelsim http://www.isy.liu.se/edu/kurs/TSTE12/kursmaterial/

#### HDL Designer tool

- Design entry tool, main entry tool to the project

- Tutorial chapter 3 introduce this www.isy.liu.se/edu/kurs/TSTE12/kursmaterial

- Tools used to manage libraries, design, and other tools for use by larger designer groups

- Graphic and text design entry

- Tool startup configurations

- Support many different languages and tools

- Version control, team management....

- Highly configurable

TSTE12 Design of Digital Systems, Lecture 4

#### HDL Designer tool, cont.

- Top level: The project (defined by xxx.hdp file)

- Contains list of libraries, (1 or more)

- Each library contains design units

- Described as components (green and blue boxes)

- Each unit have different view

- Graphic and/or textual

- Various forms of architectures (text, block, FSM, ...)

- A default architecture view is indicated by a blue arrow

- Interfaces with simulation and synthesis tools

#### HDL Designer tool, cont.

- Green boxes (components)

- Fixed interface (does not automatically update)

- Possible to reuse in multiple designs

- Blue boxes (subsystems)

- Updates interface when adding/removing inputs/outputs in block diagram (remember to save schematic to update VHDL)

- Tools can generate valid VHDL from graphical representation (schematics, state machines, etc.)

- State machine example in lab3 lab material

TSTE12 Design of Digital Systems, Lecture 4

#### VHDL timing

- Two types of time in VHDL

- Variables: no delay in update

- Signals: standard time delay and/or delta delay

- Delta delay

- Never adds up to a standard time unit

- Default delay when assigning signals unless delay is specified

- Known as macro and micro timing

2022-09-05 11

<page-header><page-header>

2020 203

214

Comparing the program flow

An entries in queue then stop, else increase time to next time entry in queue.

Start a new simulation cycle without advancing simulation time. Remove all entries scheduled for current simulation time, update all signals. Activate triggered processes.

Execute activated processes. Schedule new time queue entries.

Concurrent assignment can be seen as processes.

TSTE12 Design of Digital Systems, Lecture 4

2022-09-05 14

#### **Unexpected simulation results**

- Time may stand still in simulation by continuous signal updates

- Example: process triggered by a signal that it is updating

- Combinatorial loops without macro delay in assignments

#### Simulation models

- Delta delay only

- Functional verification of models

- Standard time unit delay only

- Validate system timing

- Mixed

- Delta delay where delay is not important

- Standard time unit delay where delay is significant

- Study system timing

.

TSTE12 Design of Digital Systems, Lecture 4

#### Example of models

| Entity BUFF is<br>port (X: in BIT; Z out BIT);<br>end;<br>Architecture ONE of BUFF is<br>signal Y: BIT;<br>begin<br>process(X)<br>variable Y : BIT;<br>begin<br>Z <= X;<br>end process;<br>end ONE; | architecture TWO of BUF is<br>signal Y: BIT;<br>begin<br>process(X)<br>begin<br>$Y \le X$ ;<br>end process<br>$Z \le Y$ ;<br>end TWO;<br>architecture THREE of BUF is<br>signal Y1,Y2: BIT;<br>begin<br>Y1 <= X;<br>Y3 <= Y2;<br>Y2 <= Y1;<br>Z <= Y3; |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                     | end THREE;                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                     | <pre>port (X: in BIT; Z out BIT);<br/>end;<br/>Architecture ONE of BUFF is<br/>signal Y: BIT;<br/>begin<br/>process(X)<br/>variable Y : BIT;<br/>begin<br/>Z &lt;= X;<br/>end process;</pre>                                                           |

2022-09-05 15

| TSTE12 Design of Digital Systems, Lecture 4                                            | 2022-09-05 17                                      |

|----------------------------------------------------------------------------------------|----------------------------------------------------|

| Example models, cont.                                                                  | Architecture FIVE of BUFF is signal Y5: BIT;       |

| Two almost identical buffers                                                           | begin<br>process( <mark>X</mark> )<br>begin        |

| <ul> <li>Have very different simulation behavour</li> </ul>                            | Ў5 <= Х;<br>Z <= Y5;                               |

| <ul> <li>Both probably generate same hardware in<br/>synthesis</li> </ul>              | end process;<br>end FIVE;                          |

| <ul> <li>Lacking entries in sensitivity list</li> </ul>                                | architecture FIVE_A of BUF is<br>signal Y5: BIT;   |

| <ul> <li>Solution: Always add all input signals to the<br/>sensitivity list</li> </ul> | begin<br>process( <mark>X,Y5</mark> )<br>begin     |

| • Drawback: unnecessary process triggering may give slower simulation                  | Y5 <= X;<br>Z <= Y5;<br>end process<br>end FIVE_A; |

```

TSTE12 Design of Digital Systems, Lecture 4

```

## Inertial and Transport delay

- Delay can be of two types (3 in VHDL93)

- Inertial Z <= I after 10 ns;

- If input change again before end of delay then do not update output

- Filter out short glitches (RC delay)

- Transport Z <= transport I after 10 ns;</li>

- "True" delay of signal (like transmission lines)

- Reject (VHDL93) Q <= reject 4 ns inertial a after 10 ns;</li>

- Q\_tmp <= A after 4 ns; Q <= Q\_tmp after 6 ns;

2022-09-05 19

#### Implementation of Inertial and Transport delay in simulator

- Important to understand why a signal change may not reach the assigned signal

- Transaction

- Pair of value and time. What value when

- Waveform

- A series of transactions (sorted by time value)

- Current value of driver

- Value of transaction whose time is not greater than current simulation time. Removed when simulation time is updated if next transaction time is reached

TSTE12 Design of Digital Systems, Lecture 4

2022-09-05 20

#### Waveform update algorithm

1. All old transactions with time at or after earliest new transaction are deleted. Add new transactions to the waveform

If inertial then

- 2. Mark all new transactions

- 3. Mark old transaction if it immediately precedes a marked transition and its value is the same as the marked transaction

- 4. Mark the current value transaction

5. All unmarked transactions are removed

2022-09-05 21

#### Waveform update example

- Z <= I after 10 ns; (I is a 5 ns pulse starting at t=0)

- First change Z updated to '1' at t=0, (10,'1') transaction added

Both current and transaction marked and kept

- Second change, Z updated to '0' at t=5, (15,'0') transaction added

- If inertial: (10,'1') not marked, removed

- End result: the pulse on I is not visible on Z (filtered out)

TSTE12 Design of Digital Systems, Lecture 4

#### Inertial delay side effects

- Process for generating reset signal Res

- Only executed once at start

- First assignment is eliminated by second assignment

- Use transport or combined assignment to get pulse

Res <= transport '1' after 50 ns;

Res <= transport '0' after 100 ns;

• Generate complete waveform instead

Res <= '1' after 50 ns, '0' after 100 ns;

Process begin Res <= '1' after 50 ns; Res <= '0' after 100 ns; wait; end process;

2022-09-05 22

2022-09-05 23

# Modeling of combinational and sequential logic

- Simple approach.

- Process sensitivity list = circuit inputs

- Compute new value using variables

- Assign output signal with delay

- Possible to synthesize (ignoring delay)

- Models uses generic in the port

- Adds parameters to components without need of a signal

- May have default values in entity declaration

LINKÖPING UNIVERSITY

TSTE12 Design of Digital Systems, Lecture 4

2022-09-05 24

#### **Combinational logic examples**

| <ul> <li>Gate</li> </ul> |

|--------------------------|

|--------------------------|

- Generic states delay

- May have default delay defined

```

entity NAND2 is

generic(DEL: TIME);

port(I1,I2: in BIT; 0: out BIT);

end NAND2;

architecture DF of NAND2 is

begin

0 <= I1 nand I2 after DEL;

end DF;

```

port map(A(0),A(1),I2); U4 : NAND\_GATE port map(A(2),I1,I3); U5 : NAND\_GATE port map(I2,I3,C(1));

```

end STRUCTURAL;

```

2022-09-05 25

#### Combinational logic examples, cont.

- Two-to-4 decoder

- Set one of the four outputs to '1' based on the I input value

entity TWO\_TO\_4\_DEC is generic(DEL: TIME); port(I: in BIT\_VECTOR(1 downto 0); 0: out BIT\_VECTOR(3 downto 0)); end TWO\_TO\_4\_DEC; architecture ALG of TWO\_TO\_4\_DEC is begin process(I) begin case I is when "00" => 0<= "0001" after DEL; when "01" => 0<= "0010" after DEL; when "10" => 0<= "0100" after DEL; when "11" => 0<= "1000" after DEL; end case; end process; end ALG;

TSTE12 Design of Digital Systems, Lecture 4

2022-09-05 26

#### Sequential logic process template

process(clk, ...) beain Must check both event and if <async expressions> then level to detect clock edge async behavior elsif clk'event and clk='1' then sync behavior - Alternative functions endif available in the std\_l,ogic end process; libraries rising\_edge, falling\_edge process(c1k) • Do NOT do the following: process(clk) begin begin if clk='1' if clk='1' then • This is acting as a flip-flop sync behavior then endif based design, but is synthesized Q <= Q;endif end process; to a latch based one! end process;

2022-09-05 27

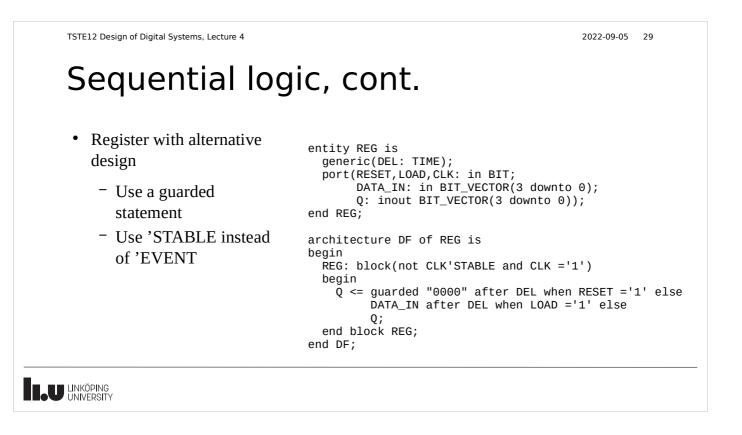

## Sequential logic, cont.

- Latch

- Latches missing the edge detection

- Bad design style

TSTE12 Design of Digital Systems, Lecture 4

- Synthesis result not working

- Flipflop would only copy D when a positive edge on Clk

```

entity LATCH is

generic(LATCH_DEL:TIME);

port(D: in BIT_VECTOR(7 downto 0);

CLK: in BIT;

LOUT: out BIT_VECTOR(7 downto 0));

end LATCH;

architecture DFLOW of LATCH is

begin

LATCH: process(clk,D)

begin

If (clk='1') then

LOUT <= D after LATCH_DEL;

end if;

end process;

end DFLOW;

```

| Sequential                                                        | logic                                                                                                                   | architecture ALG of JKFF is<br>begin<br>process(CLK,S,R)                                                                                                                    |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>JK flipflop with<br/>asynchronous set/reset</li> </ul>   | <pre>entity JKFF is   generic(SRDEL,CLKDEL: TIME)   port(S,R,J,K,CLK: in BIT;         Q,QN: inout BIT); end JKFF;</pre> | <pre>begin<br/>if S = '1' and R = '0' then<br/>Q &lt;= '1' after SRDEL;<br/>QN &lt;= '0' after SRDEL;<br/>elsif S = '0' and R = '1' then<br/>Q &lt;= '0' after SRDEL;</pre> |

| <ul> <li>Edge trigged using 'ev</li> </ul>                        | vent                                                                                                                    | QN <= '1' after SRDEL;<br>elsif CLK'EVENT and CLK = '1' ar                                                                                                                  |

| - Asynchronous update                                             |                                                                                                                         | S='0' and R='0' then<br>if J = '1' and K = '0' then                                                                                                                         |

| <ul> <li>Higher priority that<br/>clocked circuit fund</li> </ul> |                                                                                                                         | Q <= '1' after CLKDEL;<br>QN <= '0' after CLKDEL;<br>elsif J = '0' and K ='1' ther<br>0 <= '0' after CLKDEL;                                                                |

| - Synchronous update                                              |                                                                                                                         | QN <= '1' after CLKDEL;<br>elsif J= '1' and K= '1' then                                                                                                                     |

| • Note use of elsif (1<br>used)                                   | nust be                                                                                                                 | Q <= not Q after CLKDEL;<br>QN <= not QN after CLKDEL;<br>end if;                                                                                                           |

| <ul> <li>Edge trigged using</li> </ul>                            | g 'event                                                                                                                | end if;<br>end process;<br>end ALG;                                                                                                                                         |

#### Output feedback problems

- Entity output can NOT be read in the architecture

- Three solutions

- Use INOUT

- Does not match OUT, enables output values to influence internal signal values

- Use BUFFER

- Does not match OUT, complicates building testbenches etc.

- Use OUT with a temporary signal

- use temporary signal everywhere needed (read and assign), assign entity out signal at the end of the architecture

- LINKÖPING UNIVERSITY

| <ul> <li>Run signal indicate when<br/>to start generating clock<br/>pulses.</li> <li>Feedback example         <ul> <li>Need extra variable<br/>to guarantee complete<br/>clock cycles</li> <li>Simulation use only,<br/>will not synthesize</li> </ul> </li> </ul> | <pre>entity CLOCK_GENERATOR<br/>generic(PER: TIME);<br/>port(RUN: in BIT;<br/>CLK: out BIT);<br/>end CLOCK_GENERATOR;</pre> | <pre>architecture ALG of CLOCK_GENERATOR is<br/>signal CLOCK: BIT;<br/>begin<br/>process (RUN,CLOCK)<br/>variable CLKE: BIT := '0';<br/>begin<br/>if RUN='1' and not RUN'STABLE then<br/>CLKE := '1';<br/>CLOCK &lt;= transport '0' after PER/2;<br/>CLOCK &lt;= transport '1' after PER;<br/>end if;<br/>if RUN='0' and not RUN'STABLE then<br/>CLKE := '0';<br/>end if;<br/>if CLOCK='1' and not CLOCK'STABLE<br/>and CLKE = '1'then<br/>CLOCK &lt;= transport '0' after PER/2;<br/>CLOCK &lt;= transport '0' after PER/2;<br/>end if;<br/>end if;<br/>cLOCK &lt;= transport '1' after PER;<br/>end if;<br/>cLK &lt;= CLOCK;<br/>ord process:</pre> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| will not synthesize                                                                                                                                                                                                                                                |                                                                                                                             | end process;<br>end ALG;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

```

TSTE12 Design of Digital Systems, Lecture 4

```

2022-09-05 32

#### Sequential logic, oscillator

| <ul> <li>Wait statement based</li> </ul> | <pre>entity COSC is generic(HI_TIME,LO_TIME: TIME);</pre>                                                                                                                                                                                                  |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - Can not have both wait                 | <pre>port(RUN: in BIT; CLOCK: out BIT := '0');<br/>end COSC;</pre>                                                                                                                                                                                         |

| and sensitivity list in<br>process       | <pre>architecture ALG of COSC is<br/>begin<br/>process<br/>begin<br/>wait until RUN ='1';<br/>while RUN = '1' loop<br/>CLOCK &lt;= '1';<br/>wait for HI_TIME;<br/>CLOCK &lt;= '0';<br/>wait for LO_TIME;<br/>end loop;<br/>end process;<br/>end ALG;</pre> |

|                                          | ,                                                                                                                                                                                                                                                          |

#### Numeric calculations

• Bit-vectors (and std\_logic\_vectors) does not directly correspond to a value

"1011" could mean 11 in decimal (unsigned), or -5 in decimal (2's complement)

- Datatypes are included in supporting packages to enable arithmetic on bit-vectors

- ieee.numeric\_bit.all

- ieee.numeric\_std.all

- Must use defined types signed or unsigned to allow calculations

- Same definitions as bit\_vector and std\_logic\_vector

- Can copy values between types due to same element type

TSTE12 Design of Digital Systems, Lecture 4

2022-09-05 34

#### Numeric calculations example

- Counter incrementing 3-bit count value each clock cycle

- Asynchronous reset

library ieee; use ieee.numeric\_bit.all;

entity INL3\_KB is port ( C : in bit; R : in bit; Q : out bit\_vector(1 to 3)); end entity; architecture KB of INL3\_KB is begin

process(C,R)

variable count : unsigned(1 to 3);

begin

if R = '1' then

count := (others => '0');

elsif C'event and (C='1') then

count := count + 1;

end if;

Q <= bit\_vector(count);

end process;</pre>

end architecture;

2022-09-05 35

2022-09-05 36

#### Numeric calculations details

| Addition does not increment wordlengths             | 101<br>+011 | 0101<br>+0011 |

|-----------------------------------------------------|-------------|---------------|

| <ul> <li>May get overflow</li> </ul>                |             | 1000          |

| <ul> <li>Must signextend to detect carry</li> </ul> |             |               |

#### • Adding different length vectors will sign extend the shortest one

- May still get overflow

- Multiplication always generates an output number of bits equal to the total number of input bits

- Multiplying a 3-bit input with a 4-bit input generates a 7-bit output result

TSTE12 Design of Digital Systems, Lecture 4

#### Avoid old packages

- Before the introduction of numeric\_std and numeric\_bit there where other libraries

- std\_logic\_unsigned, std\_logic\_signed

- std\_logic\_arith

- Do NOT use these, they are obsolete

- Made it difficult/impossible to mix signed and unsigned

2022-09-05 37

#### Including integers

- Integers can be used for synthesis

- If synthesis tool cannot figure out the limits, the result is 32-bit arithmetic

- Subtypes (limiting range) help to reduce hardware and catch unexpected use

- Integers will be implemented as bitvectors

- Either unsigned or signed (2's complement)

- Translation between integer and bitvectors exist

- x\_signed := to\_signed(y\_int,x\_signed'size);

- Translation other way around (unsigned to integer value)

- y\_int = to\_integer(x\_signed);

TSTE12 Design of Digital Systems, Lecture 4

2022-09-05 38

#### Another aspect of signal assignment

- One signal can be assigned from different parts of the code

- Support multiple entities driving the same wire

- Example: Databus in a computer connecting multiple memories and CPU

- Modelling must be strict and clear

- Same result independant of simulator tool

- Should not be able to detect the order the processes where calculated

- Not all data types support multiple sources for the value

2022-09-05 39

#### Multiple assignment on one signal

Each process containing a signal assignment will have a driver in the simulator generating a contribution to the final signal value

- Concurrent signal assignments will have one driver each

- Processes only have one driver for each signal (even with multiple assignment)

- The signal update seen before is done individually on each driver

- One driver does not know anything about other drivers

- When the value of a signal is fetched, the contributions from the different drivers current values are collected.

- The resulting signal value depends on the definition of how to combine the values from the different drivers, using a resolution function

#### TSTE12 Design of Digital Systems, Lecture 4

2022-09-05 40 Example of data types supporting multiple drivers

- Signals driven by multiple drivers must be resolved

- Use a special function that resolves multiple drivers

- Resolution function

- Example: Wired-OR

- signal X1 : WIRED\_OR Bit;

- subtype STD\_LOGIC is RESOLVED STD\_ULOGIC;

- signal Y2 : STD\_LOGIC;

- RESOLVED is the resolution function name

- Called every time the value of the signal is calculated

- Gets all driver values as input

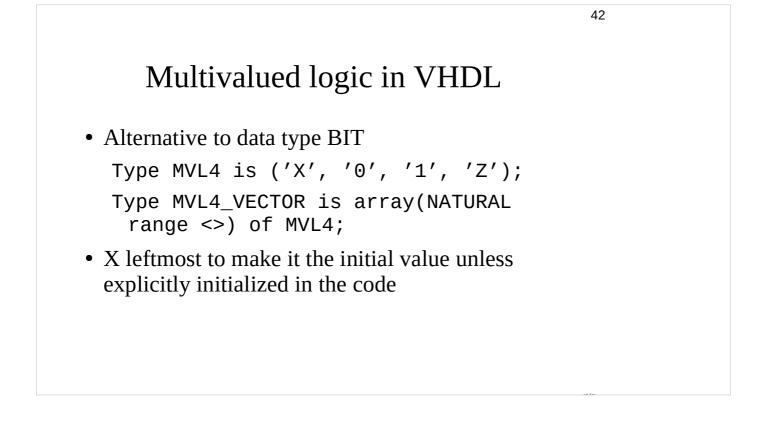

#### Multivalued logic

- Not enough with 0 and 1 to model "real" logic

- Example: Bus

- Requires bus release

- Signal assignment driver can not drop its value

- Use a value to indicate not driven, and indicate nondriven signals (Z)

- Need to indicate conflicting driver (X)

#### Multidriver signals

- Requires a resolution signal

- Different combinations possible

- X always overrides others

- 0 and 1 at the same time gives X

- Z and Z gives Z

# Resolution function definition Subtype DotX is wiredX MVL4; WiredX is the name of the resolution function Function WiredX (V:MVL4\_VECTOR) return MVL4; Where V is a vector containing all values of all drivers of a signal

43

#### Resolution function implementation

```

Implement as a loop and lookup table

Function wiredX (V: MVL4_VECTOR) return MVL4 is

Variable result: MVL4:= 'Z';

Begin

For i in V'RANGE loop -- range not known in advance

Result = table_WIREDX(result,V(i));

Exit when result = 'X';

End loop;

Return result;

End wiredX;

```

```

46

Resolution function impl., cont.

• Check of X in loop is not necessary, but speed up

simulation

Table should then look like:

Type MVL4_TABLE is array (MVL4, MVL4) of MVL4;

Constant table_WIREDX : MVL4_TABLE :=

- -

Х

0

1

Ζ

- -

- -

(('X', 'X', 'X', 'X'), --

('X', '0', 'X', '0'), --

('X', 'X', '1', '1'), --

('X', '0', '1', 'Z')); --

Х

0

1

Ζ

```

#### Resolution function impl. Cont.

- Table lookup may be used for most functions

- Not possible to know the order of the value in V, may therefore require a more complex algorithm