Kent Palmkvist http://www.isy.liu.se/edu/kurs/TSEA44 Based on slides by Andreas Ehliar

TSEA44: Computer hardware - a system on a chip

2022-10-31 2

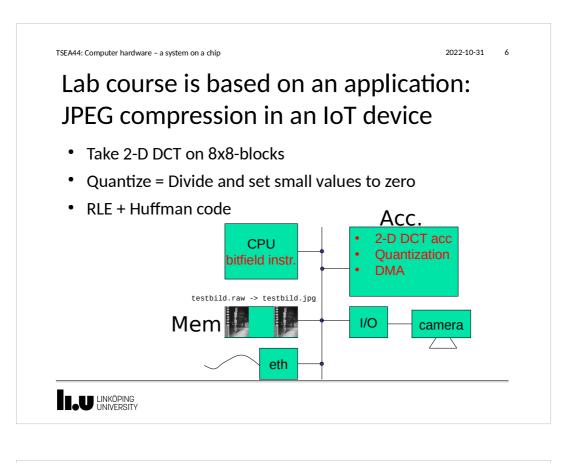

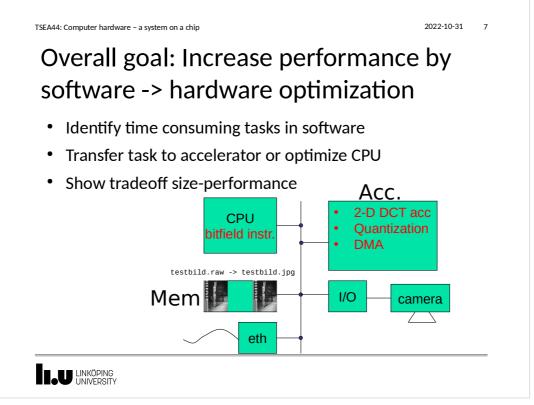

### What is the course about?

- How to build a complete embedded computer using an FPGA and a few other components. Why?

- Only one chip

- The computer can easily be tailored to your needs.

- Special instructions

- Accelerators

- DMA transfer

- The computer can be simulated

- A logic analyzer can be added in the FPGA

- Add performance counters

- It's fun!

2022-10-31 4

# Course organisation

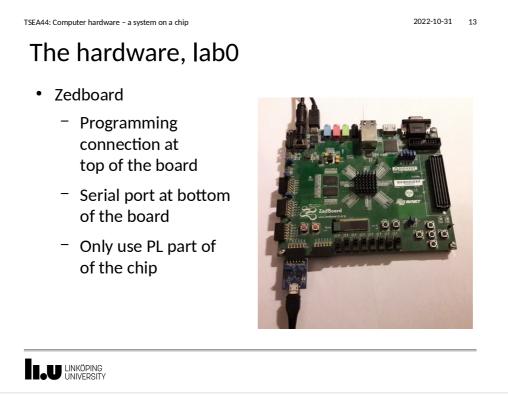

- Lab 0: learn enough Verilog, 4 hours

- Individual work and demonstration

- Lab course: 4 mini projects

- 1-3 people/labgroup

- Lectures: 8\*2 hours

- Examination 6 credits:

- 3 written reports/group

- Oral individual questions

2022-10-31 9

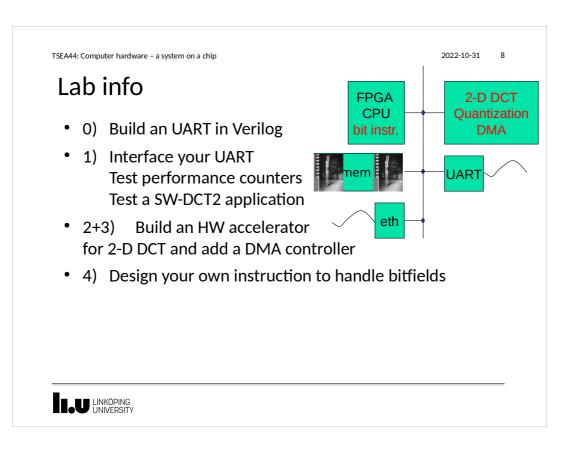

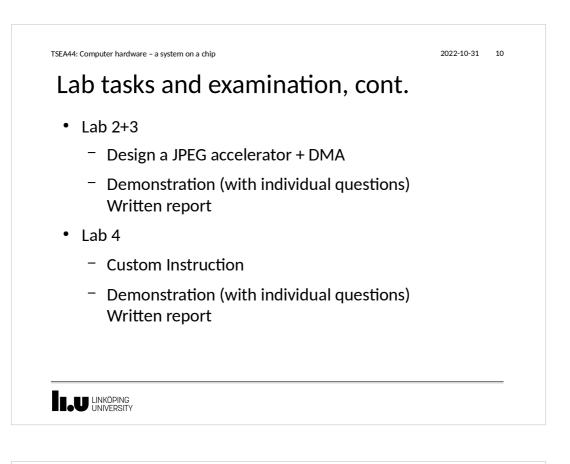

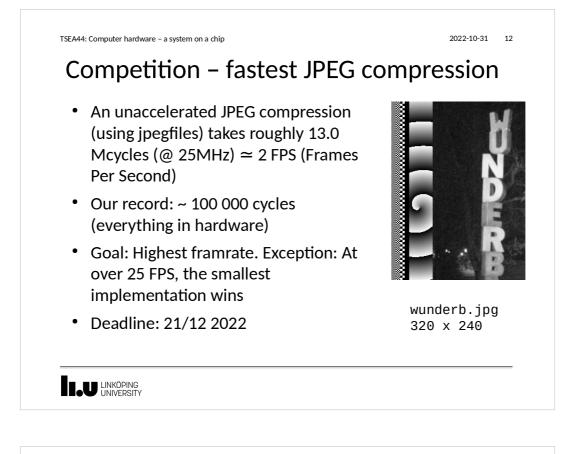

# Lab tasks and examination

- Lab 0 (individual work and demonstration)

- Build an UART in SystemVerilog

- Demonstration

- Deadline 15 November

- Not allowed to join any group before lab0 complete

- Lab 1 (in groups of 2 or 3 students)

- Interface to the Wishbone bus

- Demonstration (individual questions)

Written report

2022-10-31 11

### Written report requirements

- A readable short report typically consisting of

- Introduction

- Design, where you explain with text and diagrams how your design works

- Results, that you have measured

- Cost vs speed gain?

- Conclusions

- Appendix: All Verilog and C code with comments!

2022-10-31 17

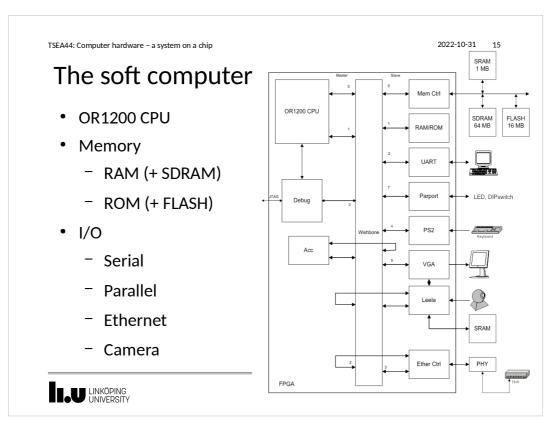

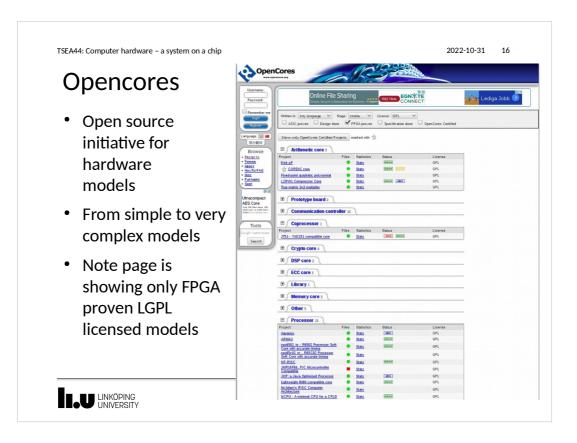

#### Processor core: Openrisc 1200

- Initially developed within opcores initiative

- Split into a new website

- Openrisc.io

- Complete risc processor including synthesizable code, instructions set simulator etc.

| Booting<br>uClinux | uClinux/OR32<br>Flat model support (C) 1998,1999 Kenneth Albanowski, D. Jeff Dionne<br>Calibrating delay loop ok - 2.00 BogoMIPS<br>Memory available: 53000k/62325k RAM, 0k/0k ROM (667892k kernel data, 2182k cor<br>Swansea University Computer Society NET3.035 for Linux 2.0<br>NET3: Unix domain sockets 0.13 for Linux NET3.035.<br>Swansea University Computer Society TCP/IP for NET3.034<br>IP Protocols: ICMP, UDP, TCP<br>uClinux version 2.0.38.1pre3 (olles@kotte) (gcc version 3.2.3) #180 Sat Sep 1:<br>9:01:55 CEST 2004<br>Serial driver version 4.13p1 with no serial options enabled<br>ttyS00 at 0x90000000 (irq = 2) is a 16550A<br>Ramdisk driver initialized : 16 ramdisks of 2048K size<br>Blkmem copyright 1998,1999 D. Jeff Dionne<br>Blkmem copyright 1998 Kenneth Albanowski<br>Blkmem 0 disk images:<br>loop: registered device at major 7<br>eth6: Open Ethernet Core Version 1.0<br>RAMDISK: Loading 1608 blocks into ram disk done.<br>VFS: Mounted root (romfs filesystem).<br>Executing shell<br>Shell invoked to run file: /etc/rc<br>Command: #!/bin/sh<br>Command: hostname bender<br>Command: #<br>Command: # start web server<br>Command: /sbin/baa -d &<br>Command: /sbin/baa -d & |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

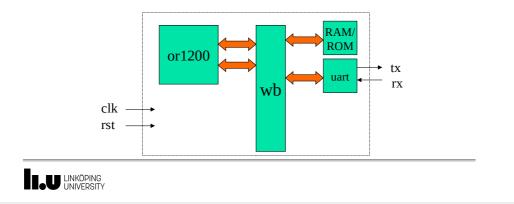

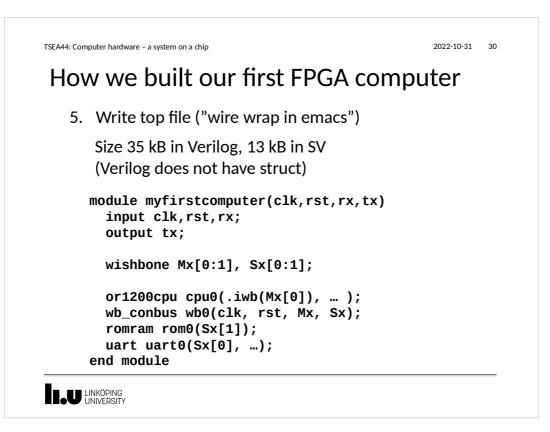

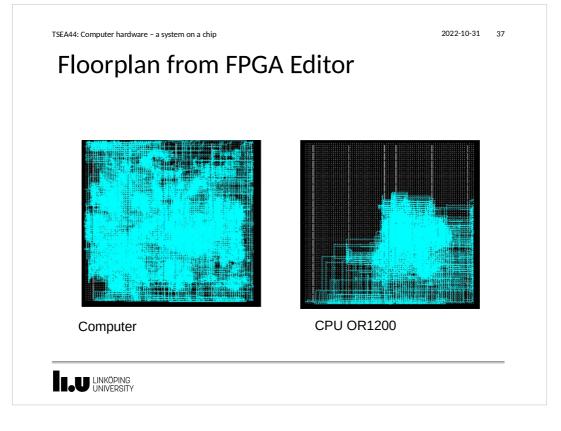

# How we built our first FPGA computer

- 1. Download CPU OR1200, roughly 60 Verilog files

- 2. Download Wishbone bus 3 Verilog files

- 3. Download UART 16550, 9 Verilog files

- 4. Figure out a computer

```

TSEA44: Computer hardware - a system on a chip

```

2022-10-31 31

### How we built our first FPGA computer

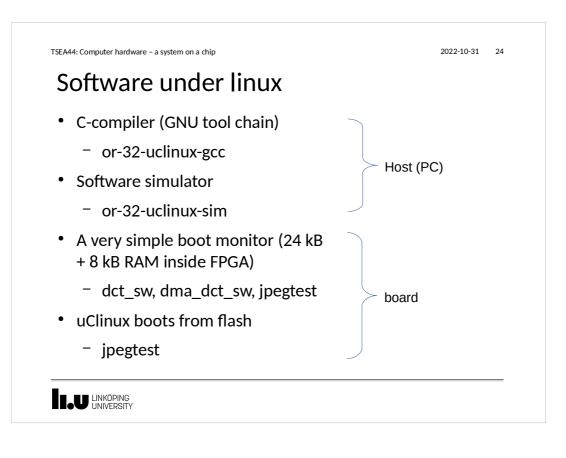

- 6. Download the cross compiler

- 7. Write a small monitor and place in ROM

- 8. ModelSim. Does it boot? Anything on tx?

- 9. Test with the simulator or 32-uclinux-sim

10. Synthesize for 10 minutes (originally 40 minutes, note that simulation are quite important in this course)

| Module      | ++<br>  LUT |      | +<br>  RAMB16 | ++<br>  MULT_18x18 |     |    |

|-------------|-------------|------|---------------|--------------------|-----|----|

| /           | ++<br>  64  |      | +·<br>        | ++                 | 216 |    |

| сри         | 5029        | 1345 | 12            | 4                  | -   |    |

| dvga        | 813         | 755  | 4             |                    | i   |    |

| eth3        | 3022        | 2337 | 4             | i i                |     |    |

| jpg0        | 2203        | 900  | 2             | 13                 |     |    |

| leela       | 685         | 552  | 4             | 2                  |     |    |

| pia         | 2           | 5    |               |                    |     |    |

| pkmc_mc     | 218         | 122  | I             |                    |     |    |

| rom0        | 82          | 3    | 12            |                    |     |    |

| sys_sig_gen |             | 6    |               |                    |     |    |

| uart2       | 825         | 346  |               |                    |     |    |

| wb_conbus   | 616         | 11   |               |                    |     |    |

| Total       | 13559       | 6382 | 38            | 19                 | 216 | F' |

2022-10-31 45

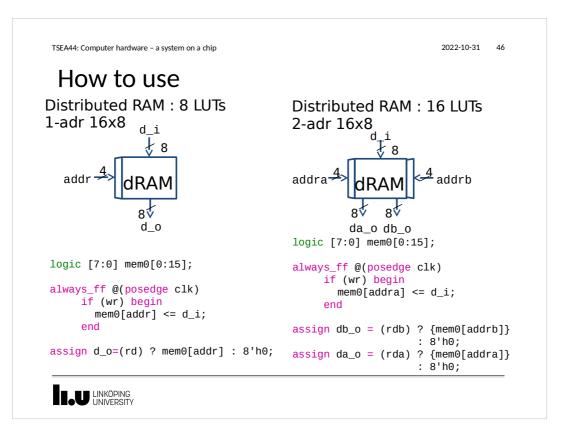

## **Distributed RAM**

- Virtex-II LUT can implement

- 16 x 1-bit synchronous RAM

- Synchronous write

- Asynchronous read

- D flip-flop in the same slice can register the output

- Allow fast embedded RAM of any width

- Only limited by the number of slices in each device

- Example: RAM 16 x 48-bit fits in 48 LUTs

```

2022-10-31 48

TSEA44: Computer hardware - a system on a chip

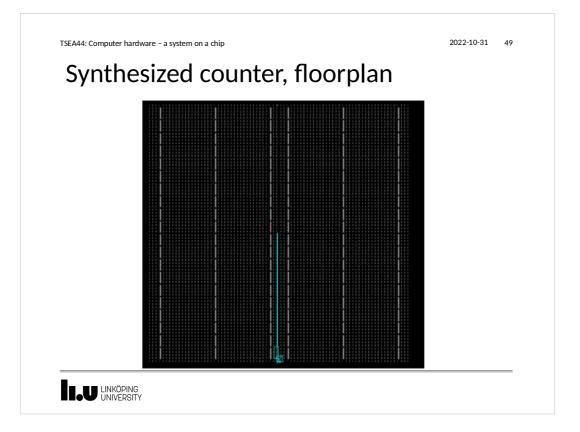

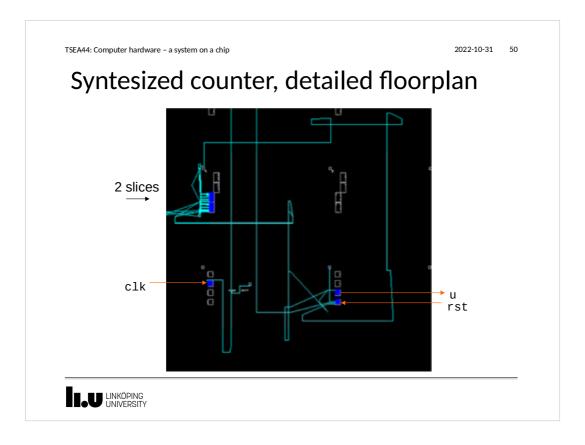

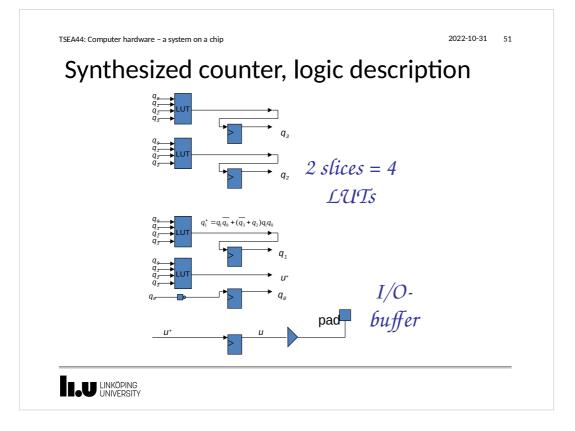

counter

module dec(

input clk,rst

output u);

reg u;

reg [3:0] q;

always_ff @(posedge clk or posedge rst)

if (rst)

q <= 4'h0;

else if (q == 9)

q <= 4'h0;</pre>

else

q <= q+1;

always_ff @(posedge clk)

if (q == 9)

u <= 1'b1;</pre>

else

u <= 1'b0;

endmodule

```

#### 2022-10-31 52

#### Hints for lab work

- Remember to think hardware!

- Draw block diagrams (required!)

- Each block should be simple to translate to verilog

- Counters

- Registers

- Boolean expressions, arithmetic operations

- State machines

- Use testbenches and simulate to verify behavor

- Finally test on hardware