# TSEA44: Computer hardware – a system on a chip

Lecture 5: Lab2 intro, Pitfalls when coding, debugging

#

| TSEA44: Computer hardware – a system on a chip | 2019-11-20 18                 |

|------------------------------------------------|-------------------------------|

| wb_tasks.sv                                    |                               |

| module wishbone_tasks(wishbone.master wb)      | ;                             |

| <pre>int result = 0;</pre>                     |                               |

| reg oldack;                                    |                               |

| reg [31:0] olddat;                             |                               |

| always @(posedge wb.clk) begin                 |                               |

| oldack <= wb.ack;                              |                               |

| olddat <= wb.dat_i;                            |                               |

| end                                            |                               |

| task m_read(input [31:0] adr, output ]         | ogic [31:0] data);            |

| begin                                          |                               |

| <pre>@(posedge wb.clk);</pre>                  |                               |

| wb.adr <= adr;                                 |                               |

| <pre>wb.stb &lt;= 1'b1;</pre>                  |                               |

| wb.we <= 1'b0;                                 | <pre>wb.stb &lt;= 1'b0;</pre> |

| wb.cyc <= 1'b1;                                | wb.we <= 1'b0;                |

| <pre>wb.sel &lt;= 4'hf;</pre>                  | wb.cyc <= 1'b0;               |

|                                                | wb.sel <= 4'h0;               |

| <pre>@(posedge wb.clk);</pre>                  |                               |

| #1;                                            | data = olddat;                |

| while (!oldack) begin                          | end                           |

| <pre>@(posedge wb.clk);</pre>                  | endtask // m_read             |

| #1;<br>end                                     | endmodule // wishbone tasks   |

|                                                |                               |

<page-header><page-header><page-header><page-header><text><list-item>

#### TSEA44: Computer hardware - a system on a chip

2019-11-20 21

### First try

- Modify the testbench so uClinux is present in SDRAM models

- Add interesting signals to the wave window

- Run the simulation over night

###

# Handling long simulation runtimes

- Use checkpointing to reduce/eliminate the need for logging

- Add no signals to wave window (and log for that matter)

2019-11-20 23

2019-11-20 24

- Modify UART so printouts are displayed in the transcript window (using \$display())

- run 100 ms; checkpoint 100ms.chk

- run 100 ms; checkpoint 200ms.chk

- run 100 ms; checkpoint 300ms.chk

- ...

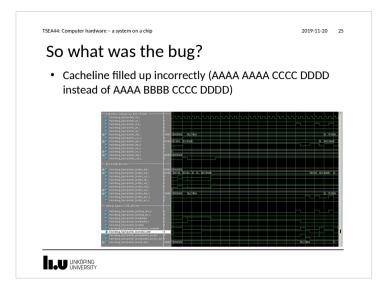

TSEA44: Computer hardware - a system on a chip

TSEA44: Computer hardware - a system on a chip

### Handling long simulation runtime, cont.

- Now you can pinpoint the time interval where the crash happened

- Restore the checkpoint in Modelsim that occured closest before the actual crash

- vsim -restore 600ms.chk

- Debug as usual (by adding signals to wave window/etc)

###

###

## • Post Place-and-Route (PAR) simulation

# - Generate a new netlist using netgen

make sim\_lab0 sdf See lab webpage

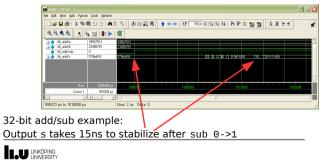

Simulation done with LUTs and FF