Lecture 4: The lab system and JPEG encoding

TSEA44: Computer hardware – a system on a chip

2019-11-14 2

#### Agenda

- Array/memory hints

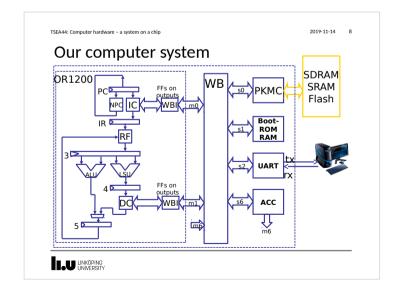

- Cache in a system

- The effect of cache in combination with accelerator

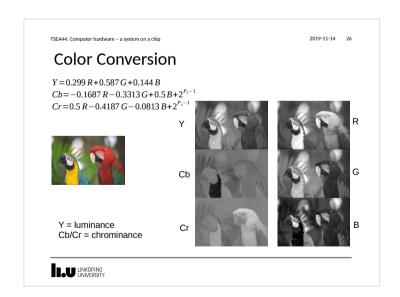

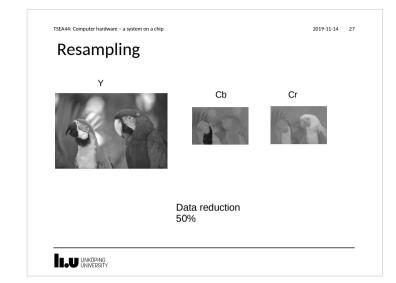

- Introduce JPEG encoding of images

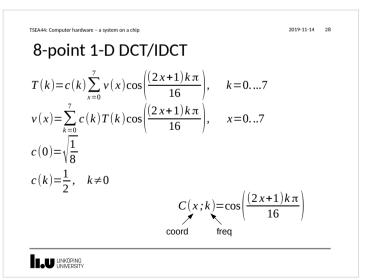

- DCT transform

- Data reduction

TSEA44: Computer hardware - a system on a chip

2019-11-14 3

#### **Practical issues**

- Forming groups

- Require pass on lab0

- Send email to me (to get shared folder access)

- Try to form groups of 2

- Groups of 1 to 3 is ok; 3 is ok, 2 is prefered, 1 is ok

- See exam webpage of course for list of students

- Each group have their own directory to store files /courses/TSEA44/labs/labgrpXX

TSEA44: Computer hardware – a system on a chip

2019-11-14

#### Some tips about arrays/memories

- · FPGA memories can be created using

- Flipflops; asynchronous read, synchronous write

- Distributed using LUTs; asynchronous read, synchronous write, 16x1 each

- BRAMs; synchronous read, synchronous write, 512x32, 1024x16 ....

- · Memories can be designed

- Using templates (BRAMs)

- Inferred (distributed)

TSEA44: Computer hardware - a system on a chip 2019-11-14 5

Some tips about arrays/memories

- Usually describe memory as arrays

- Two ways to describe arrays in SystemVerilog

- Packed, e.g., logic [3:0] p;

- Guaranteed to be continuous

p[3] p[2] p[1] p[0

- Typical for samples, values

- Unpacked, e.g., logic u [3:0];

- Support other data types

- Typical for multiple unit of same type

LIU LINKÖPING

```

TSEA44: Computer hardware - a system on a chip

Unpacked arrays

wire [31:0] bus;

reg [7:0] mem [0:3]; // a 4-byte memory

...

assign bus[31:24] = mem[3];

7

0

mem[0][7:0]

mem[1][7:0]

mem[2][7:0]

mem[3][7:0]

bus[31:0]

```

#### 2019-11-14 9

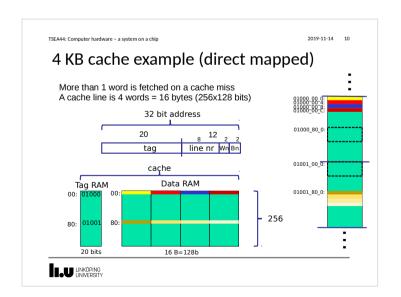

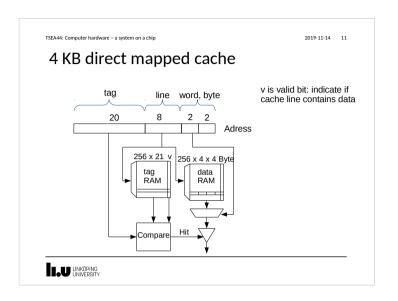

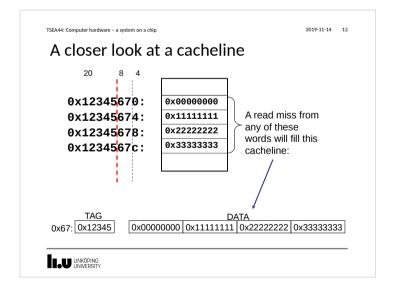

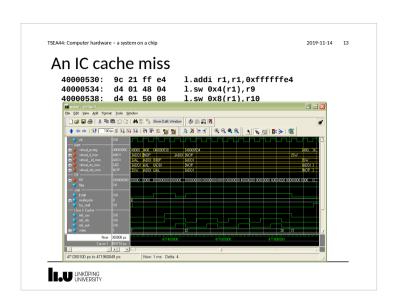

#### Caches

- Essential! Required to get good (close to 1) instructions per clock cycle (IPC)

- Expect to fetch 1 instruction each clock cyle

- Internal (FPGA ROM/RAM) memory have a latency of 3 clockcycles

- External (SRAM/SDRAM/FLASH) have a latency of 4 clockcycles

- Size: (depending on FPGA) there are up to 120 x 2KB block RAMs

- => Select 8KB each for IC and DC

- Type: direct mapped (or set associative)

LIU LINKÖPING

#### 2019-11-14 17

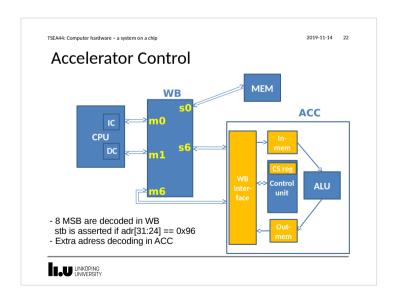

#### Accelerator interfacing

- · Accelerator should implement functionality that is timeconsuming to run on the CPU

- · Interfacing the accelerator require additional data moves

- Simplest case (for the processor)

- CPU send data to accelerator

- CPU gets data from accelerator

- · Data available immediately, no waiting

- Usually difficult to implement, processing takes time

LINKÖPING UNIVERSITY

TSEA44: Computer hardware - a system on a chip

2019-11-14 18

#### Accelerator interfacing, cont.

- More common case: Accelerator require some time to process data

- CPU send data to accelerator

- CPU waits for some time (N clock cycles)

- No useful work performed by processor

- CPU gets data from accelerator

- Worse if time required to wait is unknown

- Busy wait on the bus: Ask accelerator, but not get a respons for many clock cycles => Stalling CPU, locking bus

TSEA44: Computer hardware = a system on a chin

2019-11-14 19

### Accelerator interfacing, cont.

- · Common for the accelerator to have large amount of data to receive, process, and return

- Simplest approach: Use CPU to feed accelerator with data

Mem->CPU

Feed data to accelerator, uses CPU

CPU-> Accelerator

...wait

Return data from accelerator, uses CPU

Accelerator->CPU CPU -> Mem

LINKÖPING UNIVERSITY

TSEA44: Computer hardware - a system on a chip

2019-11-14 20

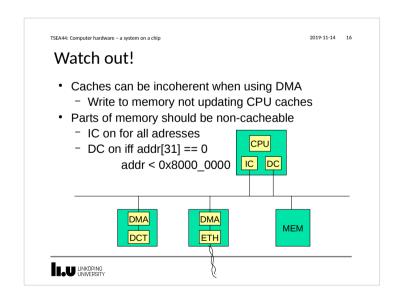

#### Accelerator interfacing, cont.

• Want to reduce load on CPU: let the accelerator do the data moves by itself: DMA! (Direct Memory Access)

CPU setups DMA controller in accelerator (startadress, length)

Mem -> Accelerator Feed data to accelerator, CPU do other things

...processing

Accelerator->Mem Return data from accelerator, CPU do other things

A drawback: Both accelerator and CPU compete for the bus Even worse if a number of accelerators work on data in sequence (Accelerator1 -> Accelerator2 ->...)

LINKÖPING

2019-11-14 21

## Accelerator interfacing, cont.

- Stop communication between accelerators from going over the bus

- Use special memories interconnecting only accelerators

- Remove bus use (increase availability for the CPU)

- The memories are unavailable to the CPU

CPU->Accelerator (setup startadress, length etc.)

Mem->Accelerator1

- ... process in Accelerator1, store result in extra memory

- ... process in Accelerator2, read input from extra memory Accelerator2->Mem

LIU LINKÖPING

TSEA44: Computer hardware - a system on a chip

2019-11-14 23

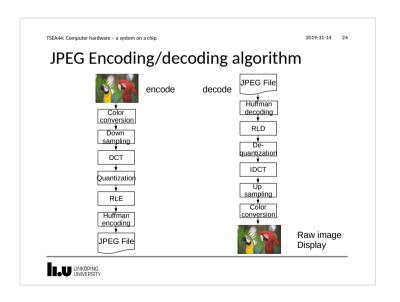

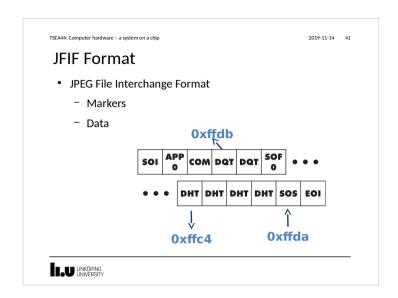

#### JPEG Introduction

- Joint Photographers Expert Group

- Image compression standard defined by JPEG

- Remove things that we cannot see

- Decoded image is slightly different from original

- Lossy compression

LINKÖPING UNIVERSITY

TSEA44: Computer hardware - a system on a chip 2019-11-14 25 **Problem definition** • JPEG compression of testbild.raw 512x400 pixels - JPEG works on 8x8 blocks => 3200 blocks Unaccelerated JPEG takes more than 32 000 000 clock cycles => 1 block takes more than 10 000 clock cycles! ··· Move DCT,Q Move Huffman Build DMA Build accelerator Build new instruction ... M DCT,Q M H ... M H CPU МН M DCT,Q M DCT,Q Accelerator LINKÖPING UNIVERSITY

2019-11-14 29

2019-11-14 30

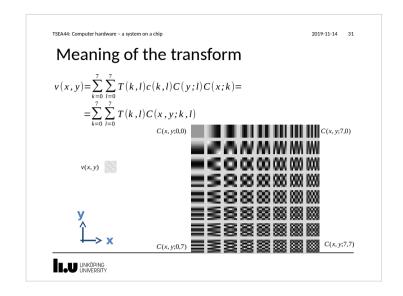

# 8x8-point 2-D DCT/IDCT

$$T(k,l) = c(k,l) \sum_{x=0}^{7} \sum_{y=0}^{7} v(x,y) C(y;l) C(x;k), \qquad k,l = 0...7$$

$$v(x,y) = \sum_{k=0}^{7} \sum_{l=0}^{7} c(k,l) T(k,l) C(y;l) C(x;k), \qquad x,y = 0...7$$

$$c(0,0) = \frac{1}{8} \qquad k = l = 0$$

$$c(k,l) = \frac{1}{4} \qquad else$$

$$C(x;k) = \cos\left(\frac{(2x+1)k\pi}{16}\right)$$

LIU LINKÖPING

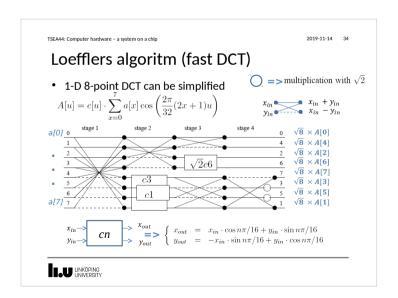

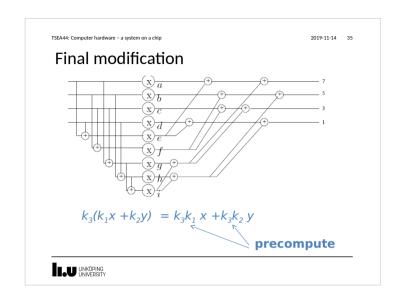

TSEA44: Computer hardware - a system on a chip **Simplifications** T(k,l)=c(k,l)  $\sum_{x=0}^{3n} \left[ \sum_{y=0}^{x-1} v(x,y)C(y;l) \right] C(x;k)$  $= c(k,l) \sum_{x=0}^{7} B(x,l) C(x;k)$

2. 1-D DCT can be simplified for N=8

LU LINKÖPING UNIVERSITY

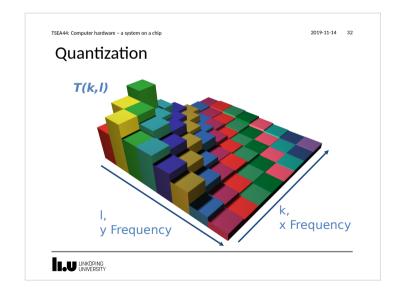

2019-11-14 33 TSEA44: Computer bardware = a system on a chin **Data Reduction** • Transform, rounded division result Y<sub>a</sub> = round (DCT<sub>a</sub>(Y)/Q<sub>i</sub>) 162 162 162 161 162 157 163 161 162 162 162 161 162 157 163 161  $162 \quad 162 \quad 162 \quad 161 \quad 162 \quad 157 \quad 163 \quad 161$ 162 162 162 161 162 157 163 161 162 162 162 161 162 157 163 161  $DCT_2(Y) =$ 164 164 158 155 161 159 159 160 160 160 163 158 160 162 159 156  $\begin{bmatrix} 16 & 11 & 10 & 16 & 24 & 40 & 51 & 61 \\ 12 & 12 & 14 & 19 & 26 & 58 & 60 & 55 \\ 14 & 13 & 16 & 24 & 40 & 57 & 69 & 56 \\ 14 & 17 & 22 & 29 & 51 & 87 & 80 & 62 \\ 18 & 22 & 37 & 56 & 68 & 109 & 103 & 77 \end{bmatrix}$ 24 35 55 64 81 104 113 92 49 64 78 87 103 121 120 101 72 92 95 98 112 100 103 99 LINKÖPING LINIVERSITY

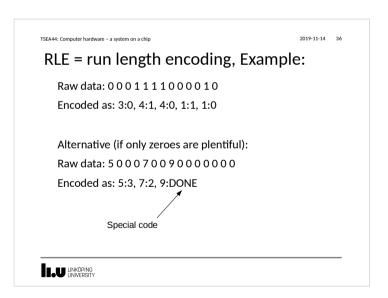

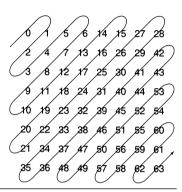

# Zigzag Pattern

- · Increase possibility of zeros at the end of the sequence

- Small energy in highest frequencies

LIU LINKÖPING

TSEA44: Computer hardware - a system on a chip

2019-11-14 38

2019-11-14 37

# Magnitude encoding (DC only)

| Encoded value | DC Value Range |              |

|---------------|----------------|--------------|

| 0             | 0              |              |

| 1             | [-1]           | [1]          |

| 2             | [-3, -2]       | [2, 3]       |

| 3             | [-7, -4]       | [4, 7]       |

| 4             | [-15, -8]      | [8, 15]      |

| 5             | [-31, -16]     | [16, 31]     |

| 6             | [-63, -32]     | [32, 63]     |

| 7             | [-127, -64]    | [64, 127]    |

| 8             | [-255, -128]   | [128, 255]   |

| 9             | [-511, -256]   | [256, 511]   |

| 10            | [-1023, -512]  | [512, 1023]  |

| 11            | [-2047, -1024] | [1024, 2047] |

LINKÖPING UNIVERSITY

2019-11-14 39 TSEA44: Computer hardware - a system on a chip An example of RLE 3) After RLE 1) After Q 22 12 0 -12 0 0 0 0 0 0 -8 0 0 0 0 0 -12 => 12-1, force MSB=0 8-1, force MSB=0 => 0111

2) After zig-zag

22 12 0 4 0 0 -12 0000000000000001

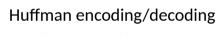

4) Huffman coding

Value are HC (variable length) using table lookup

2019-11-14 40

Run of 0:s Magnitude (number of raw bits)

- raw bits are left untouched

LU LINKÖPING reg

• Analogy: Morse Code

TSEA44: Computer hardware - a system on a chip

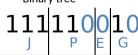

Binary codes

- Mutually exclusive codes

- Binary tree

2019-11-14 42

#### Finally

- AC and DC values are treated differently

- Two Huffman LUTs are used

- DC

- Differential, magnitude encoding, Huffman table lookup

in

code

length

0x00

1010

4

0x01

00

2

0x02

01

2

0x03

100

3

0x04

1011

4

0x05

11010

5

max length=16

- AC

- As mentioned, raw bits left untouched, Huffman table lookup

- Example: value 04, raw bits 1100 => ....10111100....

www.liu.se