# TSEA44: Computer hardware – a system on a chip

Lecture 7: DMA, lab3, testbenches

TSEA44: Computer hardware – a system on a chip

2018-12-05

## Today

- Hints for documentation

- DMA

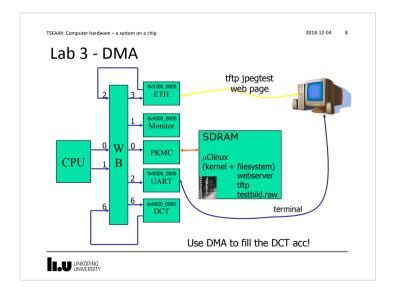

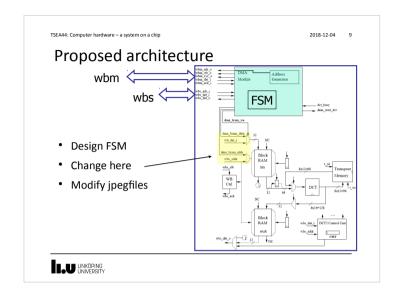

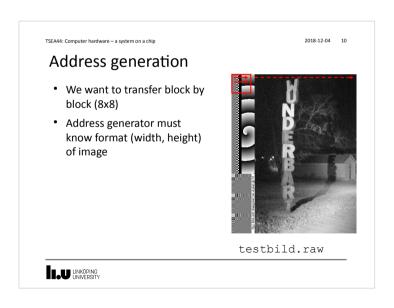

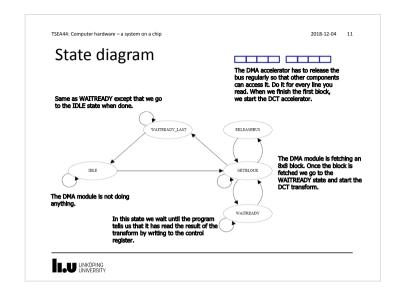

- Lab3

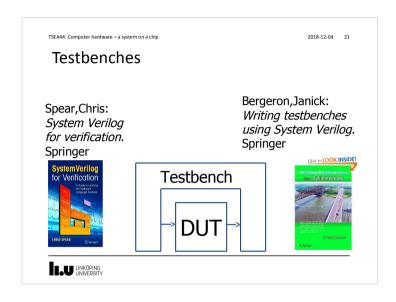

- Testbenches

LINKÖPING UNIVERSITY TSEA44: Computer hardware – a system on a chip

2018-12-05 3

# Lab reports

- Lab1: Section 3.7.2 is good reading

- Specifies what to include (code, diagrams, state graphs)

- Specifies things to discuss in the report

- Same type of section found for the other lab tasks also

- Include all code you have written/modified

- Assume the reader have access to the original lab setup

LINKÖPING UNIVERSITY

TSEA44: Computer hardware – a system on a chip

2018-12-05 4

# Creating schematics

- Alternatives

- Openoffice/libreoffice diagram tool (I use this for slides)

- Inkscape (potentially very nice looking, very cumbersome though)

- Dia (decent if you have RTL library for it)

- TikZ (if you really like latex)

- MS Paint (I'm only kidding)

- Hand drawn schematics from whiteboard/paper

- · Quality problems...

- Visio (if you have a license for it)

LU LINKÖPING UNIVERSITY

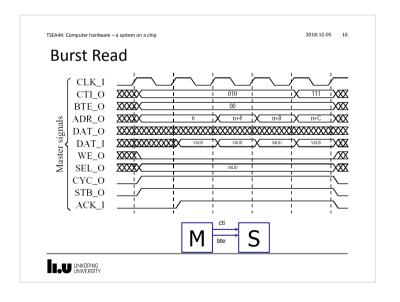

#### TSEA44: Computer hardware – a system on a chip 2018-12-04 17 Burst cycle types Signal group Value Description Classic cycle Constant address burst cycle 010 Incrementing burst cycle 011-110 Reserved 111 End of burst bte 00 Linear burst 01 4-beat wrap burst 10 8-beat wrap burst 11 16-beat wrap burst LIU LINKÖPING

TSEA44: Computer hardware – a system on a chip

2018-12-04 18

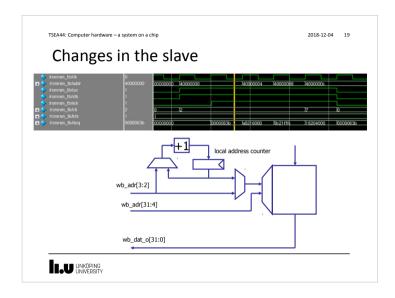

#### Burst access

- Note: Only the SRAM memory controller i the Leela memory controller has burst support

- It is a graphics controller not used in our lab setup

LINKÖPING UNIVERSITY

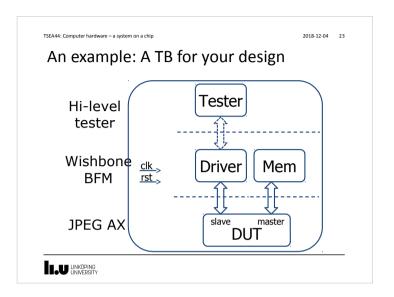

```

2018-12-04 24

TSEA44: Computer hardware – a system on a chip

Testbench: top level

module jpeg_top_tb();

logic     clk = 1'b0;

logic

rst = 1'b1;

wishbone wb(clk,rst), wbm(clk,rst);

initial begin

#75 rst = 1'b0;

always #20 clk = ~clk;

// Instantiate the tester

tester tester0();

// Instantiate the drivers

wishbone_tasks wb0(.*);

// Instantiate the DUT

jpeg_top dut(.*);

mem mem0(.*);

endmodule // jpeg_top_tb

LINKÖPING

UNIVERSITY

```

2018-12-05 00:10

```

2018-12-04 25

TSEAAA: Computer hardware = a system on a chin

Testbench: Hi-level tester

program tester():

int result = 0;

int d = 32'h01020304;

initial begin

for (int i=0; i<16; i++) begin</pre>

jpeg_top_tb.wb0.m_write(32'h96000000 + 4*i, d); // fill inmem

d += 32'h04040404;

jpeg_top_tb.wb0.m_write(32'h96001000, 32'h01000000); // start ax

while (result != 32'h80000000)

jpeg_top_tb.wb0.m_read(32'h96001000,result);  // wait for ax

for (int j=0; j<8; j++) begin

for (int i=0; i<4; i++) begin</pre>

// print outmem

$fwrite(1,"\n");

end

endprogram // tester

LINKÖPING

UNIVERSITY

```

```

TSEA44: Computer hardware - a system on a chip

2018-12-04 26

Testbench: mem

module mem(wishbone.slave wbm)

logic [7:0] rom[0:2047];

logic [1:0] state;

logic [8:0] adr;

integer blockx, blocky, x, y, i;

initial begin

// A test image, same as dma dct hw.c

for (blocky=0; blocky<`HEIGHT; blocky++)

for (blockx=0; blockx<`WIDTH; blockx++)</pre>

for (i=1, y=0; y<8; y++)

rom[blockx*8+x+(blocky*8+y)*`PITCH] = i++; // these are not wishbone cycles

assign wbm.err = 1'b0;

assign wbm.rty = 1'b0;

always ff @(posedge wbm.clk)

if (wbm.rst)

assign wbm.ack = state[1];

state <= 2'h0;

always ff @(posedge wbm.clk)

case (state)

adr <= wbm.adr[8:0];

2'h0: if (wbm.stb) state <= 2'h1;

2'h1: state <= 2'h2;

assign wbm.dat_i = {rom[adr], rom[adr+1],

rom[adr+2], rom[adr+3]};

2'h2: state <= 2'h0;

LU LINKÖPING

UNIVERSITY

```

```

TSEA44: Computer hardware = a system on a chin

2018-12-04 27

DMA? Easy!

// Init DMA-engine

ix. uMa-engine

jpeg_top_tb.wb0.m_write(32'h96001800, 32'h0);

jpeg_top_tb.wb0.m_write(32'h96001804, ?);

jpeg_top_tb.wb0.m_write(32'h96001808, ?);

jpeg_top_tb.wb0.m_write(32'h9600180c, ?);

jpeg_top_tb.wb0.m_write(32'h96001810, ?);

// start DMA engine

for (int blocky=0; blocky<`HEIGHT; blocky++) begin

for (int blockx=0; blockx<`WIDTH; blockx++) begin</pre>

// Wait for DCTDMA to fill the DCT accelerator

result = 0;

$display("blocky=%5d blockx=%5d", blocky, blockx);

for (int j=0; j<8; j++) begin

for (int i=0; i<4; i++) begin</pre>

peg_top_tb.wb0.m_read(32'h96000800 + 4*i + j*16, result);

$fwrite(1,"$5d ", result >>> 16);

$fwrite(1,"$5d ", (result << 16) >>>16);

$fwrite(1,"\n");

jpeg_top_tb.wb0.m_write(?);

// start next block

LIU LINKÖPING

```

```

TSEA44: Computer hardware - a system on a chip

2018-12-04 28

task m_read(input [31:0] adr,

wishbone_tasks.sv

output logic [31:0] data);

@(posedge wb.clk);

wb.adr <= adr:

wb.stb <= 1'b1;

May/may not consume time

wb.we <= 1'b0;

wb.cyc <= 1'b1;

May/may not be synthable

Do not contain always/initial

wb.sel <= 4'hf;

· Do not return values. Pass via output

@(posedge wb.clk);

module wishbone_tasks(wishbone.master wb);

while (!oldack) begin

int result = 0;

@(posedge wb.clk);

reg oldack;

#1;

reg [31:0] olddat;

always ff @(posedge wb.clk) begin

wb.stb <= 1'b0;

oldack <= wb.ack;

wb.we <= 1'b0;

wb.cvc <= 1'b0:

olddat <= wb.dat i;

wb.sel <= 4'h0;

data = olddat;

endtask // m_read

// ************

task m write(input [31:0] adr,

input [31:0] dat);

// similar to m_read

endtask // m write

endmodule // wishbone tasks

LINKÖPING

UNIVERSITY

28

```

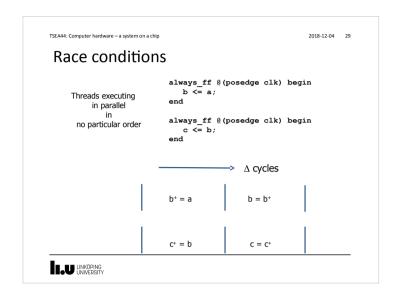

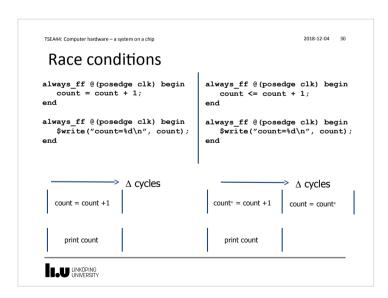

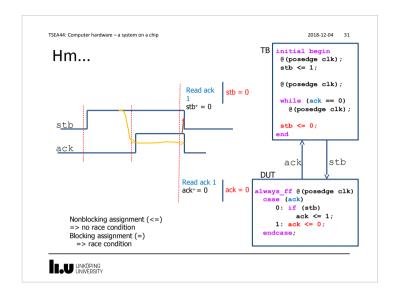

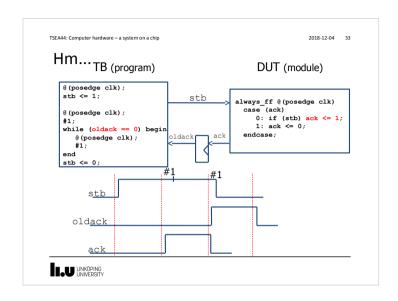

TSEA44: Computer hardware – a system on a chip

2018-12-04 32

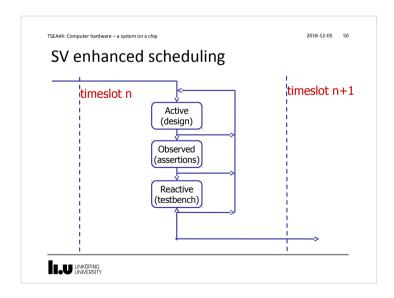

# program block

- Purpose: Identifies verification code

- A program is different from a module

- Only initial blocks allowed

- Executes last

- (module -> clocking/assertions -> program)

- No race situation in previous example!

The Program block functions pretty much like a C program Testbenches are more like software than hardware

```

TSEA44: Computer hardware – a system on a chip

2018-12-04 35

Clocking block

module tb();

clk = 1'b0;

logic

logic

rst = 1'b1:

interface wishbone(input clk,rst);

wire stb.ack;

// instantiate a WB

wishbone wb(clk,rst);

clocking cb @(posedge clk);

input ack;

initial begin

output stb;

#75 rst = 1'b0;

endclocking // cb

modport tb (clocking cb.

always #20 clk = ~clk;

input clk.rst):

// Instantiate the DUT

endinterface // wishbone

jpeg_top dut(.*);

// Instantiate the tester

tester tester0(.*);

mem mem0(.*);

endmodule // jpeg top tb

LINKÖPING

UNIVERSITY

```

```

TSEA44: Computer hardware – a system on a chip

2018-12-04 36

Clocking block

program tester(wishbone.tb wb);

module jpeg_top(wishbone wb);

reg state;

initial begin

assign wb.ack = state;

for (int i=0; i<3; i++) begin</pre>

wb.cb.stb <= 0;

always_ff @ (posedge wb.clk)

if (wb.rst)

wb.cb.stb <= 1:

state <= 1'b0:

while (wb.cb.ack==0)

else if(state)

##1;

state <= 1'b0;

else if (wb.stb)

end

state <= 1'b1;

endprogram // tester

endmodule // jpeg_top

stb

ack

LINKÖPING

UNIVERSITY

```

```

TSEA44: Computer hardware - a system on a chip

2018-12-04 39

OOP

program class t;

// Function in class (object method)

function integer get_size();

class packet;

// members in class

integer size;

get_size = this.size;

integer payload [];

integer i;

// Constructor

function new (integer size);

endclass

this.size = size;

payload = new[size];

for (i=0; i < this.size; i ++)</pre>

initial begin

payload[i] = $random();

end

pkt = new(5);

pkt.print();

$display ("Size of packet %0d",

pkt.get_size());

// Task in class (object method)

task print ();

endprogram

$write("Payload : ");

for (i=0; i < size; i ++)</pre>

$write("%x ",payload[i]);

$write("\n");

LINKÖPING

LINIVERSITY

```

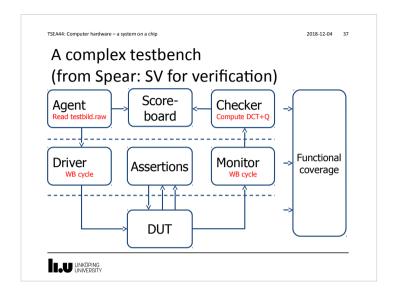

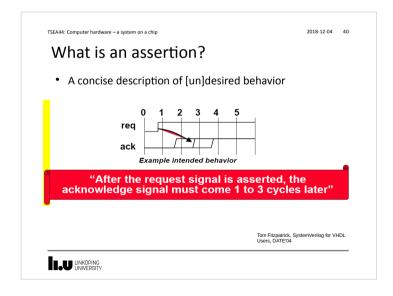

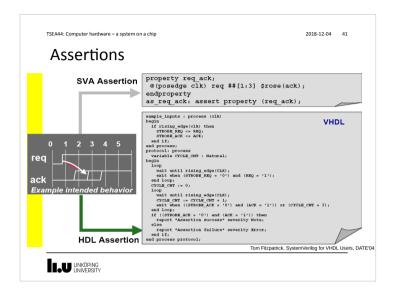

Assertions

Assertions

Assertions are built of

Boolean expressions

Sequences

Properties

Assertion directives

Sequential regular expressions

Describing a sequence of events

Sequences of Boolean expressions can be described with a specified time step in-between

##N delay operator

[\*N] repetition operator

clk

sequence s1;

Q (posedge clk) a ##1 b ##4 c ##[1:5] z;

endsequence

TSEA44: Computer hardware – a system on a chip

2018-12-04 44

# **Properties**

- · Declare property by name

- Formal parameters to enable property reuse

- Top level operators not desired/undesired disable iff reset |->, |=> implication

property p1;

disable iff (rst)

x |-> s1;

endproperty

LINKÖPING UNIVERSITY TSEA44: Computer hardware - a system on a chip

2018-12-04 45

#### **Assertion Directives**

- assert checks that the property is never violated

- cover tracks all occurrences of property

a1: assert p1 else \$display("grr");

LINKÖPING UNIVERSITY

TSEA44: Computer hardware – a system on a chip

2018-12-04 46

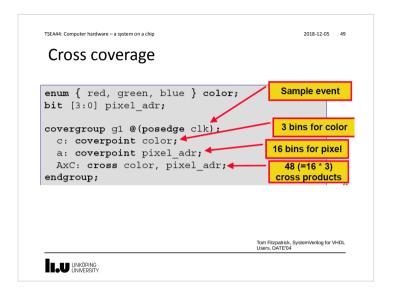

## Coverage

- Code coverage (code profiling)

- reflects how thorough the HDL code was exercised

- Functional Coverage (histogram binning)

- perceives the design from a user's or a system point of view

- Have you covered all of your typical scenarios?

- Error cases? Corner cases? Protocols?

- · Functional coverage also allows relationships,

- "OK, I've covered every state in my state machine, but did I ever have an interrupt at the same time? When the input buffer was full, did I have all types of packets injected? Did I ever inject two errorneous packets in a row?"

LINKÖPING UNIVERSITY

```

TSEA44: Computer hardware = a system on a chin

2018-12-04 47

memory mem = new();

Coverage

// Task to drive values

task drive (input [7:0] a, input [7:0] d,

// DUT With Coverage

#5 en <= 1;

addr <= a;

logic [7:0] addr;

data <= d;

logic [7:0] data;

par <= ^d:

logic

par;

$display ("@%2tns Address :%d data %x,

logic

rw;

rw %x, parity %x",

$time,a,d,r, ^d);

// Coverage Group

covergroup memory @ (posedge en);

data <= 0;

address: coverpoint addr {

bins low = {0,50};

bins med = {51,150};

par <= 0;

addr <= 0;

rw <= 0;

bins high = {151,255};

endtask

parity : coverpoint par {

// Testvector generation

bins even = {0};

bins odd = {1};

repeat (10) begin

read write : coverpoint rw {

drive (Srandom, Srandom, Srandom):

bins read = {0};

bins write = {1};

#10 $finish;

end

endgroup

LINKÖPING

UNIVERSITY

```

```

TSEA44: Computer hardware - a system on a chip

2018-12-04 48

Report

# @ 5ns Address : 36 data 81, rw 1, parity 0

# @15ns Address : 99 data 0d, rw 1, parity 1

# @25ns Address :101 data 12, rw 1, parity 0

# @35ns Address: 13 data 76, rw 1, parity 1

ModelSim says:

@GOVERGROUP:COVERAGE3, rw 0, parity 0

# @Covergroupss :143 data f2, rw 0, parity 1 Metric

At Least

Goal/ Status

TYPE /simple_coverage/memory

44.4%

100 Uncovered

Coverpoint memory::address

33.3%

100 Uncovered

covered/total bins:

hin low

1 Covered

1 ZERO

bin med

1 ZERO

50.0%

Coverpoint memory::parity

100 Uncovered

Report

covered/total bins:

1 Covered

bin even

generator:

bin odd

1 ZFRO

Coverpoint memory::read write

50.0%

100 Uncovered

covered/total bins:

1 Covered

hin write

1 7FRO

TOTAL COVERGROUP COVERAGE: 44.4% COVERGROUP TYPES: 1

LINKÖPING

UNIVERSITY

```

```

TSEA44: Computer hardware – a system on a chip

2018-12-05 51

Constrained randomization

program rc;

class Bus;

rand bit[31:0] addr;

rand bit[31:0] data;

constraint word align {addr[1:0] == 2'b0;

addr[31:24] == 8'h99;}

endclass // Bus

initial begin

Bus bus = new;

repeat (50) begin

if ( bus.randomize() == 1 )

$display ("addr = 0x%h data = 0x%h\n",

bus.addr, bus.data);

$display ("Randomization failed.\n");

end

end

endprogram // rc

LINKÖPING

UNIVERSITY

```

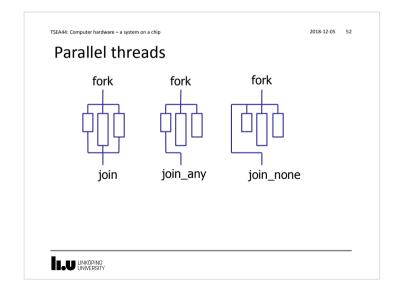

```

An example-sketch

• WB arbitration test

- Instantiate 4 wishbone_tasks

program tester2();

initial begin

fork

begin // 2

for (int 1; i<100; i++)

jpeg_top_tb.wb2.m_write(32'h100, 32'h0);

end

begin // 6

for (int i; i<100; i++)

jpeg_top_tb.wb6.m_write(32'h20000000, result);

end

end

end

end

endprogram

LUU LINKOPING

UNIVERSITY

2018-12-05 53

**Till **Monitor**

**LOU LINKOPING**

LINKOPING

UNIVERSITY

2018-12-05 53

**Till **Monitor**

**LOU LINKOPING**

**LOU LINKOPING**

```