# TSEA44: Computer hardware – a system on a chip

Lecture 6: Design for FPGAs

Material by Andreas Ehliar

#

| <b>т</b> |                                                |                   |

|----------|------------------------------------------------|-------------------|

| Tod      | ау                                             |                   |

| • In     | fluence of goal hardware on archite            | cture and code s  |

| • M      | otivation                                      |                   |

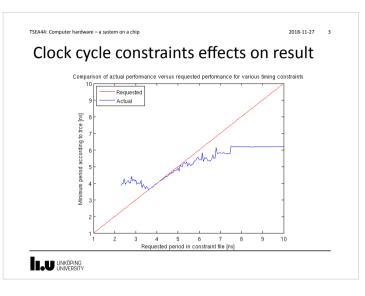

| -        | Clock speed                                    |                   |

| -        | Area                                           |                   |

| -        | Power                                          |                   |

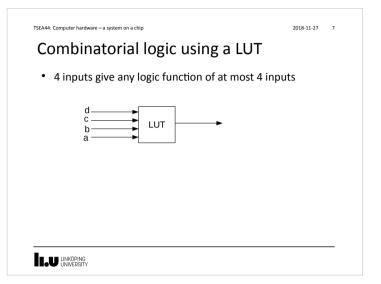

| • Ta     | rget FPGA architecture: Xilinx FPGA            | with 4-input LUT  |

| -        | Same as VirtexII used in lab                   |                   |

| _        | Later generations use 6-input LUTs can be used | s, but same ideas |

# To get the best out of the FPGA

2018-11-27 4

- Understand the architecture

- Use suitable descriptions

- Use available tools to extract implementation information

- FPGA editor

TSEA44: Computer hardware – a system on a chip

- Floorplanner

- Planahead

- Datasheets

- Timing reports

#### TSEA44: Computer hardware – a system on a chip

2018-11-27 33

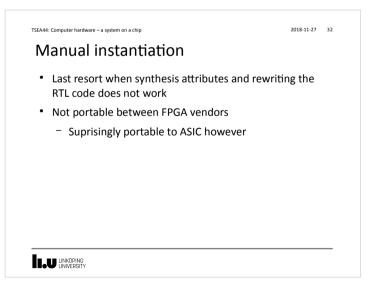

# Manual instantiation of flip-flops

- Allows you to ensure that the correct signals are corrected to the D, CE, and SR inputs

- XST (Xilinx own synthesis tool, not used in the lab) often seem to select the wrong input for SR

- Background: SR input is quite slow compared to D input

- Can sometimes be avoided by rewriting the code or using synthesis attributes

- Often easier to just instantiate flip-flop primitives directly

##

TSEA44: Computer hardware - a system on a chip

2018-11-27

34

Manual instantiation of Memories and

DSP Blocks

• Well documented in various application notes

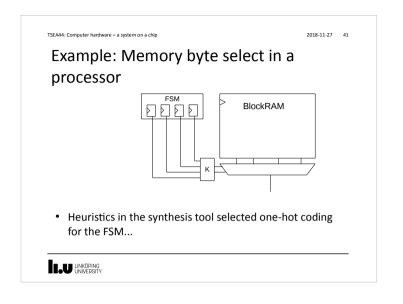

#### TSEA44: Computer hardware – a system on a chip

2018-11-27 35

## Synthesis attributes

- A convenient way to force the synthesis tool to do what you mean

- In VHDL:

attribute keep : string; attribute keep of mysignal: signal is "TRUE"

- In Verilog:

- (\* KEEP = "TRUE" \*) wire mysignal;

- Note: Synthesis attributes discussed here are for XST, not Precision!

- (Read the Precision manual)

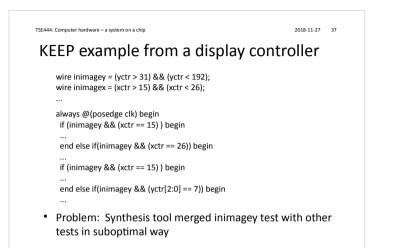

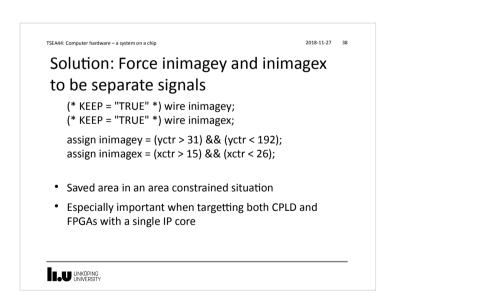

# TSEA44: Computer hardware - a system on a chip 2018-11-27 36 Synthesis attribute KEEP • • Preserves the selected signal • • Use case: •

- The synthesis tool makes a bad optimization decision.

- By using KEEP you can ensure that a certain signal is not hidden inside a LUT and hence guide the optimization process

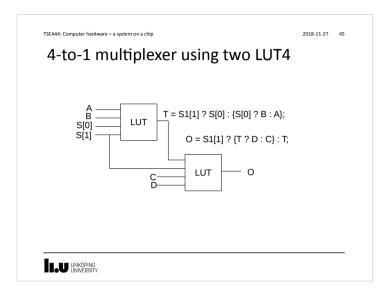

| TSEA44: Computer hardware – a system on a chip | 2018-11-27 | 44 |

|------------------------------------------------|------------|----|

| 4-to-1 multiplexer using two LUT4              |            |    |

|                                                |            |    |

|                                                |            |    |

|                                                |            |    |

|                                                |            |    |

|                                                |            |    |

|                                                |            |    |

|                                                |            |    |

|                                                |            |    |

|                                                |            |    |

|                                                |            |    |