# TSEA44: Computer hardware – a system on a chip

Lecture 4: The lab system and JPEG encoding

#

####

2018-11-14 3

2018-11-14

#### Practical issues

- Forming groups

- Require pass on lab0

- Send email to me (to get shared folder access)

- Try to form groups of 3

- Groups of 1 to 3 is expected, 3 is prefered, 2 is ok, 1 is accepted

- See exam webpage of course for list of students

TSEA44: Computer hardware - a system on a chip

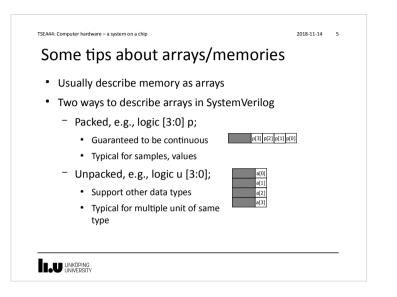

### Some tips about arrays/memories

- FPGA memories can be created using

- Flipflops; asynchronous read, synchronous write

- Distributed using LUTs; asynchronous read, synchronous write, 16x1 each

- BRAMs; synchronous read, synchronous write, 512x32, 1024x16 ....

- Memories can be designed

- Using templates (BRAMs)

- Inferred (distributed)

####

# 2018-11-14 22:04

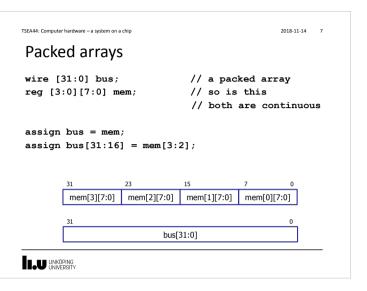

| ISEA44: Computer hardware – a system on a chip | 2018-11-14  |

|------------------------------------------------|-------------|

| Unpacked arrays                                |             |

| wire [31:0] bus;                               |             |

| reg [7:0] mem [0:3]; // a 4-byte               | e memory    |

|                                                |             |

| assign bus[31:24] = mem[3];                    | 7 0         |

|                                                | mem[0][7:0] |

|                                                | mem[1][7:0] |

|                                                | mem[2][7:0] |

|                                                | mem[3][7:0] |

|                                                |             |

| 31                                             | 0           |

| bus[31:0]                                      |             |

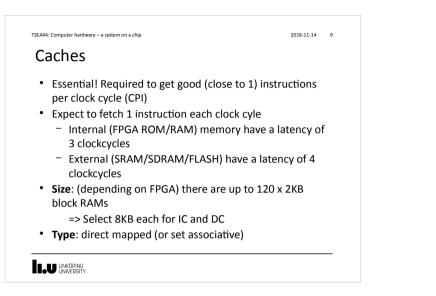

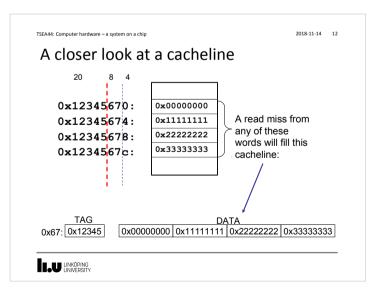

| Cach    | e policy                               |                                         |   |

|---------|----------------------------------------|-----------------------------------------|---|

| cach    | c policy                               |                                         |   |

| achelii | ne = 4 words = 16 Byte                 | S                                       |   |

| Instr   | uction cache                           |                                         |   |

|         | hit                                    | miss                                    |   |

| read    | read from cache                        | fill (replace) cacheline from<br>memory |   |

| Data c  | ache                                   |                                         | - |

|         | hit                                    | miss                                    | ] |

| read    | read from cache                        | fill (replace) cacheline from memory    |   |

| write   | write to cache<br>write thru to memory | write to memory only                    |   |

<page-header><page-header><page-header><page-header><section-header><list-item><list-item><section-header>

| Accelerator inter                                                                                   | facing, cont.                                                         |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| • Common for the accer<br>data to receive, proce                                                    | elerator to have large amount of<br>ess, and return                   |

| <ul> <li>Simplest approach: U<br/>data<br/>Mem-&gt;CPU<br/>CPU-&gt; Accelerator<br/>wait</li> </ul> | se CPU to feed accelerator with<br>Feed data to accelerator, uses CPU |

| Accelerator->CPU<br>CPU -> Mem                                                                      | Return data from accelerator, uses CPU                                |

| TSEA44: Computer hardware – a system on a chip                              | 2018-11-                                                                                                     | 14 20       |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------|

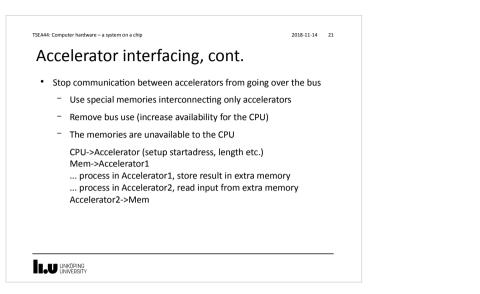

| Accelerator inter                                                           | facing, cont.                                                                                                |             |

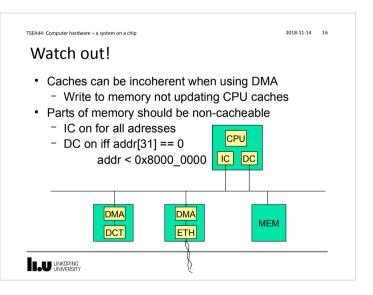

| <ul> <li>Want to reduce load on C<br/>by itself: DMA! (Direct Me</li> </ul> | PU: let the accelerator do the data mov emory Access)                                                        | 25          |

| CPU setups DMA con                                                          | troller in accelerator (startadress, length                                                                  | .)          |

| Mem -> Accelerator<br>processing                                            | Feed data to accelerator, CPU do other                                                                       | things      |

| Accelerator->Mem                                                            | Return data from accelerator, CPU do c                                                                       | ther things |

| Even worse if                                                               | tor and CPU compete for the bus<br>a number of accelerators work on<br>nce (Accelerator1 -> Accelerator2 ->) |             |

|                                                                             |                                                                                                              |             |

# 2018-11-14 22:04

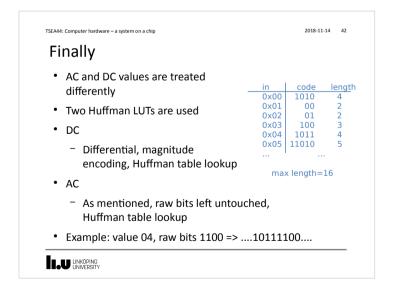

| 1agnitude er  | icoding (DC    | oniy)        |  |

|---------------|----------------|--------------|--|

| Encoded value | DC Value       | Range        |  |

| 0             | 0              |              |  |

| 1             | [-1]           | [1]          |  |

| 2             | [-3, -2]       | [2, 3]       |  |

| 3             | [-7, -4]       | [4, 7]       |  |

| 4             | [-15, -8]      | [8, 15]      |  |

| 5             | [-31, -16]     | [16, 31]     |  |

| 6             | [-63, -32]     | [32, 63]     |  |

| 7             | [-127, -64]    | [64, 127]    |  |

| 8             | [-255, -128]   | [128, 255]   |  |

| 9             | [-511, -256]   | [256, 511]   |  |

| 10            | [-1023, -512]  | [512, 1023]  |  |

| 11            | [-2047, -1024] | [1024, 2047] |  |