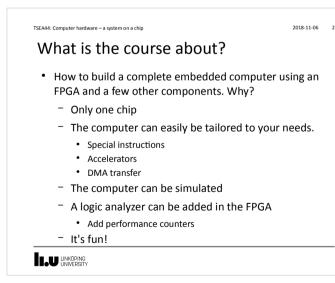

# TSEA44: Computer hardware – a system on a chip

Kent Palmkvist, Erik Bertilsson http://www.isy.liu.se/edu/kurs/TSEA44 Based on slides by Andreas Ehliar

##

#### TSEA44: Computer hardware – a system on a chip

2018-11-06 3

## Prerequisites (expected knowledge!)

- Digital logic design. You will design both a data path and a control unit for an accelerator.

- Binary arithmetic. Signed/unsigned numbers.

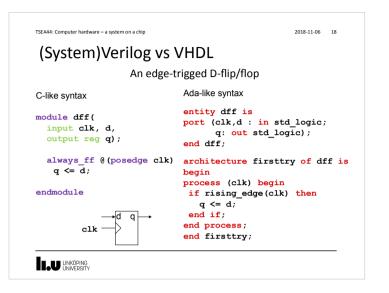

- VHDL or Verilog. SystemVerilog (SV) is the language used in the course.

- Computer Architecture. It is extremely important to understand how a CPU executes code. You will also design part of a DMA-controller. Bus cycles are central.

- ASM and C programming. Most of the programming is done in C, with a few cases of inline asm.

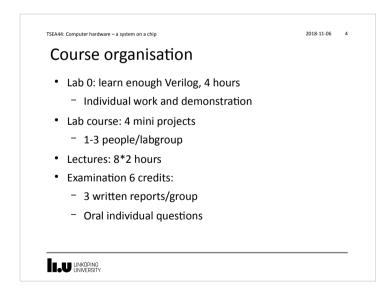

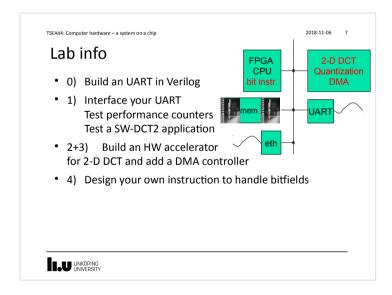

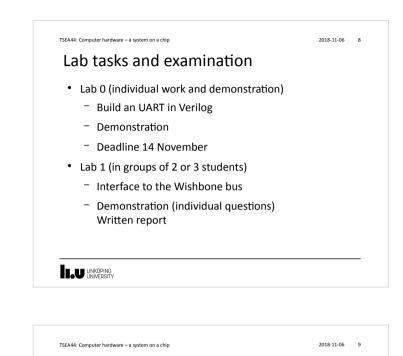

### Lab tasks and examination, cont.

- Lab 2+3

- Design a JPEG accelerator + DMA

- Demonstration (with individual questions)

Written report

- Lab 4

- Custom Instruction

- Demonstration (with individual questions)

Written report

2018-11-06 10

### Written report requirements

- A readable short report typically consisting of

- Introduction

- Design, where you explain with text and diagrams how your design works

- Results, that you have measured

- Conclusions

- Appendix: All Verilog and C code with comments!

###

#### TSEA44: Computer hardware – a system on a chip

#### 2018-11-06 11

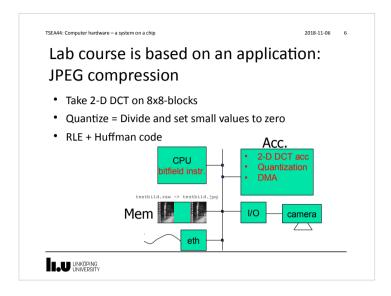

## Competition – fastest JPEG compression

- An unaccelerated JPEG compression (using jpegfiles) takes roughly 13.0 Mcycles (@ 25MHz) ~ 2 FPS (Frames Per Second)

- Our record: ~ 100 000 cycles (everything in hardware)

- Goal: Highest framrate. Exception: At over 25 FPS, the smallest implementation wins

- Deadline: 21/12 2018

wunderb.jpg 320 x 240

####

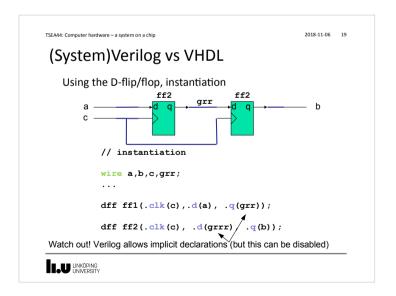

- The course uses SystemVerilog

- SystemVerilog is easy to learn if you know VHDL/C

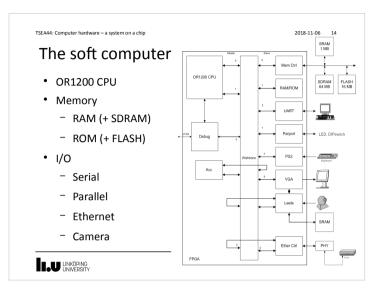

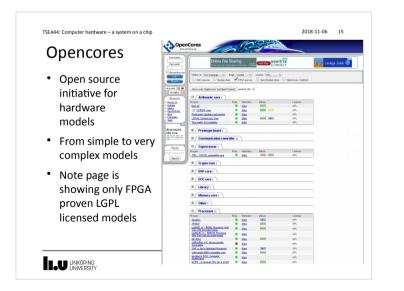

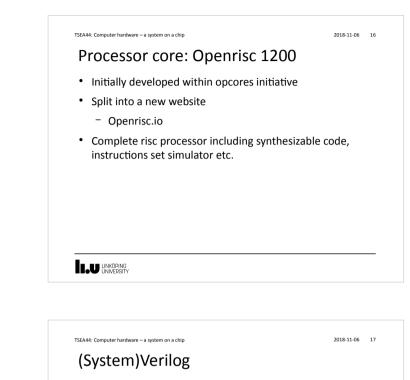

- Our soft computer (80% downloaded from OpenCores) is written in Verilog

- It is possible to use both languages in a design

- You need to understand parts of the computer

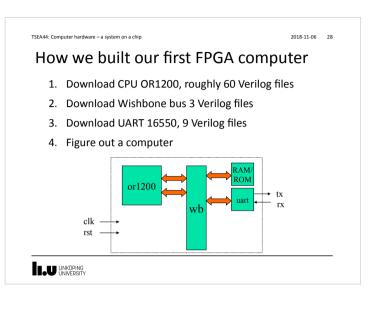

| TSEA44: Computer hardware - a system on a chip 2018-11-06 29                                                                 |

|------------------------------------------------------------------------------------------------------------------------------|

| How we built our first FPGA computer                                                                                         |

| 5. Write top file ("wire wrap in emacs")                                                                                     |

| Size 35 kB in Verilog, 13 kB in SV<br>(Verilog does not have struct)                                                         |

| <pre>module myfirstcomputer(clk,rst,rx,tx)     input clk,rst,rx;     output tx;</pre>                                        |

| <pre>wishbone Mx[0:1], Sx[0:1];</pre>                                                                                        |

| <pre>or1200cpu cpu0(.iwb(Mx[0]),); wb_conbus wb0(clk, rst, Mx, Sx); romram rom0(Sx[1]); uart uart0(Sx[0],); end module</pre> |

|                                                                                                                              |

| Synthesis result |      |       |      |      |     |        |                   |            |     |

|------------------|------|-------|------|------|-----|--------|-------------------|------------|-----|

| Synthe           |      | JIC   |      | arc  |     |        |                   |            |     |

| <br> Module      | -+-  | LUT   | -+-  | FF   | -+- | RAMB16 | +<br>  MULT_18x18 | +<br>  IOB |     |

| <br>  /          | -+-  | 64    | -+-  |      | -+- |        | +<br>             | +<br>  216 | 1   |

| cpu              | i.   | 5029  | i    | 1345 | i   | 12     | 4                 | i.         | i.  |

| dvga             | ÷.   | 813   | i.   | 755  | i.  | 4      | i                 | i          | i i |

| eth3             | i.   | 3022  | i    | 2337 | i   | 4      | Ì                 | i.         | i.  |

| 0pqi             |      |       |      | 900  |     |        | I 13              | i          | i   |

| leela            | i.   | 685   | i    | 552  | i   | 4      | 2                 | i          | i i |

| pia              |      | 2     | T    | 5    | T   |        | 1                 | 1          | 1   |

| pkmc mc          |      | 218   | T    | 122  | T   |        | 1                 | 1          | 1   |

| rom0             |      | 82    | T    | 3    | T   | 12     | 1                 | 1          | 1   |

| sys sig gen      |      |       | T    | 6    | T   |        | 1                 | 1          | 1   |

| uart2            | 1    | 825   | T    | 346  | T   |        | I                 | 1          | 1   |

| wb_conbus        | Т    | 616   |      | 11   | I   |        | I                 | I.         | L   |

| <br> Total       | -+-  | 13559 |      | 6382 | i   |        | 19                | 216        | +   |

| <br> Available   | +-+- | 46080 | +-++ |      |     |        | +                 | +<br>+ 912 | +   |

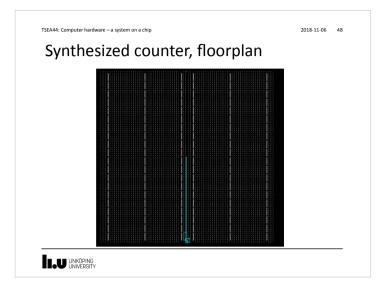

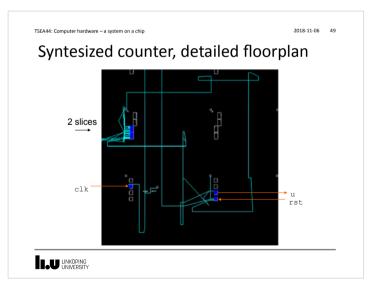

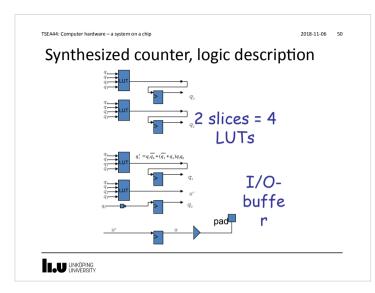

| TSEA44: Computer hardware – a system on a chip | 2018-11-06 | 47 |

|------------------------------------------------|------------|----|

| counter                                        |            |    |

| module dec(                                    |            |    |

| input clk,rst                                  |            |    |

| output u);                                     |            |    |

| reg u;                                         |            |    |

| reg [3:0] q;                                   |            |    |

| always_ff @(posedge clk or posedge rst)        |            |    |

| if (rst)                                       |            |    |

| q <= 4 h0;                                     |            |    |

| else if $(q == 9)$                             |            |    |

| q <= 4'h0;                                     |            |    |

| else                                           |            |    |

| q <= q+1;                                      |            |    |

| always_ff @(posedge clk)                       |            |    |

| if (q == 9)                                    |            |    |

| u <= 1'b1;                                     |            |    |

| else                                           |            |    |

| u <= 1'b0;                                     |            |    |

| endmodule                                      |            |    |