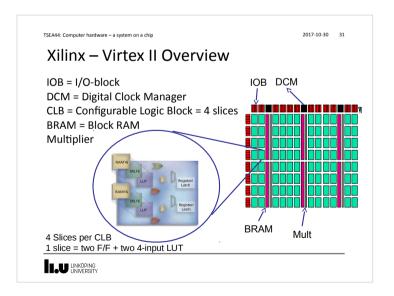

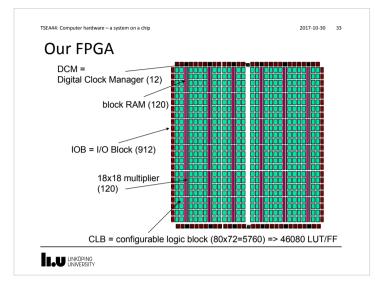

# TSEA44: Computer hardware – a system on a chip

Kent Palmkvist, Erik Bertilsson http://www.isy.liu.se/edu/kurs/TSEA44 Based on slides by Andreas Ehliar

##

#### TSEA44: Computer hardware – a system on a chip

#### Prerequisites (expected knowledge!)

• Digital logic design. You will design both a data path and a control unit for an accelerator.

2017-10-30

- · Binary arithmetic. Signed/unsigned numbers.

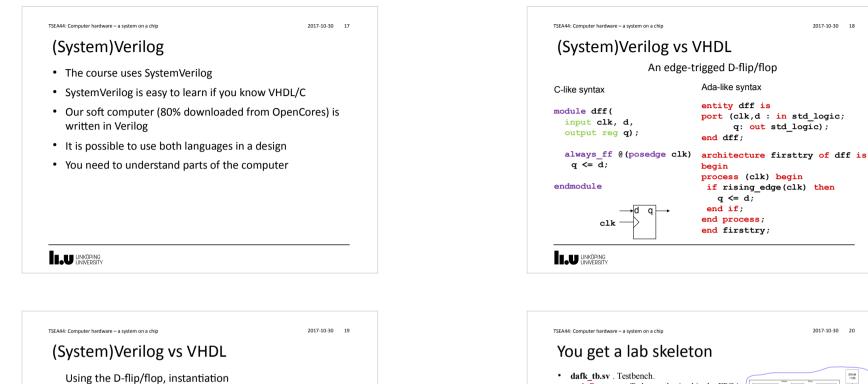

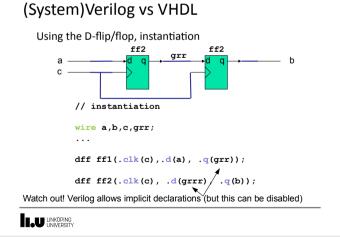

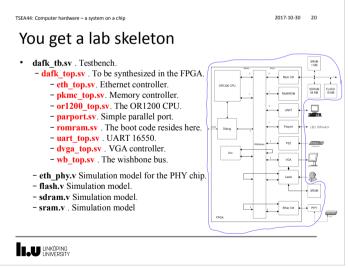

- VHDL or Verilog. SystemVerilog (SV) is the language used in the course.

- Computer Architecture. It is extremely important to understand how a CPU executes code. You will also design part of a DMA-controller. Bus cycles are central.

- ASM and C programming. Most of the programming is done in C, with a few cases of inline asm.

####

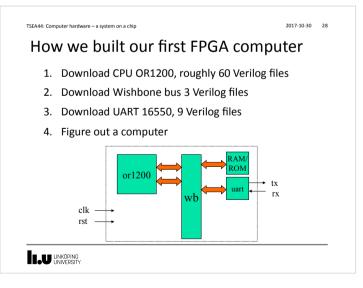

## What is the course about?

• How to build a complete embedded computer using an FPGA and a few other components. Why?

2017-10-30 2

2017-10-30 4

- Only one chip

TSEA44: Computer bardware = a system on a chin

- The computer can easily be tailored to your needs.

- Special instructions

- Accelerators

- DMA transfer

- The computer can be simulated

- A logic analyzer can be added in the FPGA

- Add performance counters

- It's fun!

TSEA44: Computer hardware - a system on a chip

## Course organisation

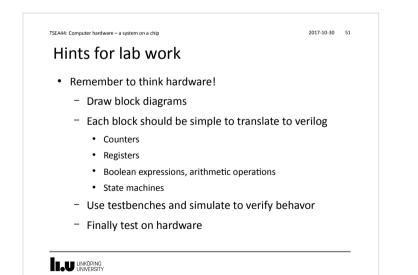

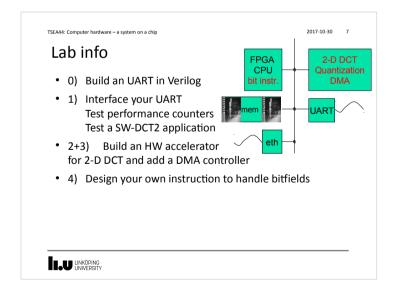

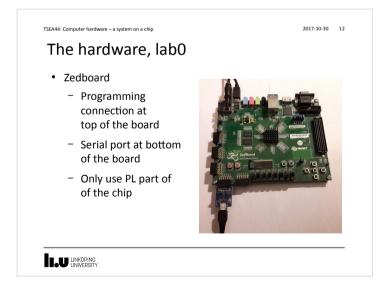

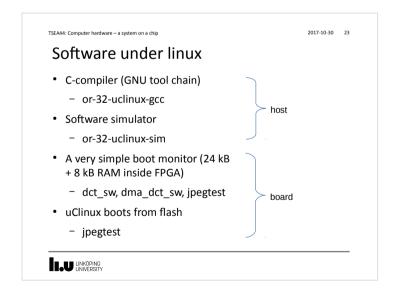

- Lab 0: learn enough Verilog, 4 hours

- Individual work and demonstration

- · Lab course: 4 mini projects

- 6 groups \* 3 students in the lab

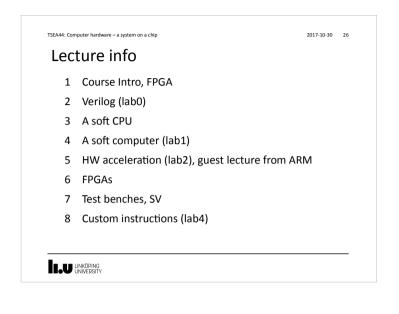

- Lectures: 8\*2 hours

- 1 guest lecture from ARM

- Examination 6 credits:

- 3 written reports/group

- Oral individual questions

####

|     | ab 0 (individual work and demonstration)                                         |  |

|-----|----------------------------------------------------------------------------------|--|

|     | <ul> <li>Build an UART in Verilog</li> <li>Demonstration</li> </ul>              |  |

|     | <ul> <li>Deadline 10 November</li> </ul>                                         |  |

| • [ | ab 1 (in groups of 2 or 3 students)                                              |  |

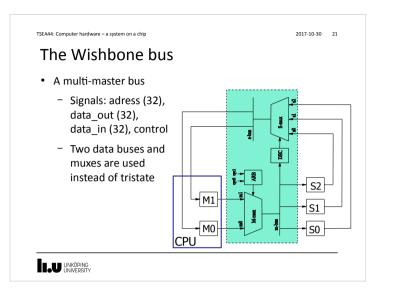

|     | <ul> <li>Interface to the Wishbone bus</li> </ul>                                |  |

|     | <ul> <li>Demonstration (individual questions)</li> <li>Written report</li> </ul> |  |

|     |                                                                                  |  |

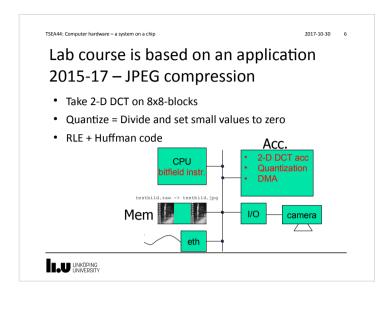

# TSEX44: Computer hardware – a system on a chip 2017-10-30 Lab tasks and examination, cont. • Lab 2+3

- Design a JPEG accelerator + DMA

- Demonstration (with individual questions) Written report

- Lab 4

- Custom Instruction

- Demonstration (with individual questions) Written report

####

#### TSEA44: Computer hardware – a system on a chip

#### 2017-10-30 11

9

## Competition – fastest JPEG compression

- An unaccelerated JPEG compression (using jpegfiles) takes roughly 13.0 Mcycles (@ 25MHz) ~ 2 FPS (Frames Per Second)

- Our record: ~ 100 000 cycles (everything in hardware)

- Goal: Highest framrate. Exception: At over 25 FPS, the smallest implementation wins

- Deadline: 19/12 2017

wunderb.jpg 320 x 240

####

#### TSEA44: Computer hardware – a system on a chip

2017-10-30 10

### Written report requirements

- A readable short report typically consisting of

- Introduction

- Design, where you explain with text and diagrams how your design works

- Results, that you have measured

- Conclusions

- Appendix: All Verilog and C code with comments!

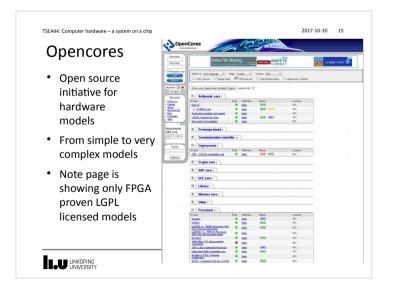

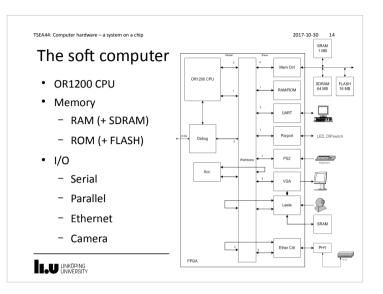

| TSEA44: Computer hardware – a system on a chip                                                                                       | 2017-10-30 | 16 |

|--------------------------------------------------------------------------------------------------------------------------------------|------------|----|

| Processor core: Openrisc 1200                                                                                                        |            |    |

| <ul> <li>Initially developed within opcores initiative</li> <li>Split into a new website <ul> <li>Openrisc.io</li> </ul> </li> </ul> |            |    |

| <ul> <li>Complete risc processor including synthesizal<br/>instructions set simulator etc.</li> </ul>                                | ble code,  |    |

|                                                                                                                                      |            | _  |

|                                                                                                                                      |            |    |

2017-10-30 18

| Booting<br>uClinux | uClinux/OR32<br>Flat model support (C) 1998,1999 Kenneth Albanowski, D. Jeff Dionne<br>Calibrating delay loop ok - 2.00 BogoMTPS<br>Memory available: 53000x/63235k RAM, 0k/0k ROM (667892k kernel data, 2182k co<br>Swansee University Computer Society NET3.035 for Linux 2.0 |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ueimux             | NET3: Unix domain sockets 0.13 for Linux NET3.035.<br>Swansea University Computer Society TCP/IP for NET3.034<br>IP Protocols: ICMP, UDP, TCP<br>uClinux version 2.0.38.lpre3 (olles%kotte) (gcc version 3.2.3) #180 Sat Sep 1                                                  |

|                    | 9:01:55 CEST 2004<br>Serial driver version 4.13pl with no serial options enabled<br>ttys00 at 0x90000000 (irq = 2) is a 16550A<br>Ramdisk driver initialized : 16 ramdisks of 2048K size                                                                                        |

|                    | Blkmem copyright 1998,1999 D. Jeff Dionne<br>Blkmem copyright 1998 Kenneth Albanowski<br>Blkmem O disk images:                                                                                                                                                                  |

|                    | loop: registered device at major 7<br>eth0: Open Ethernet Core Version 1.0<br>RAMDISK: Romfs filesystem found at block 0<br>RAMDISK: Loading 1606 blocks into ram disk done.                                                                                                    |

|                    | VFS: Mounted root (romfs filesystem).<br>Executing shell<br>Shell invoked to run file: /etc/rc                                                                                                                                                                                  |

|                    | Command: #!/bin/sh<br>Command: setenv PATH /bin:/usr/bin<br>Command: hostname bender                                                                                                                                                                                            |

|                    | Command: #<br>Command: mount -t proc none /proc<br>Nore of the same<br>Command: #                                                                                                                                                                                               |

|                    | Command: # start web server<br>Command: /sbin/boa -d &<br>[12]                                                                                                                                                                                                                  |

| Synthesis result |        |       |         |        |    |     |                                         |            |   |

|------------------|--------|-------|---------|--------|----|-----|-----------------------------------------|------------|---|

| Synthe           | 31     | 310   | 3       | un     |    |     |                                         |            |   |

| <br> Module      | -+     | LUT   | -+-     | <br>FF |    |     | +<br>  MULT 18x18                       |            | 1 |

|                  | -+     |       | -+-     |        | -+ |     | +                                       | +          | I |

| /                | 1      | 64    |         |        | 1  |     | l i i i i i i i i i i i i i i i i i i i | 216        | 1 |

| cpu              | 1      | 5029  |         | 1345   |    | 12  | 4                                       | I          | 1 |

| dvga             | 1      | 813   |         | 755    |    | 4   | l                                       | 1          | 1 |

| eth3             | 1      | 3022  |         | 2337   |    | 4   | L                                       | I          | 1 |

| jpg0             | 1      | 2203  | 1       | 900    | 1  | 2   | 13                                      | 1          | 1 |

| leela            | 1      | 685   |         | 552    |    | 4   | 2                                       | I          | 1 |

| pia              | 1      | 2     | 1       | 5      | 1  |     | l .                                     | 1          | 1 |

| pkmc mc          | 1      | 218   | T       | 122    | 1  |     | I                                       | L          | 1 |

| rom0             | 1      | 82    | T       | 3      | 1  | 12  | I                                       | L          | 1 |

| sys sig gen      | 1      |       | T       | 6      | 1  |     | I                                       | L          | 1 |

| uart2            | 1      | 825   |         | 346    |    |     | L                                       | I          | 1 |

| wb_conbus        |        | 616   |         | 11     | Т  |     | I                                       | 1          | I |

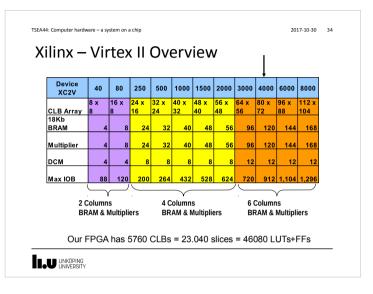

| <br> Total       | -+<br> | 13559 | -+-<br> |        |    | 38  | +<br>I 19                               | +<br>  216 | + |

| <br> Available   | +-+    | 46080 | +-+++   |        |    | 120 |                                         | +          | + |