# TSEA44: Computer hardware – a system on a chip

Lecture 4: Lab2 intro, Pitfalls when coding, Guest lecture from ARM Sweden AB.

TSEA44: Computer hardware – a system on a chip

#### Agenda

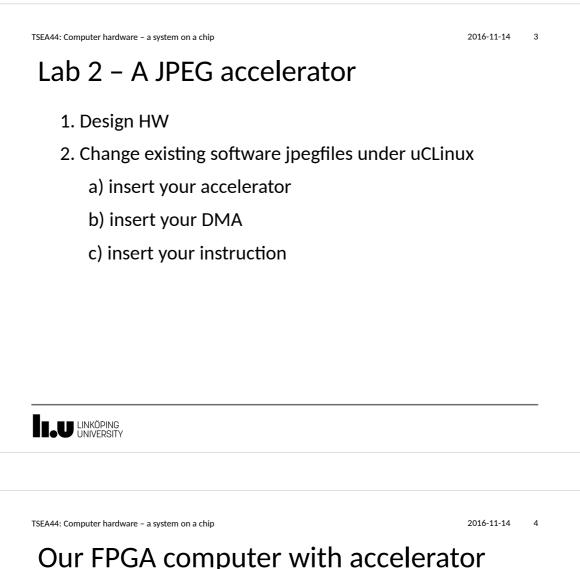

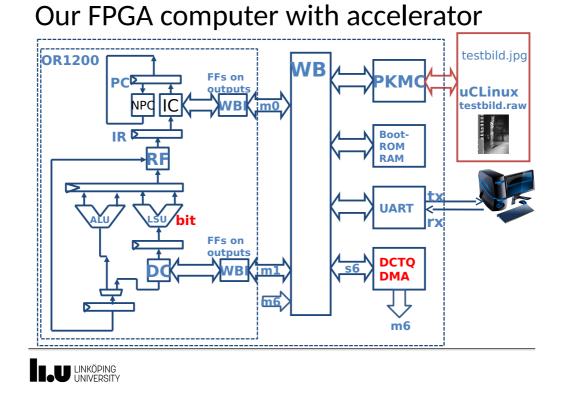

- Lab2 introduction

- Pitfalls when writing code

- Guest lecture from ARM Sweden AB

2016-11-14

TSEA44: Computer hardware - a system on a chip

#### DCT module

- Given to you

- 1D DCT

- 8 in ports (12 bits), 8 out ports (16 bits)

- Fix point arithmetic

- Straightforward implementation of Loeffler's algorithm

2016-11-14

2016-11-14

12

```

TSEA44: Computer hardware – a system on a chip

```

#### **Block RAM**

- Different timing

- "Normal" SRAM

- Asynchronous read

- Asynchronous write

- Block RAM in Virtex 2

- Synchronous read

- Synchronous write

```

TSEA44: Computer hardware - a system on a chip

2016-11-14

19

wb_tasks.sv

module wishbone_tasks(wishbone.master wb);

int result = 0;

reg oldack;

reg [31:0] olddat;

always @(posedge wb.clk) begin

oldack <= wb.ack;</pre>

olddat <= wb.dat_i;</pre>

end

task m_read(input [31:0] adr, output logic [31:0] data);

begin

@(posedge wb.clk);

wb.adr <= adr;

wb.stb <= 1'b1;

wb.we <= 1'b0;

wb.stb <= 1'b0;

wb.cyc <= 1'b1;

wb.we <= 1'b0;

wb.cyc <= 1'b0;

wb.sel <= 4'hf;

wb.sel <= 4'h0;

@(posedge wb.clk);

data = olddat;

#1;

while (!oldack) begin

end

endtask // m_read

@(posedge wb.clk);

#1;

endmodule // wishbone_tasks

end

```

```

<page-header><page-header><page-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

```

- Not so likely:

- You have triggered a bug in the CAD tools

LINKÖPING UNIVERSITY

TSEA44: Computer hardware - a system on a chip

## Clock domain crossing

- Why do we need synchronous designs?

- Race conditions

- Metastability

- Crossing clock domains

- (Avoid if possible)

- Using handshakes

- Using asynchronous FIFOs

- Your own solution

- (Only if you like debugging systems where bugs cannot be deterministically reproduced...)

- Do not forget that the reset signal has to be passed to each clock domain!

28

2016-11-14

```

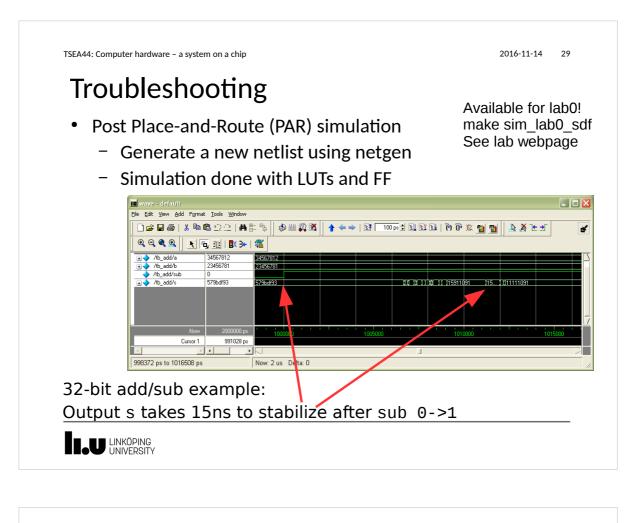

TSEA44: Computer hardware - a system on a chip

2016-11-14

30

Testbenches that work with PAR netlists

Avoid violating setup and hold times of flipflops

- Delay test values

Test results at the end of the clock cycle

•

Test values at

initial begin // Test adder

the clock cycle

@(posedge clk);

transition. before

#4; // delay after clockedge

updates moved

a <= 5;

b <= 3;

on from input

@(posedge clk);

flipflops

if (result != 8) begin

$display("Adder fail");

$stop;

end

end

```

2016-11-14 31

TSEA44: Computer hardware - a system on a chip

### Simulation ok, but still not working?

- Add measurement logic to the FPGA Design

- Use switches and LEDs

- Chipscope/Signaltap

- Add logic analyzer function to the FPGA design

- Store sampels in blockRAM or similar

- Communicate with PC over JTAG

- Warning!

- Many people think signaltap/chipscope replace simulation. It does not! Better to spend time writing better testbench

www.liu.se