# Laboratory manual for TSEA44

Olle Seger, Per Karlström, Andreas Ehliar, Kent Palmkvist Computer Engineering Department of Electrical Engineering Linköping University, S-581 83 Linköping, Sweden Email: Kent.Palmkvist@liu.se

November 4, 2019

# Contents

| 1 | The | system                                | 7  |

|---|-----|---------------------------------------|----|

|   | 1.1 | Introduction                          | 7  |

|   | 1.2 | Hardware                              | 7  |

|   |     | 1.2.1 Virtex-II Development board     | 7  |

|   |     | 1.2.2 Communication/Memory Module     | 7  |

|   |     | 1.2.3 Virtex-II 4000 FPGA             | 9  |

|   | 1.3 | Open RISC 1                           | 0  |

|   |     | 1.3.1 Top Design                      | 0  |

|   |     | 1.3.2 Structure of the Verilog code   | 1  |

|   |     | 1.3.3 OR1200 CPU                      | 3  |

|   |     | 1.3.4 The Wishbone Interconnect Bus   | 4  |

|   |     | 1.3.5 Memory Controller               | 5  |

|   |     |                                       | 5  |

|   |     | 1.3.7 VGA Controller                  | 6  |

|   |     | 1.3.8 UART                            | 6  |

|   | 1.4 | Software                              | 6  |

|   |     | 1.4.1 Memory map                      | 6  |

|   |     | 1.4.2 A simple boot monitor           | 7  |

|   |     | 1.4.3 The simulator or 32-uclinux-sim | 20 |

|   |     | 1.4.4 $\mu$ Clinux                    | 21 |

| 2 | Lab | 8                                     | 25 |

|   | 2.1 | Introduction                          | 25 |

|   | 2.2 | A simple UART                         | 25 |

|   |     | 2.2.1 General                         | 25 |

|   |     | 2.2.2 The RS232 protocol              | 26 |

|   |     | 2.2.3 The zedboard hardware           | 26 |

|   |     | 2.2.4 A simple testbench              | 27 |

|   | 2.3 | Exercises                             | 29 |

|   |     | 2.3.1 Commands                        | 29 |

|   |     | 2.3.2 A User Constraint File          | 30 |

|   | 2.4 | gtkterm usage                         | 31 |

| 3 | Lab |                                       | 33 |

|   | 3.1 |                                       | 33 |

|   | 3.2 | Some Basic Facts on the Wishbone Bus  | 34 |

# CONTENTS

|   |                | 3.2.1 A Wishbone Interconnect                           | 35       |

|---|----------------|---------------------------------------------------------|----------|

|   | 3.3            | A Simple Computer                                       | 36       |

|   |                | 3.3.1 General                                           | 36       |

|   |                | 3.3.2 A Wishbone Interface for the UART                 | 36       |

|   |                | 3.3.3 The Monitor                                       | 38       |

|   |                | 3.3.4 Test Your Design                                  | 39       |

|   | 3.4            | A Benchmark Program                                     | 40       |

|   |                | 3.4.1 JPEG Compression                                  | 40       |

|   |                | 3.4.2 Integer DCT                                       | 40       |

|   |                | 3.4.3 The Test Program dct_sw                           | 42       |

|   |                | 3.4.4 A Test Example                                    | 42       |

|   | 3.5            | Design a Performance Counter Module                     | 42       |

|   | 3.6            | Useful Commands                                         | 44       |

|   |                | 3.6.1 Synthesis Reports                                 | 44       |

|   | 3.7            | How to get Started Writing/Executing C Programs         | 45       |

|   |                | 3.7.1 A Note on Volatile                                | 45       |

|   |                | 3.7.2 What to Include in the Lab Report                 | 46       |

|   |                |                                                         |          |

| 4 |                | task 2 - Design a JPEG accelerator                      | 47       |

|   | 4.1            | The lab system                                          | 47       |

|   | 4.2            | Proposed architecture                                   | 47       |

|   |                | 4.2.1 Block RAMs in VirtexII                            | 48       |

|   |                | 4.2.2 Distributed RAMs                                  | 49       |

|   |                | 4.2.3 The transpose memory                              | 50       |

|   |                | 4.2.4 WB memory map                                     | 50       |

|   | 4.3            | Introduction to $\mu$ Clinux                            | 51       |

|   |                | 4.3.1 Compiling an application to $\mu$ Clinux          | 51       |

|   |                | 4.3.2 Starting the TFTP server                          | 51       |

|   |                | 4.3.3 Downloading applications via TFTP                 | 52       |

|   | 4.4            | Introduction to jpegfiles                               | 52       |

|   |                | 4.4.1 Important files in the lab skeleton               | 53       |

|   |                | 4.4.2 The jpegtest application                          | 54       |

|   |                | 4.4.3 The webcam application                            | 54       |

|   | 4.5            | Timestamps                                              | 54       |

|   | 4.6            | Quantization                                            | 55       |

|   |                | 4.6.1 General                                           | 55       |

|   |                | 4.6.2 Design of a hardware accelerator for quantization | 56       |

|   | 4.7            | Tips and tricks                                         | 57       |

|   | 4.8            | What to include in the lab report                       | 57       |

| 5 | Lah            | task 3                                                  | 59       |

| 5 | <b>Lau</b> 5.1 | DMA in the DCT Accelerator                              | 59<br>59 |

|   | 5.1            | 5.1.1 Proposed architecture                             | 59       |

|   |                | 5.1.2 jpeg_dma.sv                                       | 60       |

|   |                | 5.1.3 How to use DMA in jpegfiles                       | 62       |

|   |                | 5.1.4 Cache coherency issue                             | 62<br>62 |

|   | 5.2            | ,                                                       | 62<br>63 |

|   | 5.2            | What to Include in the Lab Report                       | 03       |

4

| 6 | Lab         | task 4 - Custom Instructions           | 65 |

|---|-------------|----------------------------------------|----|

|   | 6.1         | Introduction                           | 65 |

|   |             | 6.1.1 Huffman Coding                   | 65 |

|   |             | 6.1.2 The Problem                      | 66 |

|   | 6.2         | Adding a New Instruction               | 66 |

|   |             | 6.2.1 Making the Processor Understand  | 66 |

|   |             | 6.2.2 Adding Special Purpose Registers | 66 |

|   |             | 6.2.3 Adding the Required Hardware     | 67 |

|   | 6.3         | Proposed Architecture                  | 67 |

|   |             | 6.3.1 Control Unit                     | 67 |

|   |             | 6.3.2 Data Path                        | 68 |

|   |             | 6.3.3 Store Unit                       | 68 |

|   |             | 6.3.4 Multi Cycle Instructions         | 68 |

|   |             | 6.3.5 Instruction Details              | 68 |

|   | 6.4         | Hardware Implementation                | 68 |

|   |             | 6.4.1 Constructing the Hardware        | 69 |

|   | 6.5         | Software Implementation                | 69 |

|   |             | 6.5.1 Running the Instruction          | 69 |

|   |             | 6.5.2 Integration into jpegfiles       | 71 |

|   |             | 6.5.3 JPEG Markers                     | 71 |

|   | 6.6         | Important Files For this lab task      | 72 |

|   | 6.7         | Tips and tricks                        | 72 |

|   | 6.8         | What to Include in the Lab Report      | 73 |

|   | 6.9         | Beyond tsea44                          | 74 |

| A | Ope         | n RISC Reference Platform              | 77 |

|   | A.1         | Address map                            | 77 |

|   | A.2         | Interrupts                             | 78 |

|   |             |                                        |    |

| B | The         | Wishbone specification                 | 79 |

|   | <b>B</b> .1 | Introduction                           | 79 |

|   | <b>B</b> .2 | Interface signals                      | 80 |

|   |             | B.2.1 adr                              | 80 |

|   |             | B.2.2 dat_o and dat_i                  | 80 |

|   |             | B.2.3 we                               | 80 |

|   |             | B.2.4 sel                              | 80 |

|   |             | B.2.5 stb                              | 80 |

|   |             | B.2.6 cyc                              | 81 |

|   |             | B.2.7 ack                              | 81 |

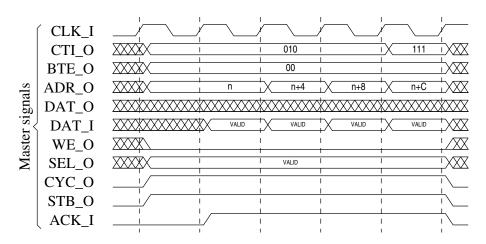

|   |             | B.2.8 cti                              | 81 |

|   |             | B.2.9 bte                              | 81 |

|   |             | B.2.10 err                             | 81 |

|   | B.3         | Wishbone classical cycles              | 81 |

|   | <b>B</b> .4 | Wishbone incrementing burst cycles     | 82 |

|   | B.5         | System Verilog Interface               | 83 |

|   |             |                                        |    |

# CONTENTS

# **Chapter 1**

# The system

# 1.1 Introduction

This text is intended as a laboratory compendium for the course TSEA44 Computer Hardware - a System On a Chip. We begin with a presentation of the hardware and software used for the laboratory exercises. If you wonder, the name *dafk* seen in many places in this course, comes from the name *DAtorteknik FortsättningsKurs* which is the Swedish name of the first version of this course. Roughly translated it means advanced course in computer technology.

# 1.2 Hardware

The lab tasks are all tested on real hardware. A suitable technology that is flexible enough to allow changes on both software and hardware is FPGA-based development systems. This course is therefore using such a board as the hardware platform on which the computer system is implemented.

## 1.2.1 Virtex-II Development board

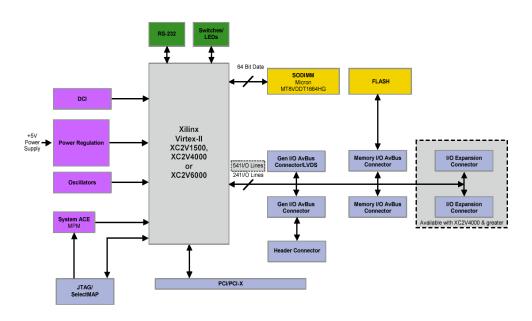

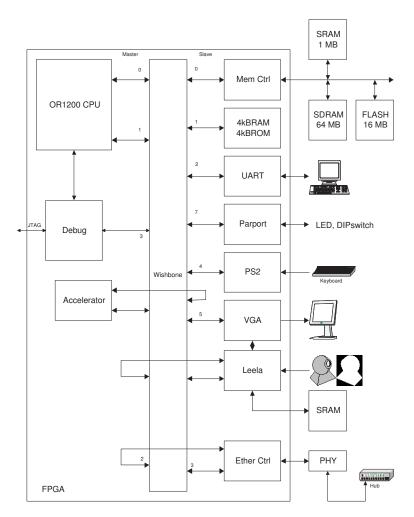

In the course we will use a development FPGA board from Avnet Corporation. A block diagram of this board is shown in Figure 1.1. More details are given in the User's Guide, [1].

#### 1.2.2 Communication/Memory Module

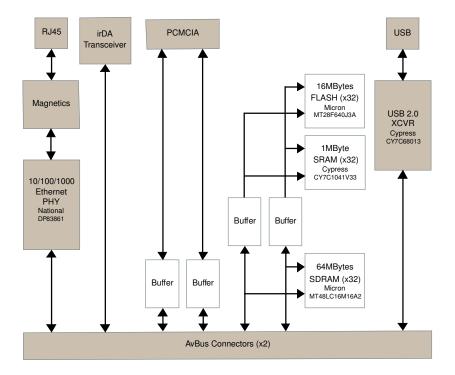

The main FPGA board is extended with a Communication and Memory Module, shown in Figure 1.2. More details are given in the User's Guide, [2].

Figure 1.1: Block diagram of the Avnet main board.

Features of the Communication/Memory module are:

- 1 MB SRAM.

- 16 MB Flash memory.

- 64 MB SDRAM.

- 10(/100/1000) Mb/s Ethernet PHY.

- (IrDA for infrared communication).

- (USB2.0 PHY).

- (PC card connector).

Features within parentheses will not be used in this course.

Figure 1.2: Block diagram of the Avnet communication and memory module.

# 1.2.3 Virtex-II 4000 FPGA

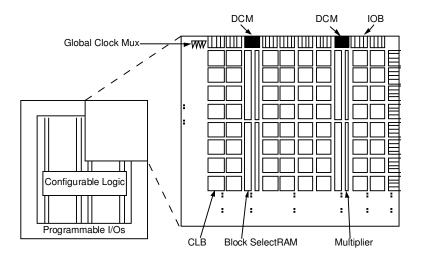

The most important circuit on the board is of course the mighty Virtex-II 4000 FPGA, [5]. The table 1.1 gives some details of this impressive circuit, which is shipped in an 1152 pin BGA (ball grid array).

The internal configurable logic in the FPGA includes four major elements organized in a regular array:

#### • CLBs (Configurable Logic Blocks):

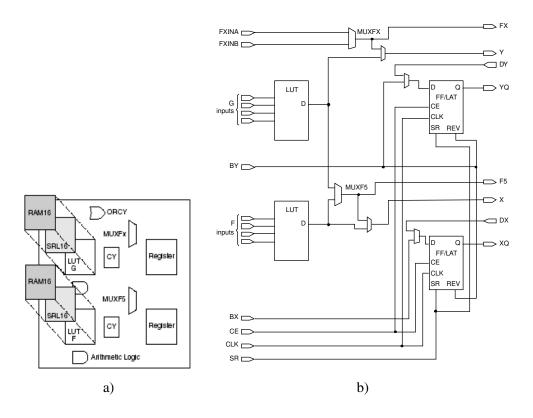

This is the programmable logic used to build combinatorial and sequential logic. The FPGA contains  $80 \times 72 = 5760$  CLBs. Each CLB is made up of 4 slices, see Figure 1.4.

#### • Multipliers:

The FPGA contains 120  $18 \times 18$ -bit multipliers. These are used for the ALU in the OR1200 CPU.

• Block RAMs:

The FPGA contains 120 18 kbit RAMs. These are typically used for cache memories inside the CPU, FIFOs in the UART and Ethernet controller.

#### • DCMs (Digital Clock Managers):

The FPGA contains 12 DCMs. The DCMs can divide/multiply the input clock frequency. We use a DCM to transform the input 40 MHz to 25 MHz.

A floorplan of the Virtex-II is shown in Figure 1.3.

The CLBs are organized in an array and connected to a switching matrix. Each CLB comprises 4 slices, which are connected locally. Each slice includes two 4-input

|          |                 | (1 CLB = 4          | CLB<br>slices = N | lax 128 bits)                       |                      | SelectF           | AM Blocks           |      |                                |

|----------|-----------------|---------------------|-------------------|-------------------------------------|----------------------|-------------------|---------------------|------|--------------------------------|

| Device   | System<br>Gates | Array<br>Row x Col. | Slices            | Maximum<br>Distributed<br>RAM Kbits | Multiplier<br>Blocks | 18 Kbit<br>Blocks | Max R AM<br>(Kbits) | DCMs | Max I/O<br>Pads <sup>(1)</sup> |

| XC2V40   | 40K             | 8 x 8               | 256               | 8                                   | 4                    | 4                 | 72                  | 4    | 88                             |

| XC2V80   | 80K             | 16 x 8              | 512               | 16                                  | 8                    | 8                 | 144                 | 4    | 120                            |

| XC2V250  | 250K            | 24 x 16             | 1,536             | 48                                  | 24                   | 24                | 432                 | 8    | 200                            |

| XC2V500  | 500K            | 32 x 24             | 3,072             | 96                                  | 32                   | 32                | 576                 | 8    | 264                            |

| XC2V1000 | 1M              | 40 x 32             | 5,120             | 160                                 | 40                   | 40                | 720                 | 8    | 432                            |

| XC2V1500 | 1.5M            | 48 x 40             | 7,680             | 240                                 | 48                   | 48                | 864                 | 8    | 528                            |

| XC2V2000 | 2M              | 56 x 48             | 10,752            | 336                                 | 56                   | 56                | 1,008               | 8    | 624                            |

| XC2V3000 | ЗM              | 64 x 56             | 14,336            | 448                                 | 96                   | 96                | 1,728               | 12   | 720                            |

| XC2V4000 | 4M              | 80 x 72             | 23,040            | 720                                 | 120                  | 120               | 2,160               | 12   | 912                            |

| XC2V6000 | 6M              | 96 x 88             | 33,792            | 1,056                               | 144                  | 144               | 2,592               | 12   | 1,104                          |

| XC2V8000 | 8M              | 112 x 104           | 46,592            | 1,456                               | 168                  | 168               | 3,024               | 12   | 1,108                          |

Table 1.1: Virtex-II table. XC2V4000 is our FPGA.

function generators, carry logic, multiplexers and two storage elements, see Figure 1.4. The function generator can be programmed as a 4-input lookup table (LUT), 16-bit RAM or 16-bit variable-tap shift register.

# 1.3 Open RISC

The computer architecture used in this lab course is based on an open-source processor design called Open RISC. This processor together with its bus system and some I/O units are defined and implemented in the FPGA by synthesis of Verilog code.

# 1.3.1 Top Design

The computer used in this lab course is designed with Verilog modules, which can be downloaded free from Open Cores (www.opencores.org) and some modules designed by us.

This section describes the main system defined in dafk.sv, which you will use in lab task 2-4

Figure 1.3: Virtex-II architectural overview.

The computer in Figure 1.5 consists of the following modules:

• OR1200 CPU:

RISC CPU with a 5-stage pipeline.

- Wishbone: An interconnect bus with 16 ports, 8 master ports and 8 slave ports.

- Memory Controller:

A memory controller for SRAM, SDRAM and Flash memories.

• UART:

A 16550 UART with baudrates up to 115200 b/s.

• Ethernet Controller:

An implementation of the MAC layer, which requires an external PHY circuit for a complete solution.

- Parallel Port

- VGA Controller

- Camera Controller

- **DCT Accelerator**: It will be your task to finish the implementation of this module.

#### **1.3.2** Structure of the Verilog code

The structure of the Verilog code closely resembles the block diagram shown in Figure 1.5. Components outside the FPGA are simulated. Here is a list of the hierarchy instantiated in dafk\_tb:

- phy0: Simulation model of the Ethernet physical to logic level chip

- videomem: Simulation model of the video memory

Figure 1.4: a) Virtex-II slice configuration b) Detail of slice (top half).

- mysram: Simulation model of the SRAM

- sdram0: Simulation model of the SDRAM

- dafk\_top: The code to be synthesized in the FPGA

- sys\_sig\_gen: Generates clock and reset signals

- or1200\_top: The OR1200 CPU

- pkmc\_top: Memory controller

- rom0: The boot code and vector table resides here

- uart2: UART 16550

- eth3: Ethernet controller

- dvga: VGA controller

- pia: Simple parallel port

- jpg0: DCT accelerator

- perf: Performance counters

- leela: Camera module

- wb\_conbus: The wishbone bus

Figure 1.5: An Open RISC computer.

# 1.3.3 OR1200 CPU

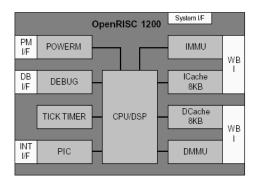

A block diagram of the OR1200 CPU is shown in Figure 1.6. More information about the CPU can be found in [6, 7].

The OR1200 CPU, [8], consists of several blocks:

# • High Performance 32-Bit CPU/DSP

- 32-bit architecture implementing ORBIS32 instruction set

- Scalar, single-issue 5-stage pipeline delivering sustained throughput

- Single-cycle instruction execution on most instructions

- Can be run at 250MHz in an ASIC

- Thirty-two, 32-bit general-purpose registers

- Custom user instructions

- L1 Caches

- Harvard model with split instruction and data cache

Figure 1.6: Block diagram of the OR1200 CPU.

- Instruction/data cache size scalable from 1KB to 64KB

# • Memory Management Unit

- Harvard model with split instruction and data MMU

- Instruction/data TLB size scalable from 16 to 256 entries

- Direct-mapped hash-based TLB

- Linear address space with 32-bit virtual address and physical address from 24 to 32 bits

- Page size 8KB with per-page attributes

- Advanced Debug Unit

- Conventional target-debug agent with a debug exception handler

- Non-intrusive debug/trace for both RISC and system

- Access and control of debug unit from RISC or via development interface

- Integrated Tick Timer

- Task scheduling and precise time measuring

- Maximum timer range of  $2^{32}$  clock cycles

- Maskable tick-timer interrupt

- Programmable Interrupt Controller

- 2 non-maskable interrupt sources

- 30 maskable interrupt sources

- two interrupt priorities

In this lab course the Power Management module is disabled.

# 1.3.4 The Wishbone Interconnect Bus

The Wishbone Interconnect is a standard way of connecting IP (Intellectual Property) blocks in System-on-Chip designs, see for instance [9]. It can be implemented in different ways ranging from a fully connected crossbar to an ordinary shared bus. In this course the shared bus variant is used. It is important to understand that there is no

#### 1.3. OPEN RISC

parallelism in this implementation. It is just a connection between one master and one slave. Furthermore tristate is not used, instead there are two databuses, one in each direction. The address bus and the data busses are 32 bits wide.

Figure 1.7: The Wishbone interconnect bus. In this example Master 0 is addressing Slave 1. Master 0 has won the arbitration.

We will briefly explain how the Wishbone bus works with a simple example. We assume a computer system like in Figure 1.5 and that the CPU executes a program in the memory, that is connected to slave port 1, see Figure 1.7. The CPU places an address  $A_0$  at the address lines at master port 0 and asserts the signal STB. The arbiter inside the Wishbone grants the bus to master 0. The address  $A_0$  will now show up on all slave ports. Address decoding logic routes the asserted STB-signal only to slave port 1. The memory at slave port 1 places  $D_1$  on the data bus and asserts the signal ACK.  $D_1$  will now show up on all master ports, but ACK will only be asserted at master port 0.

#### **1.3.5** Memory Controller

In this lab course we will use a simple memory controller, designated PKMC, designed by us. PKMC is implemented for this particular system and thus needs no configuration. PKMC handles all communications with the SRAM, SDRAM and FLASH memory. Especially ensuring that the SDRAM is refreshed correctly.

#### **1.3.6** Ethernet Controller

The Ethernet IP Core, [10], consists of five modules:

- The MAC (Media Access Control) module, formed by transmit, receive, and control module

- The MII (Media Independent Interface) Management module

| Address                   | Туре          | Content                             |

|---------------------------|---------------|-------------------------------------|

| 0x0000_0000 - 0x03ff_ffff | SDRAM         | Programs can be loaded and run      |

|                           |               | here 64MB                           |

| 0x2000_0000 - 0x200f_ffff | SRAM          | Data area 1MB                       |

| 0x4000_0000 - 0x4000_5fff | ROM           | Boot monitor, 24kB                  |

| 0x4001_1000 - 0x4001_1fff | RAM           | Data area for monitor and stack 8kB |

| 0x9000_0000 - 0x90ff_ffff | UART          |                                     |

| 0x9100_0000 - 0x91ff_ffff | Parallel port |                                     |

| 0x9200_0000 - 0x92ff_ffff | Ethernet      |                                     |

| 0x9600_0000 - 0x96ff_ffff | Accelerator   | Your JPEG accelerator               |

| 0xf000_0000 - 0xf0ff_ffff | FLASH         | Bender, $\mu$ Clinux and Linux      |

Table 1.2: Memory map of the computer system.

• The Host Interface

The Ethernet IP Core is capable of operating at 10 or 100 Mbps for Ethernet and Fast Ethernet applications. An external PHY is needed for a complete Ethernet solution.

In short the ethernet controller works as follows. There are 64 transmit buffers and 64 receive buffers. These buffers are typically located in the SRAM. To each such buffer there is a pair of registers (a buffer descriptor) inside the Ethernet Controller, one register holds the address of the buffer and one register is a control/status-register. The ethernet controller transmits/receives packets from/to the SRAM buffers with DMA.

### 1.3.7 VGA Controller

The VGA controller used is designed by us and is a simple single-video-mode controller for use in FPGA or ASIC environments. The VGA controller supports a single resolution/refresh rate in grey scale or 8-bit pseudocolor with 15-bit color sprites. For further details see [12].

### 1.3.8 UART

The UART (Universal Asynchronous Receiver Transmitter) is an implementation of the industry standard 16550 device. Details can be found in [13].

# 1.4 Software

An important part of the computer system is the software running on it. How to access hardware units, memories etc. is described in this section.

### 1.4.1 Memory map

The I/O is memory mapped. The memory adresses for the various I/O units and memory types are show in table 1.2.

| Command                       | Explanation                    |

|-------------------------------|--------------------------------|

| d <addr></addr>               | display memory content         |

| m <addr> <data></data></addr> | modify memory content          |

| g <addr></addr>               | go (execute)                   |

| 1                             | load Intel hex file            |

| u                             | boot uClinux (copy from FLASH) |

Table 1.3: Some useful commands in the monitor.

#### 1.4.2 A simple boot monitor

A simple monitor runs in the memory on slave port 1. The monitor will start at boot. Use for instance gtkterm and adjust the baud rate to 115200 b/s. Format should be 8N1 and no flow control. The port shall be /dev/ttyUSB0 or similar. Type h for help. Some available commands are explained in table 1.3.

Type 1 and then use the command File -> Send raw file in gtkterm to load an Intel hex file into memory. The hex file itself contains address information.

#### A simple program.

In this section we will demonstrate how to compile, load and run a C-program in the monitor evironment. We will use the program described in Listing 1.1 as an example.

```

Listing 1.1: simpleprog

```

```

#include "common.h"

int main(void)

ł

int Begin_Time, User_Time;

int i;

printf("Hello_world!\n");

Begin_Time = get_timer(0);

for (i=0; i<10; i++) {

led(i); /* Set the led display on the card */

printf("%d\n",i);

sleep (1); /* sleep 1 s */

}

User_Time = get_timer(Begin_Time);

printf("Time=u%dus\n", User_Time);

return (0);

}

```

The program prints a string, counts on the LEDs and measures the elapsed time.

To build simpleprog we use a Makefile described in Listing 1.2, in the Makefile we observe the following:

• A cross-compiler, or32-uclinux-gcc, must be used.

- The functions printf, get\_timer, led and sleep are library functions in openrisclib, which is included in the lab skeleton for lab 1.

- A link script ram.ld is used to determine where in memory our program should be located.

```

# The name of the program we want to compile

PROGRAM = simpleprog

```

```

# The directory containing the open risc supportdir

LIBDIR = ../lib

INCLUDEDIR = ../include

```

```

CFLAGS += -I$(INCLUDEDIR) -Wall -Wstrict-prototypes

CFLAGS += -Werror-implicit-function-declaration

CFLAGS += -Os -g -fno-builtin -fomit-frame-pointer -nostdlib

```

Listing 1.2: Makefile for simpleprog (Listing 1.1)

```

# Toolchain configuration

AS = or32-uclinux-as

CC = or32-uclinux-gcc

LD = or32-uclinux-ld

DUMP = or32-uclinux-objdump -S -D -EB

COPY = or32-uclinux-objcopy

SIM = or32-uclinux-sim

```

# Flags to LD, need to include a link script here LDFLAGS = -Tram.ld

OBJFILES=\$(PROGRAM).o

HEXFILE=\$(PROGRAM).hex

```

SIMPROGRAM=$ (PROGRAM) sim

```

```

all: $(PROGRAM) $(HEXFILE) $(SIMPROGRAM)

```

```

# The minimal supportlib containing printf/sleep/etc

openrisclib: $(LIBDIR)/openrisclib.a $(LIBDIR)/crt.o $(LIBDIR)/reset.o

# Commands to make the open risc support lib

```

```

$(LIBDIR)/openrisclib.a:

cd $(LIBDIR) && $(MAKE)

$(LIBDIR)/crt.o:

```

cd \$(LIBDIR) && \$(MAKE)

\$(LIBDIR)/reset.o: cd \$(LIBDIR) && \$(**MAKE**)

. S . o :

```

$(CC) $(CFLAGS) −c $<

```

.c.o:

```

$(CC) -c $(CFLAGS) -o $@ $<

# Link the program together with the supportlib</pre>

```

```

# (And create a text file with the disassembled contents of the program)

$(PROGRAM): $(OBJFILES) ram.ld openrisclib

$(LD) -Bstatic $(LIBDIR)/crt.o $(OBJFILES) $(LIBDIR)/openrisclib.a \

$(LDFLAGS) -o $(PROGRAM)

```

```

(DUMP)  (PROGRAM) >  (PROGRAM). t x t

```

```

# Create an intel hex dump of the program

$(HEXFILE): $(PROGRAM)

```

# \$(COPY) -O ihex \$(PROGRAM) \$(HEXFILE)

```

# Create a binary we can simulate with the openrisc simulator

$(SIMPROGRAM): $(PROGRAM) ram.ld openrisclib

$(LD) -Bstatic $(LIBDIR)/reset.o $(PROGRAM) $(LDFLAGS) -o $(SIMPROGRAM)

$(DUMP) $(SIMPROGRAM) > $(SIMPROGRAM).txt

```

We place all the segments of simpleprog at the address 0x2000 with the link script shown in Listing 1.3.

Listing 1.3: Link script for simpleprog (Listing 1.1)

```

MEMORY

{

: ORIGIN = 0 \times 00000000, LENGTH = 0 \times 00002000

vectors

: ORIGIN = 0 \times 00002000, LENGTH = 0 \times 03 ffe000

sdram

}

SECTIONS

{

.vectors :

{

*(.vectors)

} > vectors

.text :

{

*(.text)

} > sdram

.rodata ALIGN(4) :

{

*(.rodata)

} > sdram

.rodata.str1.1 ALIGN(4) :

{

*(.rodata.str1.1)

} > sdram

.data ALIGN(4):

{

*(.data)

} > sdram

.bss ALIGN(4):

{

*(.bss)

} > sdram

}

```

### 1.4.3 The simulator or 32-uclinux-sim

The simulator is started with the command

```

or32-uclinux-sim -f sim.cfg prog ,

```

where sim.cfg describes the hardware and prog is the program to run on the simulated hardware. Some help is printed out by the command

or32-uclinux-sim -h .

The simulator can also be started in an interactive mode by

or32-uclinux-sim -f sim.cfg -i prog .

| Bender Monitor (type 'help' for help) |                                                               |                                                    |                                                    |          |                  |  |  |  |

|---------------------------------------|---------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------|------------------|--|--|--|

| bender> dm 0x100<br>dm 0x100          |                                                               |                                                    |                                                    |          |                  |  |  |  |

| 00000110:                             | 9c600001<br>44001800<br>00000000                              | 15000000                                           | 00000000                                           | 00000000 | .`@` .(c<br>D    |  |  |  |

| 00000140:<br>00000150:                | $\begin{array}{c} 00000000\\ 00000000\\ 00000000 \end{array}$ | 000000000000000000000000000000000000000            | 00000000<br>00000000                               | 00000000 | •••••            |  |  |  |

| 00000170:<br>00000180:                | 000000000000000000000000000000000000000                       | 000000000000000000000000000000000000000            | 00000000<br>00000000                               | 00000000 | ••••••<br>•••••• |  |  |  |

| 000001a0:<br>000001b0:                | 000000000000000000000000000000000000000                       | 000000000000000000000000000000000000000            | 00000000<br>00000000                               | 00000000 | ••••••<br>•••••  |  |  |  |

| 000001d0:<br>000001e0;                | 00000000<br>00000000<br>00000000                              | $\begin{array}{c} 00000000\\ 00000000 \end{array}$ | $\begin{array}{c} 00000000\\ 00000000 \end{array}$ | 00000000 | •••••            |  |  |  |

Figure 1.8: Simulation of the bender monitor.

In Figure 1.8 we show as an example the simulation of a simple monitor in an xterm window.

The command help lists available commands, for instance t (trace):

```

>t

00000000 l.j 0x0 (executed) [time 40ns, #1]

00000100:

:

00000104:

00000000 1.j 0x0 (next insn) (delay insn)

:

GPR00:

00000000 GPR01:

00000000 GPR02:

00000000 GPR03:

0000000

GPR04:

00000000 GPR05:

00000000 GPR06:

0000000 GPR07:

0000000

GPR08:

00000000 GPR09:

00000000 GPR10:

0000000 GPR11:

0000000

GPR12:

00000000 GPR13:

00000000 GPR14:

0000000 GPR15:

0000000

00000000 GPR17:

00000000 GPR18:

00000000 GPR19:

GPR16:

0000000

GPR20:

00000000 GPR21:

00000000 GPR22:

0000000 GPR23:

0000000

GPR24:

0000000 GPR25:

00000000 GPR26:

00000000 GPR27:

0000000

GPR28:

00000000 GPR29:

00000000 GPR30:

00000000 GPR31:

00000000 flag: 0

```

#### 1.4.4 $\mu$ Clinux

$\mu$ Clinux, which stands for microcontroller Linux, is a Linux variant intended for computers without a Memory Management Unit (MMU). This means that the kernel and the processes reside in the same address space.

You can start  $\mu$ Clinux by giving the u command from the boot monitor.  $\mu$ Clinux is now copied from FLASH (0xf0100000) to SDRAM (0x0) and the booting process starts.

The command help will list the built-in shell commands.

An important file is /etc/rc, the start-up file, which is shown in Listing 1.4. If you want to change the start-up behavior of  $\mu$ Clinux this the file to change. In a running  $\mu$ Clinux this file resides in a non-writable file system. A new system must be recompiled on a host computer, downloaded over the serial port and flashed to the flash memory. It is very unlikely that you have to do this in the course of this lab series.

Listing 1.4: µClinux configuration file /etc/rc

```

#!/bin/sh

#

setenv PATH /bin:/sbin:/usr/bin

hostname bender

#

mount -t proc none /proc

/bin/expand /ramfs512.img /dev/ram1

mount -t ext2 /dev/ram1 /var

mkdir /var/log /var/log/boa /var/lock /var/tmp /var/run

chmod 777 /var/tmp

#

/bin/expand /ramfs8192.img /dev/ram2

mount -t ext2 /dev/ram2 /mnt

mkdir /mnt/bin

# Set up the webserver stuff

mkdir /mnt/htdocs

cp /misc/* /mnt/htdocs

mkdir /mnt/htdocs/cgi-bin

# Bring up the local interface

/sbin/ifconfig lo 127.0.0.1

/sbin/route add -net 127.0.0.0

# Set IP address from configuration data in flash

/sbin/setip

# Start the web server

/sbin/boa -d &

```

#### Running programs under $\mu$ Clinux

We demonstrate how to run a program in the  $\mu$ Clinux environment by an example. The program, shown in Listing 1.5, displays the contents of a Special Purpose Register (SPR). It uses inline assembler to read a register. We use the Makefile shown in Listing 1.6 to compile the program shown in Listing 1.5. The flags -r and -d to \$CC are important, otherwise the program will not execute.

```

#include <sys/types.h>

#include <sys/stat.h>

#include <asm/io.h>

#include <asm/spr_defs.h>

#include <asm/board.h>

int main (int argc, char *argv[])

{

unsigned long val, addr;

if (argc == 2) {

addr = strtoul (argv[1], 0, 0);

/* Read SPR */

asm("1.mfspru%0,%1,0": "=r" (val) : "r" (addr));

printf ("\nSPRu%041x:u%081x\n", addr, val);

} else return -1;

return 0;

}

```

Listing 1.6: Makefile to compile the program showing an SPR (Listing 1.5).

```

CC = or32-uclibc-gcc

STRIP = or32-uclibc-strip

PRGS = mfspr

all: $(PRGS)

mfspr: mfspr.o

$(CC) -r -d mfspr.o -o $@

$(STRIP) -g $@

```

Finally the program can be downloaded with tftp. Change directory (cd) to a writable portion of the filesystem, like for instance /var/tmp. Then start the tftp client

> tftp IP\_address\_of\_your\_tftp\_server

Retrieve the program:

> get mfspr

See section 4.3.2 for more information on how to start the TFTP server.

# **Chapter 2**

# Lab task 0 - Build a UART in Verilog

# 2.1 Introduction

In this introductory lab exercise you will learn the HDL Verilog. We require that you are familiar with another HDL, typically VHDL. In our opinion hardware design is done by drawing hardware diagrams, so that the programming in Verilog is just a final simple translation step!

You will also get (re)acquainted with the tools used in this course, ModelSim and make (or Xilinx Project Navigator).

The initial tests will use the Zedboard instead of the described VirtexII. Once the design works on the Zedboard, you will move the design to the VirtexII board.

# 2.2 A simple UART

A computer system is hard to use if you can not communicate with it. One of the simplest ways to send and receive characters is to use a serial communication protocol such as RS232.

# 2.2.1 General

For the lab you will have to download tsea44.tgz. Uncompress the downloaded file using tar xzvf tsea44.tgz. Make sure the path does not contains spaces or other strange characters. Inspect the directory hw and you will find:

- lab0\_zed.sv, a skeleton for the top file when using zedboard.

- lab0.sv, a skeleton for the top file when using VirtexII.

- lab0\_zed.ucf, lab0.ucf, User Constraints Files for use with zedboard and VirtexII respectively.

- dafk\_tb, a folder containing the testbenches for both zedboard and VirtexII board.

• simulator, a folder containing tcl script files for use with the modelsim simulator.

#### 2.2.2 The RS232 protocol

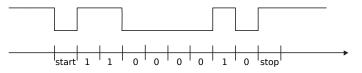

In this exercise you shall design a simple RS232 transceiver in Verilog. We assume that the serial port of the FPGA board is connected to a PC, where a terminal program is running. This is typically gtkterm if you are using Linux or Teraterm if you are running in Windows. The bit rate should be fixed 115200 bits/s. Your design shall use the parameters 8N1, that is 8 message bits, no parity bit and 1 stop bit, see Figure 2.1. Messages are sent and received with LSB first. Furthermore your UART shall support full duplex operation, that is be able to transmit and receive at the same time.

Figure 2.1: The letter C (0x43). Time per bit is 8.68  $\mu$ s.

#### 2.2.3 The zedboard hardware

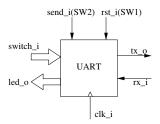

The system clock of the zedboard is running at 100 MHz. You will need a reset-signal and a send-signal, see Figure 2.2. Both these signals are active-high.

Figure 2.2: The UART.

Your task is twofold with an additional feature:

- send exactly one ASCII-coded character from the switches of the zedboard to the PC by pressing the button BTNU switch once, see Figure 2.2.

- catch the incoming characters from rx\_i and present the ASCII code on the LED display, see Figure 2.2.

- when reset is pressed and released (BTND switch) output (and keep) on the LED the value of the last two digits of your student-id. Example: the student linus123 should output the value 23 on the LED (00010111).

Some advice before you start:

- The signal rx\_i is asynchronous. We strongly advice you to synchronize it!

- You will use your UART on the VirtexII board in the second part of lab0 with a slower system clock of 40 MHz, and finally in lab task 1 with an even slower system clock of 25 MHz. We suggest that you prepare the frequency change with an 'ifdef 'else 'endif construct.

- Avoid continously sending the character while BTNU is pressed.

## 2.2.4 A simple testbench

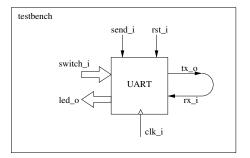

You will also need a test bench. Since you are designing both a transmitter and a receiver you may choose to test them both at the same time, see Figure 2.3.

There are two different boards used, and there are therefore two different testbenches available. Use the lab0\_zed\_tb to test the design to run on the zedboard. The corresponding designfile is then named lab0\_zed.sv.

Figure 2.3: A testbench.

The code for the test bench shown in Figure 2.3, is listed in Listing 2.1.

Listing 2.1: Test bench for the UART.

```

'timescale 1ns / 10ps

module lab0_zed_tb();

reg clk_i;

reg rst_i;

reg send_i;

reg [7:0] switch_i;

wire [7:0] led_o;

wire jumper;

// Instantiate a UART

lab0_zed uart(.clk_i(clk_i), .rst_i(rst_i), .rx_i(jumper), .tx_o(jumper),

.led_o(led_o), .switch_i(switch_i), .send_i(send_i));

always #5 clk_i = ~clk_i; // 100 MHz clock

initial

begin

clk_i = 1'b0;

switch_i = 8'h43; // C

rst_i = 1'b1;

send_i = 1'b0;

#200 rst_i = 1'b0;

#1000 send_i = 1'b1;

#1100 send_i = 1'b0;

end

endmodule

```

# 2.3 Exercises

# Preparation task 1

Individual! Draw a HW diagram of the UART. Use simple components like counters, registers, shift registers, and state machines. Show this to the lab supervisor at the start of the lab!

# Laboration task 0.1

Individual!

a) Translate your HW diagram into Verilog code to be used on the zedboard. Use the lab0\_zed.sv file

b) Simulate your design in ModelSim, using the lab0\_zed\_tb

c) Synthesize your design, program the FPGA and test run your design.

d) Move the design to the VirtexII board. Do this by copying the code into lab0.sv, update the clock frequency, and if necessary modifying the testbench lab0\_tb.sv

#### 2.3.1 Commands

Add definitions of tools to use by adding the course module using the command module load courses/TSEA44. To start the simulator with the zedboard design, use the command make sim\_lab0\_zed, and to start the simulator with the VirtexII design use the command make sim\_lab0. To generate a bitfile to program the FPGA of the zedboard use make lab0\_zed.bit and for the VirtexII use make lab0.bit.

To configure the Zedboard FPGA with a .BIT file, use sh utils/download\_zed.sh lab0\_zed.bit, and use use sh utils/download.sh lab0.bit to program the VirtexII board. There are also a makefile target prog\_lab0\_zed and prog\_lab0 to simplify these tasks.

## 2.3.2 A User Constraint File

You will need the User Constraint File that describe the board signals. The list used for the zedboard is shown in Listing 2.3. The exact same signals and names mentioned in Listing 2.3 must be present in the interface declaration of you top module. Comment out the lines that you don't use. (This file is included in the lab skeleton as lab0\_zed.ucf for the zedboard and lab0.ucf for the Virtex II board.)

| Listing 2.2: User constraints | file for your | UART o | on zedboard |

|-------------------------------|---------------|--------|-------------|

|-------------------------------|---------------|--------|-------------|

| 0                  |          |           | 5                    |                               |

|--------------------|----------|-----------|----------------------|-------------------------------|

|                    |          |           |                      | // 100 MHz on Zedboard        |

| NET "rst_i"        | LOC = "  | 'R16"     | IOSTANDARD=LVCMOS18; | // BTND (downward) on green f |

| NET "send_i"       | LOC = "  | 'T18"     | IOSTANDARD=LVCMOS18; | // BTNU (up) on green flexo   |

| // black switches  |          |           |                      |                               |

| NET "switch_i<0>"  | LOC = "  | 'F22"     | IOSTANDARD=LVCMOS18; | // SW0                        |

| NET "switch_i <1>" | LOC = "  | 'G22"     | IOSTANDARD=LVCMOS18; | // SW1                        |

| NET "switch_i<2>"  | LOC = "  | 'H22"     | IOSTANDARD=LVCMOS18; | // SW2                        |

| NET "switch_i<3>"  | LOC = "  | 'F21"     | IOSTANDARD=LVCMOS18; | // SW3                        |

| NET "switch_i<4>"  | LOC = "  | 'H19"     | IOSTANDARD=LVCMOS18; | // SW4                        |

| NET "switch_i<5>"  | LOC = "  | 'H18"     | IOSTANDARD=LVCMOS18; | // SW5                        |

| NET "switch_i<6>"  | LOC = "  | 'H17"     | IOSTANDARD=LVCMOS18; | // SW6                        |

| NET "switch_i <7>" | LOC = "  | 'M15"     | IOSTANDARD=LVCMOS18; | // SW7                        |

| // row of LEDs ab  | ove swit | tches     |                      |                               |

|                    |          |           | IOSTANDARD=LVCMOS33; |                               |

| NET "led_o<1>"     | LOC = "  | 'T21"     | IOSTANDARD=LVCMOS33; | // LED LD1                    |

| NET "led_o<2>"     | LOC = "  | 'U22"     | IOSTANDARD=LVCMOS33; | // LED LD2                    |

| NET "led_o<3>"     | LOC = "  | 'U21"     | IOSTANDARD=LVCMOS33; | // LED LD3                    |

| NET "led_o<4>"     | LOC = "  | 'V22"     | IOSTANDARD=LVCMOS33; | // LED LD4                    |

| NET "led_o<5>"     | LOC = "  | 'W22"     | IOSTANDARD=LVCMOS33; | // LED LD5                    |

| NET "led_o<6>"     | LOC = "  | 'U19"     | IOSTANDARD=LVCMOS33; | // LED LD6                    |

| NET "led_o<7>"     | LOC = "  | 'U14"     | IOSTANDARD=LVCMOS33; | // LED LD7                    |

| // PMOD JB connec  | ted to U | USB - UAR | Τ                    |                               |

| NET "rx_i"         | LOC = "  | 'V10"     | IOSTANDARD=LVCMOS33; | // PMOD B, JB3                |

| NET "tx_o"         | LOC = "  | 'W11"     | IOSTANDARD=LVCMOS33; | // PMOD B, JB2                |

Listing 2.3: User constraints file for your UART on VirtexII

| NET "clk_i"           | LOC =                | = | "AK19"; | // | 40 MHz in this lab         |  |  |  |  |  |

|-----------------------|----------------------|---|---------|----|----------------------------|--|--|--|--|--|

| NET "rst_i"           | LOC =                | = | "C2";   | // | SW1 (red) on green flexo   |  |  |  |  |  |

| NET "send_i"          | LOC =                | = | "B3";   | 11 | SW2 (black) on green flexo |  |  |  |  |  |

| // blue DIP switch    | // blue DIP switches |   |         |    |                            |  |  |  |  |  |

| NET "switch_i <7>"    | LOC =                | - | "AL3";  | 11 | SWITCH 1                   |  |  |  |  |  |

| NET "switch_i <6>"    | LOC =                | - | "AK3";  | 11 | SWITCH 2                   |  |  |  |  |  |

| NET "switch_i<5>"     | LOC =                | = | "AJ5";  | 11 | SWITCH 3                   |  |  |  |  |  |

| NET "switch_i <4>"    | LOC =                | - | "AH6";  | 11 | SWITCH 4                   |  |  |  |  |  |

| NET "switch_i<3>"     |                      |   |         |    |                            |  |  |  |  |  |

| NET "switch_i<2>"     | LOC =                | - | "AF7";  | 11 | SWITCH 6                   |  |  |  |  |  |

| NET "switch_i <1>"    | LOC =                | - | "AF11"; | 11 | SWITCH 7                   |  |  |  |  |  |

| NET "switch_i<0>"     | LOC =                | = | "AE11"; | 11 | SWITCH 8                   |  |  |  |  |  |

| // row of LEDs        |                      |   |         |    |                            |  |  |  |  |  |

| NET "led_o<7>"        | LOC =                | - | "N9";   | 11 | LED D4                     |  |  |  |  |  |

| NET "led_o<6>"        | LOC =                | - | "P8";   | 11 | LED D5                     |  |  |  |  |  |

| NET "led_o<5>"        |                      |   |         |    |                            |  |  |  |  |  |

| NET "led_o<4>"        | LOC =                | - | "N7";   | 11 | LED D7                     |  |  |  |  |  |

| NET "led_o<3>"        | LOC =                | - | "M6";   | 11 | LED D8                     |  |  |  |  |  |

| NET "led_o<2>"        | LOC =                | = | "M3";   | 11 | LED D9                     |  |  |  |  |  |

| NET "led_o<1>"        | LOC =                | - | "L6";   | 11 | LED D10                    |  |  |  |  |  |

| NET "led_o<0>"        | LOC =                | - | "L3";   | 11 | LED D11                    |  |  |  |  |  |

| // rainbow flat cable |                      |   |         |    |                            |  |  |  |  |  |

| NET "rx_i"            |                      | - | "M9";   |    |                            |  |  |  |  |  |

| NET "tx_o"            | LOC =                | - | "K5";   |    |                            |  |  |  |  |  |

|                       |                      |   |         |    |                            |  |  |  |  |  |

# 2.4 gtkterm usage

Start gtkterm in a shell or from **Applications->Accessories->GTKTerm** if your computer have the board to use connected. All computers have a zedboard connected, but there are fewer VirtexII boards.

Communication parameters are set from **Configuration->Port** and should for the zedboard be /dev/ttyUSB0 and for the VirtexII board be/dev/ttyUSB2. For both boards use speed 115200, no parity, 8 bits, 1 stop bit and no flow control.

# **Chapter 3**

# Lab task 1 - Interfacing to the Wishbone bus

# 3.1 Introduction

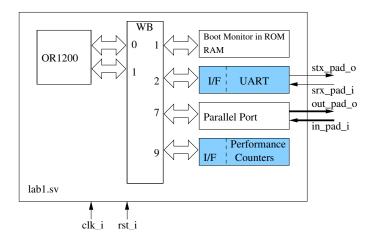

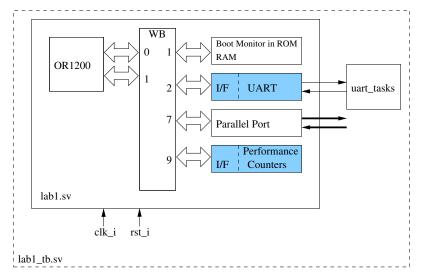

In this lab exercise you will get acquainted with the OR 1200 RISC processor and particularly the Wishbone bus. You will do this by designing and interfacing two modules, a UART and a performance counter module to the Wishbone bus.

Figure 3.1: The computer. The two gray modules will be designed by you.

Figure 3.1 depicts the computer that you are going to work with in this laboratory exercise. You will have to:

- 1. modify your UART from the previous lab and interface it to the Wishbone bus. The wishbone interface should be inserted into lab1/lab1\_uart\_top.sv.

- 2. check the UART device drivers in the boot monitor. The driver is in this file monitor/firmware/src/uartfun.c.

- 3. download and execute a benchmark program, that performs the DCT part of JPEG compression on a small image in your RAM module.

- 4. simulate the computer running the benchmark program.

- 5. design a module containing hardware performance counters (perf\_top.sv in the lab skeleton).

# **3.2** Some Basic Facts on the Wishbone Bus

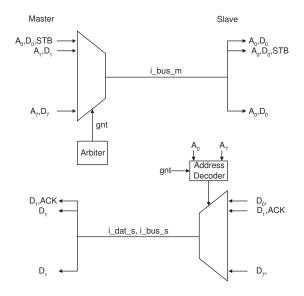

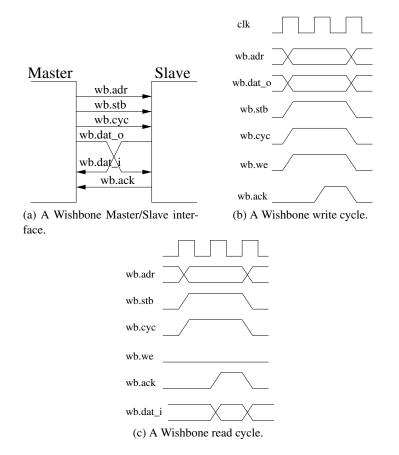

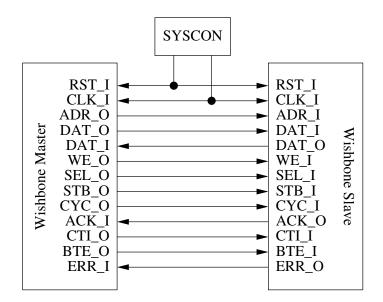

The Wishbone bus is intended for implementation in FPGAs or ASICs. Typical for such a bus is that multiplexers are used instead of tristate buffers. Two data buses are used, one for each direction, see Figure 3.2a.

Figure 3.2: The Wishbone bus protocol.

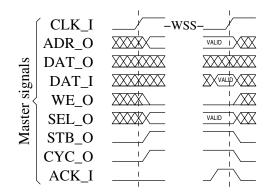

In this lab we will only need a subset of the Wishbone protocol, namely the basic write and read bus cycles.

For the write cycle, see Figure 3.2b, we have:

- 1. The master places address and data on the buses wb.adr and wb.dat\_o, respectively. Finally the master asserts the wb.stb-signal, wb.cyc-signal, and wb.we-signal.

- 2. The slave, when ready, decodes the address bus, latches the data and asserts the wb.ack-signal.

- 3. The Master deasserts the wb.stb, wb.cyc and wb.we-signals.

- 4. The slave deasserts the wb.ack-signal.

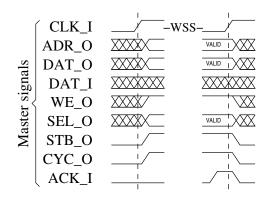

For the read cycle, see Figure 3.2c, we have:

- 1. The master places the address on the bus wb.adr and asserts the wb.stb-signal, the wb.cyc-signal, and deasserts the wb.we-signal.

- 2. The slave, when ready, decodes the address bus, places the data on the data bus wb.dat\_i and asserts the wb.ack-signal.

- 3. The Master deasserts the wb.stb and wb.cyc-signals.

- 4. The slave deasserts the wb.ack-signal.

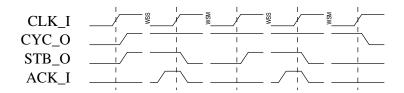

In these basic write and read bus cycles the wb.stb and wb.cyc-signals are identical. The wb.cyc-signal is used for arbitration of the bus, so the master may assert it for many cycles, for instance during a cache line refill.

#### 3.2.1 A Wishbone Interconnect

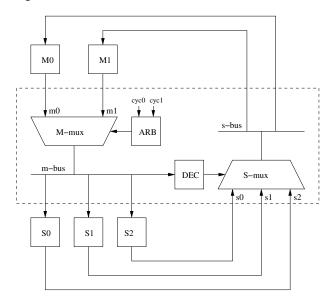

Before we begin with the actual integration of the computer we would like to give a short explanation of the Wishbone interconnect. In Figure 3.3 we show an example of 2 masters and 3 slaves connected to a Wishbone bus. The m-bus is all the signals going from the master to a slave, like the address bus, data bus and in particular the stb-signal. The s-bus is all the signals going from the slave to a master, like the data bus and the ack-signal.

Figure 3.3: A Wishbone interconnect for 2 masters and 3 slaves.

An arbiter, a finite state machine, listens to the cyc-signals from the masters. The masters MO and M1 are, in our implementation, granted the bus in a round-robin fashion. The m-bus is then connected to all the slaves. The stb-signal is, however, only asserted at the addressed slave port.

In the return path the addressed slave's s-bus is connected to all the masters. This is handled by the block DEC. The ack-signal is, however, only asserted at the master that won the arbitration.

# **3.3** A Simple Computer

# 3.3.1 General

For the lab you will have to download tsea44.tgz if you haven't done so already. Uncompress the zip-file to your home directory. Inspect the directory hw and you will find:

- the file lab1/lab1\_uart\_top.sv, a skeleton for the top file.

- the file lab1.ucf, a User Constraints File.

- the directory or1200 containing the CPU. The top file is or1200\_top.sv.

- the directory monitor containing both HW and SW for the boot monitor.

- the directory wb containing the Wishbone interconnect.

- the directory include containing some include files.

- the directory firmware, which contains the example program dct\_sw/dct\_sw that can be downloaded to your computer with the boot monitor.

## 3.3.2 A Wishbone Interface for the UART

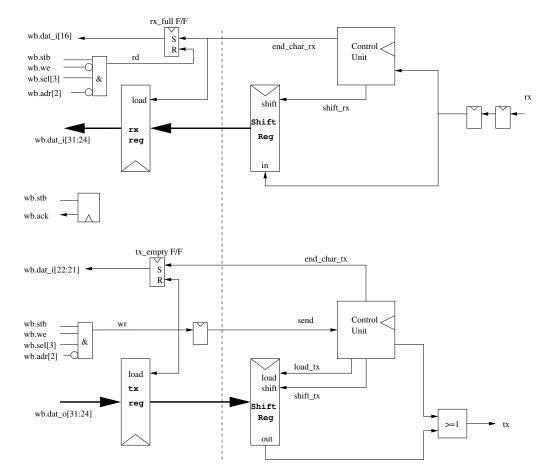

Let's start our computer design with the UART. In the introductory lab you designed a simple UART. All that is needed now is to attach a Wishbone interface to your design, see Figure 3.4.

Since you will use a boot monitor that is written for the standard 16550 UART, you will want to make your design emulate that UART.

Luckily our device driver does not use much of the functionality in the 16550. The main enhancement in the 16550 are 16 character FIFOs in both directions. This is more or less mandatory when you run an OS, which always has some interrupt latency.

The driver routine expects three bytesized registers:

- 1. transmit register, adr=0, write-only

- 2. *receive register*, adr=0, read-only

- 3. status register, adr=5, read-only

In the status register, you will only need two F/Fs:

• rx\_full, set when the stop-bit is received and reset when the receive register is read. Use signal wb\_sel[3] to determine when the receive register is read.

Figure 3.4: A sketch of the Wishbone interface for the UART. The signal load\_tx is a single-pulsed version of send. The tx\_empty F/F is connected to two wires.

• tx\_empty, set when the stop-bit has been transmitted and reset when the transmit register is written. The 16550 has two slightly different flags for this case. The monitor will work if you connect tx\_empty to both these flags.

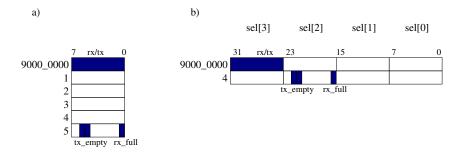

Figure 3.5 shows address maps for the UART connected to an 8 bit bus and a 32 bit bus. The *transmit register* should be placed on wb.dat\_o[31:24], the *receive register* on wb.dat\_i[31:24]. The *status register* should be placed on wb.dat\_i[23:16]. What about address decoding? The 8 most significant bits are already decoded in the wb.stb-signal. Since we are now using a 32 bit data bus, we will not use the two least significant address bits. Instead the wb.sel-signal is used to access individual data bytes. For instance wb.sel[3] is asserted when a byte on address 0x9000\_0000 or (for instance) 0x9000\_0004 is accessed. To prevent an access to 0x9000\_0004 to reset the status F/Fs, we connect wb.adr[2] to the AND gates.

#### Preparation task 2

Why must the wb.sel[3]-signal be included in the reset condition for the rx\_full *F*/*F*?

The code for the lab skeleton lab1\_uart\_top.sv is given in the listing 3.1. The

Figure 3.5: a) Address map for the UART connected to an 8 bit bus b) Address map for the UART connected to a 32 bit bus. The sel-signals are used to address individual bytes.

definition of the wishbone SystemVerilog interface can be found in the appendix section B.5.

Listing 3.1: Lab skeleton lab1\_uart\_top.sv.

```

module lab1_uart_top

(wishbone.slave wb,

output wire int_o,

input wire

srx_pad_i ,

output wire stx_pad_o);

assign int_o = 1'b0;

// Interrupt, not used in this lab

assign wb.err = 1'b0;

// Error, not used in this lab

// Retry, not used in this lab

assign wb.rty = 1'b0;

assign wb.ack = wb.stb;

// change if needed

// Here you must instantiate lab0_uart or cut and paste

// You will also have to change the interface of lab0_uart to make this work.

assign stx_pad_o = srx_pad_i; // Change this line.. :)

endmodule

```

#### Preparation task 3

Write Verilog code for the Wishbone interface of your UART.

# Preparation task 4

Inspect the driver routines getch and putch in the file monitor/firmware/src/uartfun.c. You will also have to look in uartfun.h.

#### 3.3.3 The Monitor

The monitor directory contains a couple of Verilog files that implements an 8 kB block RAM at base address 0x4001\_0000. This RAM will contain the stack of the monitor. The monitor itself is implemented in an 24 kB block ROM at base address 0x4000\_0000. The contents of the block ROM is in the Verilog file mon\_prog\_bram\_contents.v.

The software is in the sub directories firmware/src and firmware/include.

#### 3.3. A SIMPLE COMPUTER

Check mon2.c to see what the monitor does at startup so that you can verify that the hardware does the correct thing.

#### 3.3.4 Test Your Design

In Figure 3.6a we show a test bench for the computer. The only signals that the test bench has to activate in this case are the clk\_i- and rst\_i-signals. We check the behavior of the computer by listening to tx-signal from the UART. Part of a testbench has already been written for you in dafk\_tb/lab1\_tb.v. This test bench can be started with make sim\_lab1.

Remember that you may be required to change parts of the testbench also. Make sure to verify the testbench outputs to verify that both the input pattern and the output patterns are as expected.

(a) A test bench. The module uart\_tasks gives a nice printout.

| /test_v/stx_pa<br>⊕_≁/test_v/rx_data_r | StO<br>O |      |   |     | ا الل<br>۲m | ЛП.<br>(о |    | NN<br>n )   |    | <mark>}∏</mark><br>_(t | ₩₩<br>(0 | LПП<br>(; | (<br>( |           | VIII<br>XA | ]]<br>_)u |       |

|----------------------------------------|----------|------|---|-----|-------------|-----------|----|-------------|----|------------------------|----------|-----------|--------|-----------|------------|-----------|-------|

| Now                                    | )00 ps   | )    | 1 | ı I | 1           | 1 1       | 50 | l i<br>Dius | I. | 1 1                    |          |           | ' ' 1  | l i<br>ms | I          |           | 1 1 1 |

| Cursor 1                               | 0 ps     | 0 ps |   |     |             |           |    |             |    |                        |          |           |        |           |            |           |       |

(b) A test run in ModelSim, showing the signals tx and rx\_data in the test bench.

Figure 3.6: Simulation of your design

There is also a smaller test bench, lab1/uart\_tb.sv, that will test only your UART design. This test bench can be started with make sim\_uart. Remember to verify that the generated testpattern is correct, and adjust the testbench if necessary.

# Laboration task 1.1

Test your computer.

## **3.4 A Benchmark Program**

#### 3.4.1 JPEG Compression

We will use the first part, DCT, of the JPEG compression algorithm to test our computer. This section is inspired by [3]. We begin with a short discussion of how DCT works.

### 3.4.2 Integer DCT

The two dimensional discrete cosine transform (DCT) for an  $8 \times 8$  array a[x, y] is defined as

$$A[u,v] = c[u]c[v] \cdot \sum_{x=0}^{7} \sum_{y=0}^{7} a[x,y] \cos \frac{\pi u}{8} (x+\frac{1}{2}) \cos \frac{\pi v}{8} (y+\frac{1}{2})$$

(3.1)

where  $c[0] = 1/\sqrt{8}$  and c[u] = 1/2 when  $u \neq 0$ .

The transform in (3.1) can be separated. First compute a one-dimensional DCT on each row and then a one-dimensional DCT on each column.

$$A[u,v] = c[v] \cdot \sum_{y=0}^{7} \left\{ c[u] \sum_{x=0}^{7} a[x,y] \cos \frac{2\pi}{32} (2x+1)u \right\} \cos \frac{2\pi}{32} (2v+1)y \quad (3.2)$$

The innermost part of (3.1) is the 1-D DCT, which we repeat with slightly different notation:

$$A[u] = c[u] \cdot \sum_{x=0}^{7} a[x] \cos\left(\frac{2\pi}{32}(2x+1)u\right)$$

(3.3)

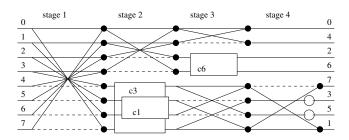

By using all possible symmetries of the cosine function it is not so difficult to figure out a fast DCT, see Figure 3.7. This computation scheme is usually referred to as Loeffler's algorithm. It computes the 1-D DCT as defined in (3.2) multiplied with  $\sqrt{8}$ .

Figure 3.7: Loeffler's original algorithm for fast DCT. Black circles means addition, dashed lines multiplication with -1 and white circles multiplication with  $\sqrt{2}$ . White boxes marked cn denote rotation with  $n\pi/16$ .

The white boxes in Figure 3.7 denote rotation with  $n\pi/16$ :

$$\begin{cases} x_{out} = x_{in} \cdot \cos n\pi/16 + y_{in} \cdot \sin n\pi/16 \\ y_{out} = -x_{in} \cdot \sin n\pi/16 + y_{in} \cdot \cos n\pi/16 \end{cases}$$

(3.4)

#### 3.4. A BENCHMARK PROGRAM

Sofar we have presented three ways of computing the 2-D DCT. We compare the computation complexity of the algorithms:

| Algorithm         | MUL  | ADD  |

|-------------------|------|------|

| Eq (3.1)          | 4096 | 4032 |

| Eq (3.2)          | 1024 | 892  |

| Loeffler original | 224  | 416  |

The post multiplication with c[u] has been left out of the table.

The OR1200 CPU has no floating point arithmetic, so the sin/cosine factors and  $\sqrt{2}$  in Figure 3.7 must be mapped to integers. We have chosen to multiply with  $2^{13}$  and rounding to the nearest integer. We have the following correspondences:

| Real number            | Integer |

|------------------------|---------|

| $\sqrt{2}$             | 11585   |

| $\cos \pi/16$          | 8035    |

| $\sin \pi/16$          | 1598    |

| $\cos 3\pi/16$         | 6811    |

| $\sin 3\pi/16$         | 4551    |

| $\sqrt{2}\cos 6\pi/16$ | 4433    |

| $\sqrt{2}\sin 6\pi/16$ | 10703   |

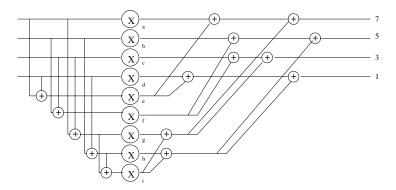

The scheme in Figure 3.7 has a serious drawback. The outputs 3 and 5 pass through two multipliers. There is, however, a modified version where this flaw has been removed at the price of 1 extra multiplier and 3 extra adders. The last 3 stages on the lower part of Figure 3.7 is replaced with the computation scheme in Figure 3.8. This modification is not, in our opinion, so easy to figure out. The interested reader is therefore directed to the original article, [4].

Figure 3.8: Loeffler's modified algorithm. Computation of the odd part with parallel multiplications.

We conclude that Loeffler's modified algorithm can be used with integer arithmetic. After each run all outputs, except 0 and 4, must be arithmetic right shifted 13 steps. The 2-D DCT will be  $8 \cdot A[u, v]$  compared to (3.2), which can be compensated for in later stages in the JPEG compression algorithm.

# Preparation task 5

Why do we go through all the trouble inserting the module in Figure 3.8? Why is it so bad having 2 multipliers in series?

#### 3.4.3 The Test Program dct\_sw

For this lab you will get a test program dct\_sw.c, written by us. It is a straightforward implementation of Loeffler's algorithm and computes the 2-D DCT of an  $8 \times 8$  image. You will actually find two copies:

- in the directory hw/firmware/dct\_sw for downloading and running on the target computer. You can also run it on the host computer.

- in the directory hw/monitor/firmware/src for simulation. A call to the DCT program has been inserted in the beginning of the monitor program mon2.c.

### **3.4.4** A Test Example

$$a[x,y] = \begin{pmatrix} 1 & 2 & 3 & 4 & 5 & 6 & 7 & 8 \\ 9 & 10 & 11 & 12 & 13 & 14 & 15 & 16 \\ 17 & 18 & 19 & 20 & 21 & 22 & 23 & 24 \\ 25 & 26 & 27 & 28 & 29 & 30 & 31 & 32 \\ 33 & 34 & 35 & 36 & 37 & 38 & 39 & 40 \\ 41 & 42 & 43 & 44 & 45 & 46 & 47 & 48 \\ 49 & 50 & 51 & 52 & 53 & 54 & 55 & 56 \\ 57 & 58 & 59 & 60 & 61 & 62 & 63 & 64 \end{pmatrix}$$

(3.5)

Origo is shown in bold text.

# **3.5** Design a Performance Counter Module

As a last task in this lab you shall design a simple performance counter module, see Figure 3.1. The module shall:

- 1. be connected to slave port 9 of the Wishbone bus.

- 2. have the port definition shown in Listing 3.2.

- 3. contain four 32 bit counters that can be read and written on the addresses  $0x9900\_0000$  to  $0x9900\_000c$ .

#### 3.5. DESIGN A PERFORMANCE COUNTER MODULE

- 4. The counter on address 0x9900\_0000 shall count the number of clock cycles that m0.cyc and m0.stb are both asserted. The counter on address 0x9900\_0004 shall count the number of clock cycles that m0.ack is asserted.

- 5. The counter on address  $0x9900\_0008$  shall count the number of clock cycles that m1.cyc and m1.stb are both asserted. The counter on address  $0x9900\_000c$  shall count the number of clock cycles that m1.ack is asserted.

- 6. Be aware that you will add extra signals (and counters) to this module in later labs to measure DMA activities.

- 7. You may optionally use the m? . we signals to gather even more statistics.

Listing 3.2: Performance counter module port definition. The definition of the wishbone SystemVerilog interface can be found in the appendix, section B.5.

```

module perf_top ( wishbone.slave wb, wishbone.monitor m0, m1 );

reg [31:0] ctr0, ctr1; // your counters

assign wb.ack = wb.stb && wb.cyc; // how to fix the ack-signal

// your code goes here

endmodule // perf_top

```

# Laboration task 1.2

Design the performance counter module and use these counters to measure the performance of the dct\_sw.c program. There is also a free running timer present in the processor. You can access it on SPR register 0x5002. In this lab you may also use the regular timer register in the processor since no operating system will modify it.

# **3.6 Useful Commands**

We have prepared a makefile based build system that is responsible for both building the monitor firmware and synthesizing the hardware from the RTL source code. You can use it on the Linux computers in Muxen 1. The following targets will be useful for you:

- make lab1 Creates a bit file of the computer in this lab task.

- make sim\_lab1 Launches Modelsim on the "lab1" system.

- make sim\_uart Launches Modelsim on your UART.

- make dafk Creates a bit file of the complete system.

- make sim Launches Modelsim on the complete system.

- make simfiles Recompiles all source files for use with Modelsim but does not launch Modelsim itself. This is mainly useful if you already have Modelsim running and want to try out some changes to your source code. This way you don't need to close Modelsim, it is enough to issue a restart command in Modelsim.

- make clean Removes intermediate files and backup files.

- make updatebit Compiles the monitor and updates dafk.bit, and lab1.bit with the new monitor. This way you don't need to resynthesize the design to test changes in your monitor. The updated bit file is named updated\_dafk.bit for dafk.bit and so on.

We also have some utilities that you might be interested in. The first of these is download.sh which you can use to download your design.Invoke it as in the following example:

```

utils/download.sh dafk.bit

```

Another utility is designed to highlight the error and warning messages in the various reports that the Xilinx flow will output. Use it on (for example) the synthesis report with the following command:

```

make dafk.bit | utils/checklogs.pl

```

#### 3.6.1 Synthesis Reports

If you use make, the following files will be of special interest to you: (look in /tmp/<your name>/synthdir

- precision.log: Synthesis report

- foo\_map.mrp: Map report

- foo.par: Place and Route report

- foo\_timing.rep: Timing analyzer report

(Where foo is the name of the top level file you compiled, as in dafk or lab1).

# **3.7** How to get Started Writing/Executing C Programs

A good starting point is the program simpleprog situated in the directory firmware. It can be compiled with make in Linux.

The executable file is simpleprog.hex which can be downloaded with the command l in the monitor and File->Send Raw File in gtkterm. You run the program with g 2000 or just g.

The size of the DRAM is 64 MB, so there is plenty of room for your program. You can check the length of the program by looking inside the file simpleprog.txt, which is a disassembled version of simpleprog. The length of simpleprog is 2800 bytes.

#### 3.7.1 A Note on Volatile

Normally, the compiler assumes that memory locations will not change unless the program itself changes it. This assumption does not hold when the program tries to access I/O memory. For example, in the following code shown in Listing 3.3, the programmer wants the program to wait until pin 1 of the parallel port is set to 1. The problem is that an optimizing compiler will generate assembler code doing approximately what is shown in Listing 3.4.

Listing 3.3: Volatile is not used for memory mapped I/O.

| 8                                | 5 11                                    |

|----------------------------------|-----------------------------------------|

| <b>unsigned</b> int *parport = 0 | )x91000000;                             |

| while ((* parport & 0x1) !=      | = 1); /* Busy wait */                   |

|                                  |                                         |

| Listing 3.4: Resulting           | ng assembler from code in Listing 3.3.  |

| LOAD R0,[0x91000000]             | ; Load value from memory                |

| AND $R0, R0, 0x1$                | ; And R0 with 1                         |

| CMP $R0, 0x1$                    | ; Compare R0 with 1                     |

| loop :                           |                                         |

| BNEQ loop                        | ; Jump to loop if R0 was not equal to 1 |

|                                  |                                         |

This is certainly not what the programmer had in mind. This kind of error is even more insidious because in some cases it might work ok and in some cases it will fail sporadically and in some cases it might not work at all. It will also depend on the optimization level of the compiler. The correct way to deal with this situation is to tell the C compiler that the memory location can change at any time. This will force the compiler to generate code that reloads the memory location every time it is referenced. This can be done using the volatile keyword. We recommend that you use the macros shown in Listing 3.5 to access memory mapped I/O. These macros are defined in both the monitor (mon2.h) and in jpeglib.h but if you write a small test program you might have to include them in your own source code as well. Using these macros<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>The macros assume that a long is 32 bits, a short is 16 bits and a char is 8 bits.

the program from Listing 3.3 would look like whats shown in Listing 3.6.

Listing 3.5: Recommended macros for memory mapped I/O access.

```

#define REG32(add) *((volatile unsigned long *)(add))

#define REG16(add) *((volatile unsigned short *)(add))

#define REG8(add) *((volatile unsigned char *)(add))

```

Listing 3.6: Correct program, using volatile.

| $((12052(0X)100000)) \approx 0X1) = 1), 7* Duby wall *7$ | while ((REG32(0x91000000) | & 0x1) != | 1); /* | Busy | wait | */ |

|----------------------------------------------------------|---------------------------|-----------|--------|------|------|----|

|----------------------------------------------------------|---------------------------|-----------|--------|------|------|----|

#### 3.7.2 What to Include in the Lab Report

46

The lab report should contain all source code that you have written. (The source code should of course be commented.) We would also like you to include a block diagram of your hardware. If you have written any FSM you should include a state diagram graph of the FSM.

We would also like you to discuss the following questions:

- How did you verify that your computer hardware worked?

- What is the performance of the 2D DCT software? (Try it with and without caches.)

- How much of the FPGA is used by our design?

And of course, the normal parts of a lab report such as a table of contents, an introduction, a conclusion, etc. The source code that you have written should be included in appendices and referred to from the main document.

# **Chapter 4**

# Lab task 2 - Design a JPEG accelerator

# 4.1 The lab system

In this lab task you will learn how to build a hardware accelerator for the JPEG image compression algorithm. In this lab you will use the build target dafk.bit. This is a complete system with the following components:

- OR1200 CPU

- Boot monitor

- UART

- VGA controller

- Camera controller

- Ethernet controller

- SDRAM, SRAM, and flash memory controller

$\mu$ Clinux is programmed into the flash memory on the FPGA board and we will use this operating system for the remainder of this course. Examples of how to compile for Linux are included in the lab skeleton in the hello directory.

# 4.2 **Proposed architecture**

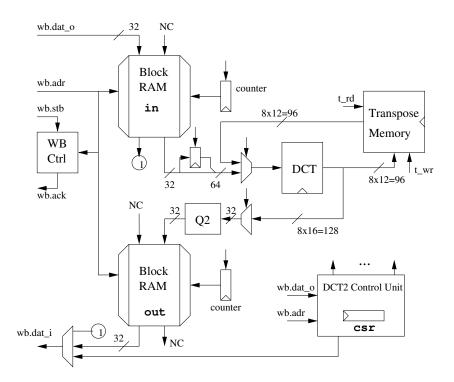

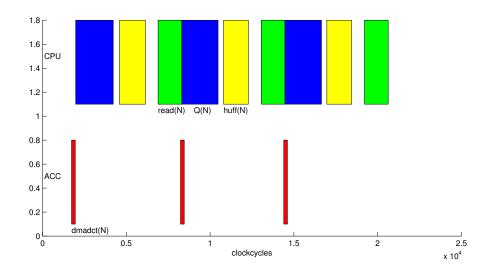

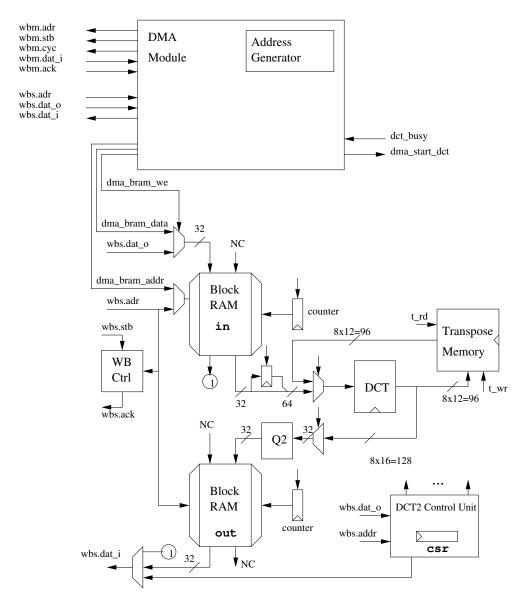

We propose the general architecture shown in Figure 4.1. It works in the following way:

1. An  $8 \times 8$  bytes image is written from the Wishbone bus by the application program to the in RAM in 16 write cycles. Pixels are 8-bit positive numbers and packed in one 32-bit word. We recommend that you subtract 128 from each pixel before it is written to the in RAM. The accelerator is then started by setting the START bit in csr (Control/Status Register).

Figure 4.1: Proposed architecture for the 2-D DCT-accelerator. csr is a Control/Status register. Not all wires are shown.

- 2. A row of the image is read from the in RAM in 2 clock cycles. This is repeated 8 times.

- 3. The rows are transformed in DCT (12-bit signed numbers) and written to the transpose memory in the same tempo

- 4. When all rows have been written to T, columns, 8 × 12 bits, can be read from T and fed into the DCT again. A complete column can be read per clock cycle. After the second DCT the values are 16-bit signed numbers.

- 5. Finally  $2 \times 16$  bits per clock cycle are quantized in Q2 and written to the out RAM. When all columns have been written, the RDY bit in csr is set.

You will receive a Verilog module, dct.v, that computes a 1-D DCT multiplied with  $\sqrt{8}$ . This file is a straightforward implementation in Verilog of the computation schemes (modified Loeffler) in Figures 3.7 and 3.8 in Chapter 3.

#### Preparation task 6

Open the file dct.v and have a look at what it does. What are the inputs, what are the outputs? How many clock cycles does a computation take? Is it pipelined?

#### 4.2.1 Block RAMs in VirtexII

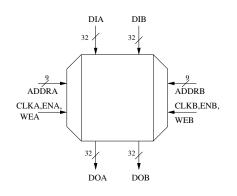

The VirtexII-4000 FPGA contains 120 18 kbit block RAMs. They are dual ported with two completely independent sets of synchronous read and write ports. The easiest way

to use a block RAM is, in our opinion, to instantiate a library primitive. The code in Listing 4.1 instantiates a block RAM shown in Figure 4.2.

SSR is a set/reset signal, that only affects the output latches, not the RAM memory cells. DIP and DOP can be used for additional data such as parity bits but we do not use them in this lab. It is important to understand that both reads and writes are synchronous as opposed to an ordinary RAM that you might have used in one of our earlier courses such as *Digital Konstruktion*.

Listing 4.1: Instantiation of a block RAM as shown in Figure 4.2

```

wire [31:0] doa, dia, dob, dib;

wire [8:0] addra, addrb;

wire clk, cea, wea, ceb, web;

// dual port 512x32 RAM

RAMB16_S36_S36 memory (

// port A

.DOA(doa), .DOPA(), .ADDRA(addra),.CLKA(c1k),

.DIA(dia), .DIPA(4'h0), .ENA(cea), .SSRA(1'b0), .WEA(wea),

// port B

.DOB(dob), .DOPB(), .ADDRB(addrb),.CLKB(c1k), .DIB(dib),

.DIPB(4'h0), .ENB(ceb), .SSRB(1'b0), .WEB(web));

```

Figure 4.2: Dualported  $512 \times 32$  bit block RAM.

#### 4.2.2 Distributed RAMs

Small RAMs can be designed using the LUTs in the FPGA. A LUT is a  $16 \times 1$  RAM. Distributed RAM memory supports the following:

- Single-port RAM with one synchronous write and one combinatorial read port

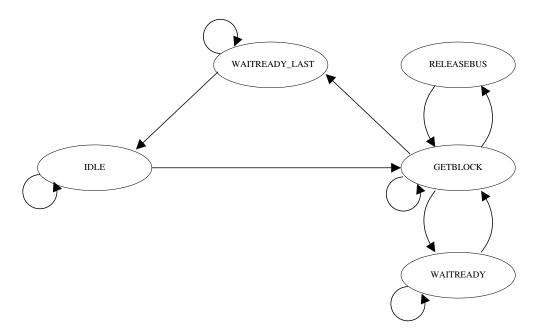

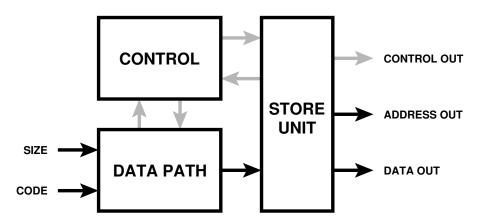

- Dual-port RAM with one synchronous write port and two asynchronous read ports