# OpenRISC 1000 Architecture Manual

January 28, 2003

Copyright (C) 2000, 2001, 2002, 2003 OPENCORES.ORG and Authors

This document is free; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 2 of the License, or (at your option) any later version.

This document is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details.

## **Table of Contents**

| 1 | AB   | OUT THIS MANUAL                                      | 10  |

|---|------|------------------------------------------------------|-----|

|   | 1.1  | INTRODUCTION                                         | 10  |

|   | 1.2  | AUTHORS                                              | 10  |

|   | 1.3  | REVISION HISTORY                                     | 11  |

|   | 1.4  | WORK IN PROGRESS                                     | 12  |

|   | 1.5  | FONTS IN THIS MANUAL                                 | 12  |

|   | 1.6  | CONVENTIONS                                          | 12  |

|   | 1.7  | NUMBERING                                            | 13  |

| 2 | AR   | CHITECTURE OVERVIEW                                  | 14  |

|   | 2.1  | FEATURES                                             | 14  |

|   | 2.2  | INTRODUCTION                                         | 14  |

| 3 | AD   | DRESSING MODES AND OPERAND CONVENTIONS               | 16  |

|   | 3.1  | MEMORY ADDRESSING MODES                              | 16  |

|   | 3.1. | g p                                                  |     |

|   | 3.1. |                                                      |     |

|   | 3.2  |                                                      |     |

|   | 3.2. | , ,                                                  |     |

|   | 3.2. | 3                                                    |     |

| 4 | RE   | GISTER SET                                           |     |

|   | 4.1  | FEATURES                                             |     |

|   | 4.2  | OVERVIEW                                             |     |

|   | 4.3  | SPECIAL-PURPOSE REGISTERS                            |     |

|   | 4.4  | GENERAL-PURPOSE REGISTERS (GPRS)                     |     |

|   | 4.5  | SUPPORT FOR CUSTOM NUMBER OF GPRS                    |     |

|   | 4.6  | SUPERVISION REGISTER (SR)                            |     |

|   | 4.7  | EXCEPTION PROGRAM COUNTER REGISTERS (EPCR0 - EPCR15) |     |

|   | 4.8  | EXCEPTION EFFECTIVE ADDRESS REGISTERS (EEAR0-EEAR15) |     |

|   | 4.9  | EXCEPTION SUPERVISION REGISTERS (ESR0-ESR15)         |     |

|   | 4.10 | NEXT AND PREVIOUS PROGRAM COUNTER (NPC AND PPC)      |     |

| 5 |      | TRUCTION SET                                         |     |

|   |      | FEATURES                                             |     |

|   | 5.2  | OVERVIEW                                             |     |

|   | 5.3  | ORBIS32/64                                           |     |

|   | 5.4  | ORFPX32/64                                           |     |

|   | 5.5  | ORVDX32/64                                           | 149 |

| 6 | EX   | CEPTION MODEL                                        | 261 |

|   | 6.1  | INTRODUCTION                                         | 261 |

|   | 6.2          | EXCEPTION CLASSES                                                                           | 261 |

|---|--------------|---------------------------------------------------------------------------------------------|-----|

|   | 6.3          | EXCEPTION PROCESSING                                                                        |     |

|   | 6.4          | FAST CONTEXT SWITCHING (OPTIONAL)                                                           | 264 |

|   | 6.4.         | .1 Changing Context in Supervisor Mode                                                      | 264 |

|   | 6.4.         |                                                                                             |     |

|   | 6.4.         |                                                                                             |     |

| 7 | MEI          | MORY MODEL                                                                                  |     |

|   | 7.1          | MEMORY                                                                                      | _   |

|   | 7.2          | MEMORY ACCESS ORDERING                                                                      |     |

|   | 7.2.         | · · · · · · · · · · · · · · · · · · ·                                                       |     |

|   | 7.2.         |                                                                                             |     |

|   | 7.3          | ATOMICITY                                                                                   |     |

| 8 | ME           | MORY MANAGEMENT                                                                             |     |

|   | 8.1          | MMU FEATURES                                                                                |     |

|   | 8.2          | MMU OVERVIEW                                                                                |     |

|   | 8.3          | MMU EXCEPTIONS                                                                              |     |

|   | 8.4          | MMU SPECIAL-PURPOSE REGISTERS                                                               |     |

|   | 8.4.         | • • • • • • • • • • • • • • • • • • • •                                                     |     |

|   | 8.4.<br>8.4. | ,                                                                                           |     |

|   | 8.4.         | - , , , , , , , , , , , , , , , , , , ,                                                     |     |

|   | 8.4.         | • ,                                                                                         |     |

|   | 8.4.         |                                                                                             |     |

|   | •            | LBWyMR0-xTLBWyMR127)                                                                        |     |

|   | 8.4.<br>DTL  | LBWyTR127)                                                                                  | 278 |

|   |              | .8 Instruction Translation Lookaside Buffer Way y Translate Regi<br>LBWyTR0-ITLBWyTR127)    | 279 |

|   | 8.4.<br>xAT  | .9 Instruction/Data Area Translation Buffer Match Registers (xATB<br>ΓΒΜR3)                 |     |

|   | 8.4.         | •                                                                                           |     |

|   | 8.4.         | <ul><li>Instruction Area Translation Buffer Translate Registers (IATBTR0-IATE 283</li></ul> | TR3 |

|   | 8.5          | ADDRESS TRANSLATION MECHANISM IN 32-BIT IMPLEMENTATIONS                                     | 284 |

|   | 8.6          | ADDRESS TRANSLATION MECHANISM IN 64-BIT IMPLEMENTATIONS                                     | 287 |

|   | 8.7          | MEMORY PROTECTION MECHANISM                                                                 | 290 |

|   | 8.8          | PAGE TABLE ENTRY DEFINITION                                                                 | 291 |

|   | 8.9          | PAGE TABLE SEARCH OPERATION                                                                 | 293 |

|   | 8.10         | PAGE HISTORY RECORDING                                                                      | 293 |

|   | 8.11         | PAGE TABLE UPDATES                                                                          | 293 |

| 9 | CA           | CHE MODEL & CACHE COHERENCY                                                                 | 295 |

|   | 9.1          | CACHE SPECIAL-PURPOSE REGISTERS                                                             | 295 |

|   | 9.1.         | = = = 9                                                                                     |     |

|   | 9.1.         | .2 Instruction Cache Control Register                                                       | 296 |

|   | 9.2          | CACHE MANAGEMENT                                                                            | 297 |

|    | 9.2.1               | Data Cache Block Prefetch (Optional)               | 297 |

|----|---------------------|----------------------------------------------------|-----|

|    | 9.2.2               | Data Cache Block Flush                             | 298 |

|    | 9.2.3               | Data Cache Block Invalidate                        | 298 |

|    | 9.2.4               |                                                    |     |

|    | 9.2.5               | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \              |     |

|    | 9.2.6               | <b>\ 1</b>                                         |     |

|    | 9.2.7               |                                                    |     |

|    | 9.2.8               | ` . ,                                              |     |

|    | 9.3<br><b>9.3.1</b> | CACHE/MEMORY COHERENCY                             |     |

|    | 9.3.1               |                                                    |     |

|    | 9.3.3               |                                                    |     |

| 10 |                     | UG UNIT (OPTIONAL)                                 |     |

| 10 | 10.1                | FEATURES                                           |     |

|    | 10.1                | DEBUG VALUE REGISTERS (DVR0-DVR7)                  |     |

|    | 10.2                | DEBUG CONTROL REGISTERS (DCR0-DCR7)                |     |

|    | 10.3                | DEBUG MODE REGISTER 1 (DMR1)                       |     |

|    | 10.4                | DEBUG MODE REGISTER 2(DMR2)                        |     |

|    | 10.6                | DEBUG WATCHPOINT COUNTER REGISTER (DWCR0-DWCR1)    |     |

|    | 10.7                | DEBUG STOP REGISTER (DSR)                          |     |

|    | 10.8                | DEBUG REASON REGISTER (DRR)                        |     |

| 11 |                     | FORMANCE COUNTERS UNIT (OPTIONAL)                  |     |

|    | 11.1                | FEATURES                                           |     |

|    | 11.2                | PERFORMANCE COUNTERS COUNT REGISTERS (PCCR0-PCCR7) |     |

|    | 11.3                | PERFORMANCE COUNTERS COUNT REGISTERS (PCCR0-PCCR7) |     |

| 40 |                     | ,                                                  |     |

| 12 |                     | /ER MANAGEMENT (OPTIONAL)                          |     |

|    | 12.1                | FEATURES                                           |     |

|    | 12.2                | POWER MANAGEMENT REGISTER (PMR)                    |     |

| 13 |                     | GRAMMABLE INTERRUPT CONTROLLER (OPTIONAL)          |     |

|    | 13.1                | FEATURES                                           |     |

|    | 13.2                | PIC MASK REGISTER (PICMR)                          |     |

|    | 13.3                | PIC STATUS REGISTER (PICSR)                        |     |

| 14 |                     | TIMER FACILITY (OPTIONAL)                          |     |

|    | 14.1                | FEATURES                                           |     |

|    | 14.2                | TICK TIMER MODE REGISTER (TTMR)                    |     |

|    | 14.3                | TICK TIMER COUNT REGISTER (TTCR)                   | 322 |

| 15 | OPE                 | NRISC 1000 IMPLEMENTATIONS                         | 324 |

|    | 15.1                | OVERVIEW                                           | 324 |

|    | 15.2                | VERSION REGISTER (VR)                              |     |

|    | 15.3                | UNIT PRESENT REGISTER (UPR)                        | 325 |

|    | 15.4                | CPU CONFIGURATION REGISTER (CPUCFGR)               |     |

|    | 15.5                | DMMU CONFIGURATION REGISTER (DMMUCFGR)             |     |

|    | 15.6                | IMMU CONFIGURATION REGISTER (IMMUCFGR)             | 328 |

|    | 15.7  | DC CONFIGURATION REGISTER (DCCFGR)                 | 329     |

|----|-------|----------------------------------------------------|---------|

|    | 15.8  | IC CONFIGURATION REGISTER (ICCFGR)                 | 330     |

|    | 15.9  | DEBUG CONFIGURATION REGISTER (DCFGR)               | 332     |

|    | 15.10 | PERFORMANCE COUNTERS CONFIGURATION REGISTER (PCCFG | GR) 332 |

| 16 | APP   | LICATION BINARY INTERFACE                          | 333     |

|    | 16.1  | DATA REPRESENTATION                                | 333     |

|    | 16.1  | 1 Fundamental Types                                | 333     |

|    | 16.1  | 2 Aggregates and Unions                            | 334     |

|    | 16.1  | 3 Bit-fields                                       | 335     |

|    | 16.2  | FUNCTION CALLING SEQUENCE                          | 336     |

|    | 16.2  | 1 Register Usage                                   | 336     |

|    | 16.2  | 2 The Stack Frame                                  | 338     |

|    | 16.2  | 3 Parameter Passing                                | 338     |

|    | 16.2  | 4 Functions Returning Scalars or No Value          | 338     |

|    | 16.2  | 5 Functions Returning Structures or Unions         | 339     |

|    | 16.3  | OPERATING SYSTEM INTERFACE                         | 339     |

|    | 16.3  | 1 Exception Interface                              | 339     |

|    | 16.3  | 2 Virtual Address Space                            | 340     |

|    | 16.3  | 3 Page Size                                        | 340     |

|    | 16.3  | 4 Virtual Address Assignments                      | 340     |

|    | 16.3  | 5 Stack                                            | 341     |

|    | 16.3  | 6 Processor Execution Modes                        | 341     |

|    | 16.4  | POSITION-INDEPENDENT CODE                          | 341     |

|    | 16.5  | ELF                                                | 341     |

|    | 16.5  | 1 Header Convention                                | 341     |

|    | 16.5  | 2 Sections                                         | 342     |

|    | 16.5  | 3 Relocation                                       | 342     |

|    | 16.6  | COFF                                               | 343     |

|    | 16.6  | 1 Sections                                         | 343     |

|    | 16.6  |                                                    |         |

## **Table Of Figures**

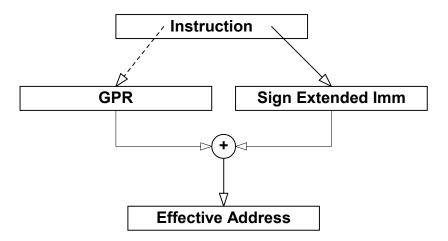

| Figure 3-1. Register Indirect with Displacement Addressing                                                        | 16  |

|-------------------------------------------------------------------------------------------------------------------|-----|

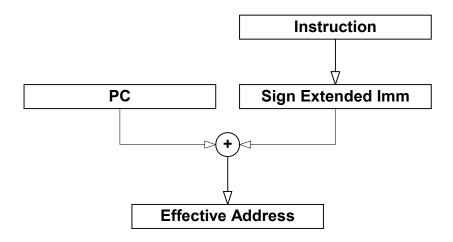

| Figure 3-2. PC Relative Addressing                                                                                | 17  |

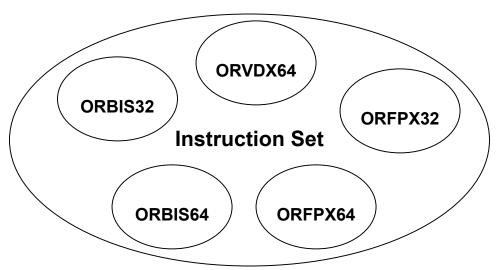

| Figure 5-1. Instruction Set                                                                                       | 29  |

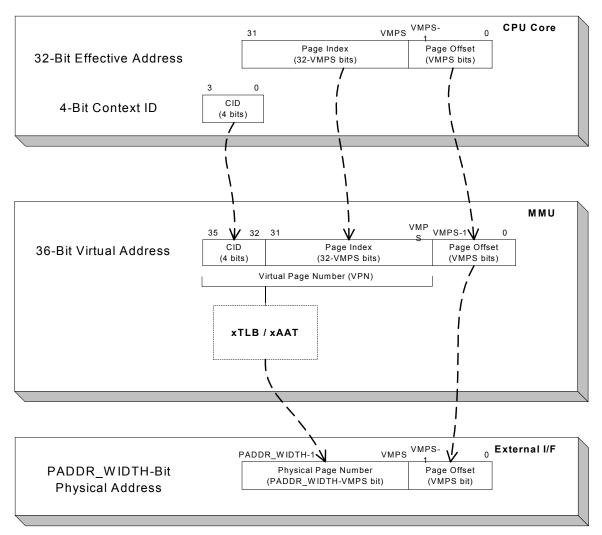

| Figure 8-1. Translation of Effective to Physical Address – Simplified block diagram for processor implementations |     |

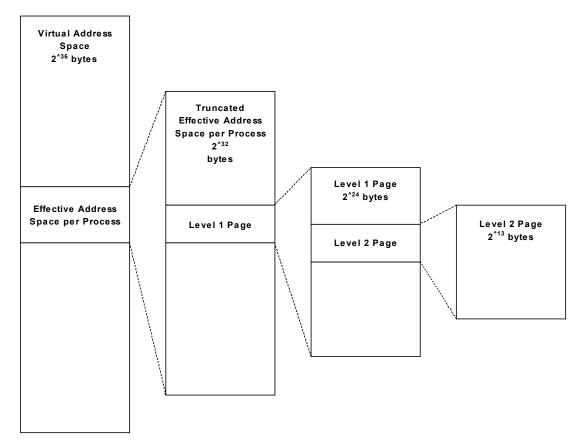

| Figure 8-2. Memory Divided Into L1 and L2 pages                                                                   | 284 |

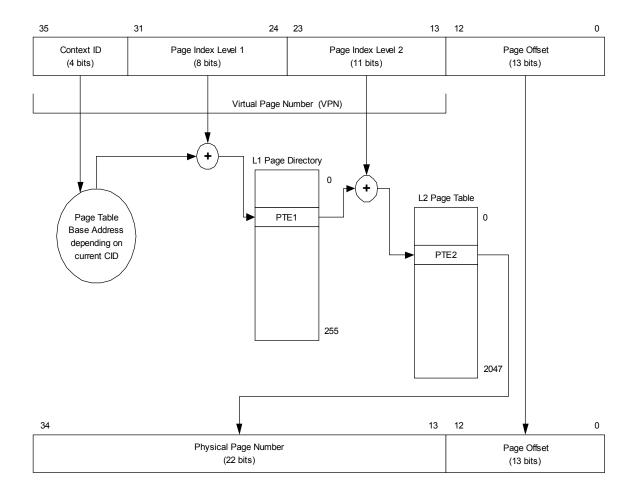

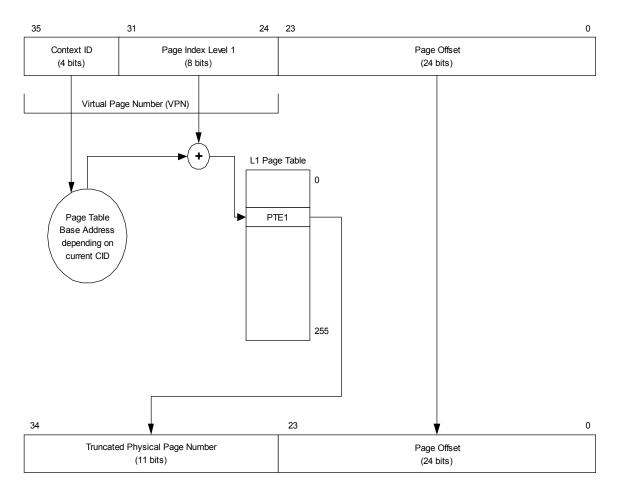

| Figure 8-3. Address Translation Mechanism using Two-Level Page Table                                              | 285 |

| Figure 8-4. Address Translation Mechanism using only L1 Page Table                                                | 286 |

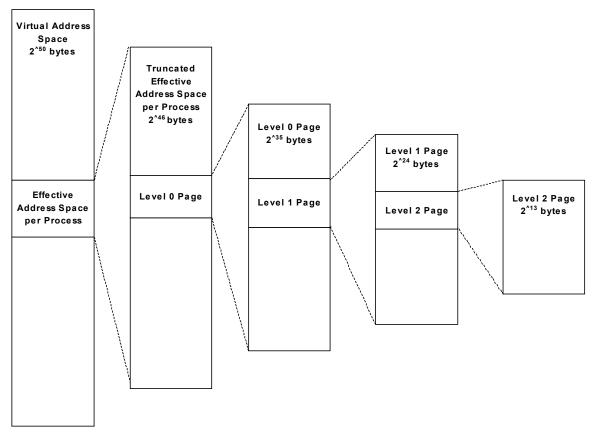

| Figure 8-5. Memory Divided Into L0, L1 and L2 pages                                                               | 287 |

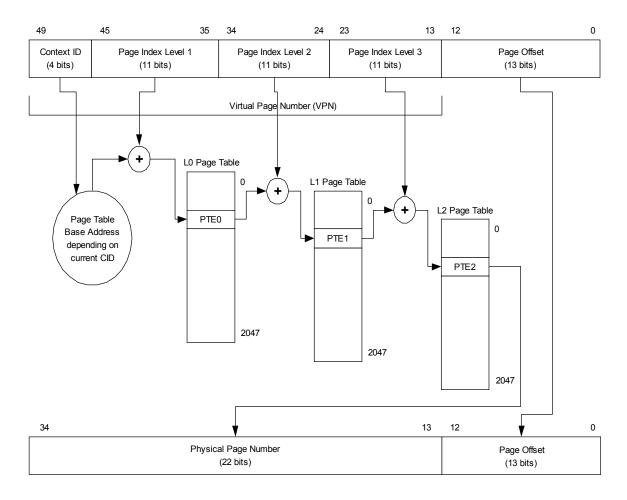

| Figure 8-6. Address Translation Mechanism using Three-Level Page Table                                            | 288 |

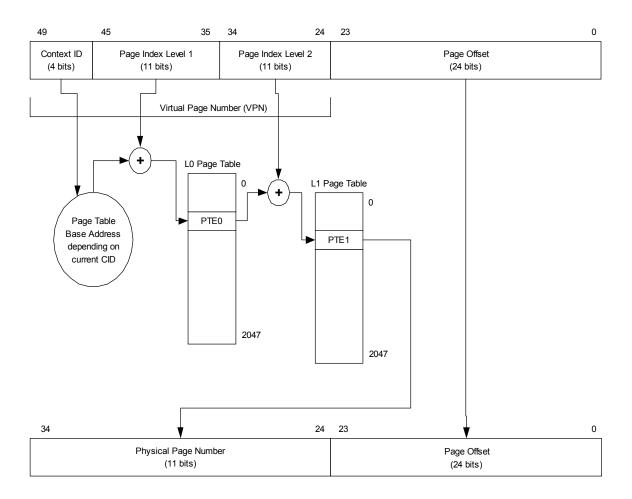

| Figure 8-7. Address Translation Mechanism using Two-Level Page Table                                              | 289 |

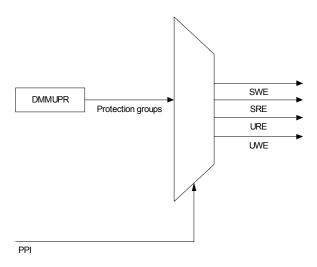

| Figure 8-8. Selection of Page Protection Attributes for Data Accesses                                             | 291 |

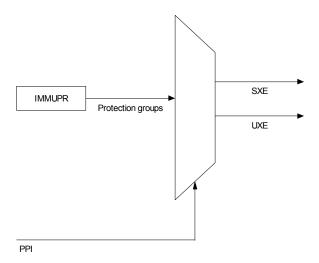

| Figure 8-9. Selection of Page Protection Attributes for Instruction Fetch Accesses                                | 291 |

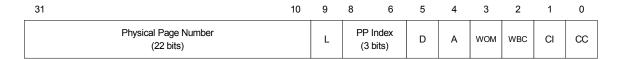

| Figure 8-10. Page Table Entry Format                                                                              | 292 |

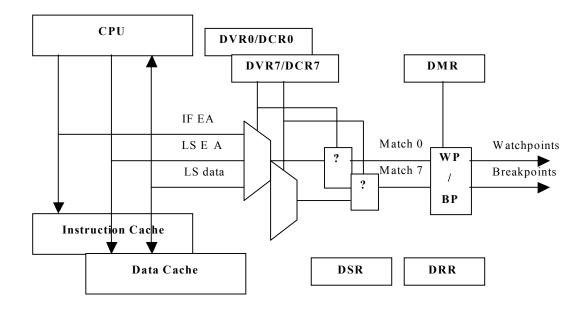

| Figure 10-1. Block Diagram of Debug Support                                                                       | 305 |

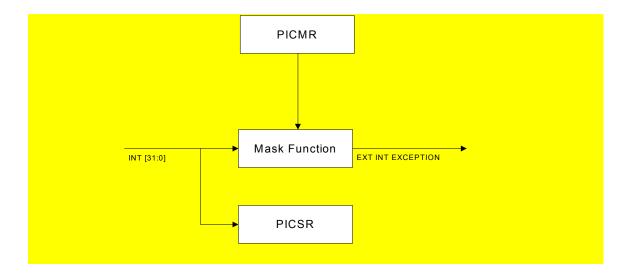

| Figure 13-1. Programmable Interrupt Controller Block Diagram                                                      | 319 |

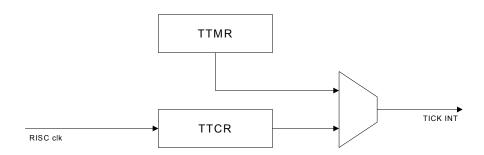

| Figure 14-1. Tick Timer Block Diagram                                                                             | 321 |

| Figure 16-1. Byte aligned, sizeof is 1                                                                            | 334 |

| Figure 16-2. No padding, sizeof is 8                                                                              |     |

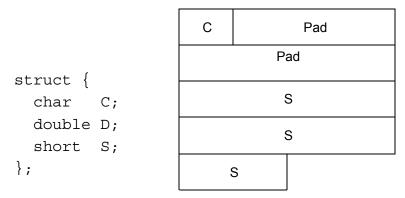

| Figure 16-3. Padding, sizeof is 18                                                                                | 335 |

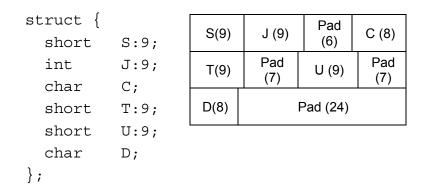

| Figure 16-4. Storage unit sharingand alignment padding, sizeof is 12                                              | 336 |

## **Table Of Tables**

| Table 1-1. Acronyms and Abbreviations                                                      | 9   |

|--------------------------------------------------------------------------------------------|-----|

| Table 1-1. Authors of this Manual                                                          | 10  |

| Table 1-2. Revision History                                                                | 11  |

| Table 1-3. Conventions                                                                     | 13  |

| Table 3-1. Memory Operands and their sizes                                                 | 18  |

| Table 3-2. Default Bit and Byte Ordering in Halfwords                                      | 18  |

| Table 3-3. Default Bit and Byte Ordering in Singlewords and Single Precision Floats        | 18  |

| Table 3-4. Default Bit and Byte Ordering in Doublewords, Double Precision Floats and Types |     |

| Table 3-5. Memory Operand Alignment                                                        |     |

| Table 4-1. Groups of SPRs                                                                  |     |

| Table 4-2. List of All Special-Purpose Registers                                           |     |

| Table 4-3. General-Purpose Registers                                                       |     |

| Table 4-4. SR Field Descriptions                                                           |     |

| Table 4-5. EPCR Field Descriptions                                                         |     |

| Table 4-6. EEAR Field Descriptions                                                         |     |

| Table 4-7. ESR Field Descriptions                                                          |     |

| Table 5-1. OpenRISC 1000 Instruction Classes                                               | 30  |

| Table 6-1. Exception Classes                                                               | 261 |

| Table 6-2. Exception Types and Causal Conditions                                           | 262 |

| Table 6-3. Values of EPCR and EEAR After Exception                                         | 264 |

| Table 8-1. MMU Exceptions                                                                  | 271 |

| Table 8-2. List of MMU Special-Purpose Registers                                           | 273 |

| Table 8-3. DMMUCR Field Descriptions                                                       | 273 |

| Table 8-4. DMMUPR Field Descriptions                                                       | 274 |

| Table 8-5. IMMUCR Field Descriptions                                                       | 275 |

| Table 8-6. IMMUPR Field Descriptions                                                       | 276 |

| Table 8-7. xTLBEIR Field Descriptions                                                      | 276 |

| Table 8-8. xTLBMR Field Descriptions                                                       | 277 |

| Table 8-9. DTLBTR Field Descriptions                                                       | 279 |

| Table 8-10. ITLBWyTR Field Descriptions                                                    |     |

| Table 8-11. xATBMR Field Descriptions                                                      | 281 |

| Table 8-12. DATBTR Field Descriptions                                                      | 282 |

| Table 8-13. IATBTR Field Descriptions                                                      |     |

| Table 8-14. Protection Attributes                                                          | 290 |

| Table 8-15. PTE Field Descriptions                                                         |     |

| Table 9-1. Cache Registers                                                                 |     |

| Table 9-2. DCCR Field Descriptions                                                         | 296 |

| Table 9-3 ICCR Field Descriptions                                                          | 297 |

| Table 9-4. DCBPR Field Descriptions         | 298 |

|---------------------------------------------|-----|

| Table 9-5. DCBFR Field Descriptions         | 298 |

| Table 9-6. DCBIR Field Descriptions         | 299 |

| Table 9-7. DCBWR Field Descriptions         | 300 |

| Table 9-8. DCBLR Field Descriptions         | 300 |

| Table 9-9. ICBPR Field Descriptions         | 301 |

| Table 9-10. ICBIR Field Descriptions        | 301 |

| Table 9-11. ICBLR Field Descriptions        | 302 |

| Table 10-1. DVR Field Descriptions          | 305 |

| Table 10-2. DCR Field Descriptions          | 306 |

| Table 10-3. DMR1 Field Descriptions         | 308 |

| Table 10-4. DMR2 Field Descriptions         | 309 |

| Table 10-5. DWCR Field Descriptions         | 310 |

| Table 10-6. DSR Field Descriptions          | 311 |

| Table 10-7. DRR Field Descriptions          | 313 |

| Table 11-1. PCCR0 Field Descriptions        | 315 |

| Table 11-2. PCMR Field Descriptions         | 316 |

| Table 12-1. PMR Field Descriptions          | 318 |

| Table 13-1. PICMR Field Descriptions        | 320 |

| Table 13-2. PICSR Field Descriptions        | 320 |

| Table 14-1. TTMR Field Descriptions         | 322 |

| Table 14-2. TTCR Field Descriptions         | 323 |

| Table 15-1. VR Field Descriptions           | 325 |

| Table 15-2. UPR Field Descriptions          | 326 |

| Table 15-3. CPUCFGR Field Descriptions      | 327 |

| Table 15-4. DMMUCFGR Field Descriptions     | 328 |

| Table 15-5. IMMUCFGR Field Descriptions     | 329 |

| Table 15-6. DCCFGR Field Descriptions       | 330 |

| Table 15-7. ICCFGR Field Descriptions       | 331 |

| Table 15-8. DCFGR Field Descriptions        | 332 |

| Table 15-9. PCCFGR Field Descriptions       | 332 |

| Table 16-1. Scalar Types                    | 333 |

| Table 16-2. Vector Types                    | 334 |

| Table 16-3. Bit-Field Types and Ranges      | 335 |

| Table 16-4. General-Purpose Registers       | 337 |

| Table 16-5. Stack Frame                     | 338 |

| Table 16-6. Hardware Exceptions and Signals | 339 |

| Table 16-7. Virtual Address Configuration   | 340 |

| Table 16-8. e_ident Field Values            | 342 |

| Table 16-9. e_flags Field Values            | 342 |

## **Acronyms & Abbreviations**

| ALU   | Arithmetic Logic Unit             |

|-------|-----------------------------------|

| ATB   | Area Translation Buffer           |

| BIU   | Bus Interface Unit                |

| BTC   | Branch Target Cache               |

| CPU   | Central Processing Unit           |

| DC    | Data Cache                        |

| DMMU  | Data MMU                          |

| DTLB  | Data TLB                          |

| DU    | Debug Unit                        |

| EA    | Effective address                 |

| FPU   | Floating-Point Unit               |

| GPR   | General-Purpose Register          |

| IC    | Instruction Cache                 |

| IMMU  | Instruction MMU                   |

| ITLB  | Instruction TLB                   |

| MMU   | Memory Management Unit            |

| OR1K  | OpenRISC 1000 Architecture        |

| ORBIS | OpenRISC Basic Instruction Set    |

| ORFPX | OpenRISC Floating-Point eXtension |

| ORVDX | OpenRISC Vector/DSP eXtension     |

| PC    | Program Counter                   |

| PCU   | Performance Counters Unit         |

| PIC   | Programmable Interrupt Controller |

| PM    | Power Management                  |

| PTE   | Page Table Entry                  |

| R/W   | Read/Write                        |

| RISC  | Reduced Instruction Set Computer  |

| SMP   | Symmetrical Multi-Processing      |

| SMT   | Simultaneous Multi-Threading      |

| SPR   | Special-Purpose Register          |

| SR    | Supervison Register               |

| TLB   | Translation Lookaside Buffer      |

| ·     |                                   |

Table 1-1. Acronyms and Abbreviations

## 1 About this Manual

#### 1.1 Introduction

The OpenRISC 1000 system architecture manual defines the architecture for a family of open-source, synthesizable RISC microprocessor cores. The OpenRISC 1000 architecture allows for a spectrum of chip and system implementations at a variety of price/performance points for a range of applications. It is a 32/64-bit load and store RISC architecture designed with emphasis on performance, simplicity, low power requirements, and scalability. The OpenRISC 1000 architecture targets medium and high performance networking and embedded computer environments.

This manual covers the instruction set, register set, cache management and coherency, memory model, exception model, addressing modes, operands conventions, and the application binary interface (ABI).

This manual does not specify implementation-specific details such as pipeline depth, cache organization, branch prediction, instruction timing, bus interface etc.

#### 1.2 Authors

If you have contributed to this manual but your name isn't listed here, it is not meant as a slight – We simply don't know about it. Send an email to the maintainer(s), and we'll correct the situation.

| Name             | E-mail                     | Contribution                     |

|------------------|----------------------------|----------------------------------|

| Damjan Lampret   | lampret@opencores.org      | Initial document                 |

| Chen-Min Chen    | jimmy@ee.nctu.edu.tw       | Some notes                       |

| Marko Mlinar     | markom@opencores.org       | Fast context switches            |

| Johan Rydberg    | jrydberg@opencores.org     | ELF section                      |

| Matan Ziv-Av     | matan@svgalib.org          | Several suggestions              |

| Chris Ziomkowski | chris@opencores.org        | Several suggestions              |

| Greg McGary      | greg@mcgary.org            | I.cmov, trap exception           |

| Bob Gardner      |                            | Native Speaker Check             |

| Rohit Mathur     | rohitmathurs@opencores.org | Technical review and corrections |

| Maria Bolado     | mbolado@teisa.unican.es    | Technical review and corrections |

Table 1-1. Authors of this Manual

#### 1.3 Revision History

The revision history of this manual is presented in the table below.

| Revision Date     | Ву                | Modifications                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15/Mar/2000       | Damjan Lampret    | Initial document                                                                                                                                                                                                                                                                                                                                                                                    |

| 7/Apr/2001        | Damjan Lampret    | First public release                                                                                                                                                                                                                                                                                                                                                                                |

| 22/Apr/2001       | Damjan Lampret    | Incorporated changes from Johan and Matan                                                                                                                                                                                                                                                                                                                                                           |

| 16/May/2001       | Damjan Lampret    | Changed SR, Debug, Exceptions, TT, PM. Added I.cmov, I.ff1, etc.                                                                                                                                                                                                                                                                                                                                    |

| 23/May/2001       | Damjan Lampret    | Added SR[SUMRA], configuration registerc etc.                                                                                                                                                                                                                                                                                                                                                       |

| 24/May/2001       | Damjan Lampret    | Changed virtually almost all chapters in some way – major change is addition of configuration registers.                                                                                                                                                                                                                                                                                            |

| 28/May/2001       | Damjan Lampret    | Changed addresses of some SPRs, removed group SPR group 11, added DCR[CT]=7.                                                                                                                                                                                                                                                                                                                        |

| 24/Jan/2002       | Marko Mlinar      | Major check and update                                                                                                                                                                                                                                                                                                                                                                              |

| 9/Apr/2002        | Marko Mlinar      | PICPR register removed; I.sys convention added; mtspr/mfspr now use bitwise OR instead of sum                                                                                                                                                                                                                                                                                                       |

| 28/July/2002      | Jeanne Wiegelmann | First overall review & layout adjustment                                                                                                                                                                                                                                                                                                                                                            |

| 20/Spetember/2002 | Rohit Mathur      | Second overall review                                                                                                                                                                                                                                                                                                                                                                               |

| 12/January/2003   | Damjan Lampret    | Synchronization with or1ksim and OR1200 RTL. Not all chapters have been checked.                                                                                                                                                                                                                                                                                                                    |

| 26/January/2003   | Damjan Lampret    | Synchronization with or1ksim and OR1200 RTL. From this revision on the manual carries revision number 1.0 and parts of the architecture that are implemented in OR1200 will no longer change because OR1200 is being implemented in silicon. Major parts that are not implemented in OR1200 and could change in the future include ORFPX, ORVDX, PCU, fast context switching, and 64-bit extension. |

Table 1-2. Revision History

#### 1.4 Work in Progress

This document is *work in progress*. Anything in the manual could change until we have made our first silicon. The latest version is always available from OPENCORES CVS. See details about how to get it on <a href="https://www.opencores.org">www.opencores.org</a>.

We are currently looking for people to work on and maintain this document. If you would like to contribute, please send an email to one of the authors.

#### 1.5 Fonts in this Manual

In this manual, fonts are used as follows:

- ✓ Typewriter font is used for programming examples.

- ✓ **Bold** font is used for emphasis.

- ✓ UPPER CASE items may be either acronyms or register mode fields that can be written by software. Some common acronyms appear in the glossary.

- ✓ Square brackets [] indicate an addressed field in a register or a numbered register in a register file.

#### 1.6 Conventions

| 1.mnemonic     | Identifies an ORBIS32/64 instruction.                                                                                                                                                                             |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| lv.mnemonic    | Identifies an ORVDX32/64 instruction.                                                                                                                                                                             |  |

| lf.mnemonic    | Identifies an ORFPX32/64 instruction.                                                                                                                                                                             |  |

| 0x             | Indicates a hexadecimal number.                                                                                                                                                                                   |  |

| RA             | Instruction syntax used to identify a general purpose register                                                                                                                                                    |  |

| REG[FIELD]     | Syntax used to identify specific bit(s) of a general or special purpose register. FIELD can be a name of one bit or a group of bits or a numerical range constructed from two values separated by a color         |  |

| Х              | In certain contexts, this indicates a 'don't care'.                                                                                                                                                               |  |

| N              | In certain contexts, this indicates an undefined numerical value.                                                                                                                                                 |  |

| Implementation | An actual processor implementing the OpenRISC 1000 architecture.                                                                                                                                                  |  |

| Unit           | Sometimes referred to as a coprocessor. An implemented unit usually with some special registers and controlling instructions. It can be defined by the architecture or it may be custom.                          |  |

| Exception      | A vectored transfer of control to supervisor software through an exception vector table. A way in which a processor can request operating system assistance (division by zero, TLB miss, external interrupt etc). |  |

| Privileged     | An instruction (or register) that can only be executed (or accessed) when the processor is in supervisor mode (when SR[SM]=1).                                                                                    |  |

#### Table 1-3. Conventions

#### 1.7 Numbering

All numbers are decimal or hexadecimal unless otherwise indicated. The prefix 0x indicates a hexadecimal number. Decimal numbers don't have a special prefix. Binary and other numbers are marked with their base.

#### 2 Architecture Overview

This chapter introduces the OpenRISC 1000 architecture and describes the general architectural features.

#### 2.1 Features

The OpenRISC 1000 architecture includes the following principal features:

- ✓ A completely free and open architecture.

- ✓ A linear, 32-bit or 64-bit logical address space with implementation-specific physical address space.

- ✓ Simple and uniform-length instruction formats featuring different instruction set extensions:

- > OpenRISC Basic Instruction Set (ORBIS32/64) with 32-bit wide instructions aligned on 32-bit boundaries in memory and operating on 32- and 64-bit data

- > OpenRISC Vector/DSP eXtension (ORVDX64) with 32-bit wide instructions aligned on 32-bit boundaries in memory and operating on 8-, 16-, 32- and 64-bit data

- > OpenRISC Floating-Point eXtension (ORFPX32/64) with 32-bit wide instructions aligned on 32-bit boundaries in memory and operating on 32- and 64-bit data

- ✓ Two simple memory addressing modes, whereby memory address is calculated by:

- > addition of a register operand and a signed 16-bit immediate value

- > addition of a register operand and a signed 16-bit immediate value followed by update of the register operand with the calculated effective address

- ✓ Two register operands (or one register and a constant) for most instructions who then place the result in a third register

- ✓ Shadowed or single 32-entry or narrow 16-entry general purpose register file

- ✓ Branch delay slot for keeping the pipeline as full as possible

- ✓ Support for separate instruction and data caches/MMUs (Harvard architecture) or for unified instruction and data caches/MMUs (Stanford architecture)

- ✓ A flexible architecture definition that allows certain functions to be performed either in hardware or with the assistance of implementation-specific software

- ✓ Number of different, separated exceptions simplifying exception model

- ✓ Fast context switch support in register set, caches, and MMUs

#### 2.2 Introduction

The OpenRISC 1000 architecture is a completely open architecture. It defines the architecture of a family of open source, RISC microprocessor cores. The OpenRISC 1000

architecture allows for a spectrum of chip and system implementations at a variety of price/performance points for a range of applications. It is a 32/64-bit load and store RISC architecture designed with emphasis on performance, simplicity, low power requirements, and scalability. OpenRISC 1000 targets medium and high performance networking and embedded computer environments.

Performance features include a full 32/64-bit architecture; vector, DSP and floating-point instructions; powerful virtual memory support; cache coherency; optional SMP and SMT support, and support for fast context switching. The architecture defines several features for networking and embedded computer environments. Most notable are several instruction extensions, a configurable number of general-purpose registers, configurable cache and TLB sizes, dynamic power management support, and space for user-provided instructions.

The OpenRISC 1000 architecture is the predecessor of a richer and more powerful next generation of OpenRISC architectures.

The full source for implementations of the OpenRISC 1000 architecture is available at <a href="https://www.opencores.org">www.opencores.org</a> and is supported with GNU software development tools and a behavioral simulator. Most OpenRISC implementations are designed to be modular and vendor-independent. They can be interfaced with other open-source cores available at <a href="https://www.opencores.org">www.opencores.org</a>.

Opencores.org encourages third parties to design and market their own implementations of the OpenRISC 1000 architecture and to participate in further development of the architecture.

## 3 Addressing Modes and Operand Conventions

This chapter describes memory-addressing modes and memory operand conventions defined by the OpenRISC 1000 system architecture.

#### 3.1 Memory Addressing Modes

The processor computes an effective address when executing a memory access instruction or branch instruction or when fetching the next sequential instruction. If the sum of the effective address and the operand length exceeds the maximum effective address in logical address space, the memory operand wraps around from the maximum effective address through effective address 0.

#### 3.1.1 Register Indirect with Displacement

Load/store instructions using this address mode contain a signed 16-bit immediate value, which is sign-extended and added to the contents of a general-purpose register specified in the instruction.

Figure 3-1. Register Indirect with Displacement Addressing

Figure 3-1 shows how an effective address is computed when using register indirect with displacement addressing mode.

#### 3.1.2 PC Relative

Branch instructions using this address mode contain a signed 26-bit immediate value that is sign-extended and added to the contents of a Program Counter register. Before the execution at the destination PC, instruction in delay slot is executed.

Figure 3-2. PC Relative Addressing

Figure 3-2 shows how an effective address is generated when using PC relative addressing mode.

#### 3.2 Memory Operand Conventions

The architecture defines an 8-bit byte, 16-bit halfword, a 32-bit word, and a 64-bit doubleword. It also defines IEEE-754 compliant 32-bit single precision float and 64-bit double precision float storage units. 64-bit vectors of bytes, 64-bit vectors of halfwords, 64-bit vectors of singlewords, and 64-bit vectors of single precision floats are also defined.

| Type of Data           | Length in Bytes | Length in Bits |

|------------------------|-----------------|----------------|

| Byte                   | 1               | 8              |

| Halfword (or half)     | 2               | 16             |

| Singleword (or word)   | 4               | 32             |

| Doubleword (or double) | 8               | 64             |

| Single precision float | 4               | 32             |

| Double precision float | 8               | 64             |

| Vector of bytes        | 8               | 64             |

| Vector of halfwords    | 8               | 64             |

| Vector of singlewords  | 8               | 64             |

January 28, 2003

| Type of Data                      | Length in Bytes | Length in Bits |  |

|-----------------------------------|-----------------|----------------|--|

| Vector of single precision floats | 8               | 64             |  |

Table 3-1. Memory Operands and their sizes

#### 3.2.1 Bit and Byte Ordering

Byte ordering defines how the bytes that make up halfwords, singlewords and doublewords are ordered in memory. To simplify OpenRISC implementations, the architecture implements Most Significant Byte (MSB) ordering – or big endian byte ordering by default. But implementations can support Least Significant Byte (LSB) ordering if they implement byte reordering hardware. Reordering is enabled with bit SR[LEE].

The figures below illustrate the conventions for bit and byte numbering within various width storage units. These conventions hold for both integer and floating-point data, where the most significant byte of a floating-point value holds the sign and at least significant byte holds the start of the exponent.

Table 3-2 shows how bits and bytes are ordered in a halfword.

| Bit 15 Bit 8   | Bit 7 Bit 0    |  |

|----------------|----------------|--|

| MSB            | LSB            |  |

| Byte address 0 | Byte address 1 |  |

Table 3-2. Default Bit and Byte Ordering in Halfwords

Table 3-3 shows how bits and bytes are ordered in a singleword.

| Bit 31  | Bit 24   | Bit 23  | Bit 16   | Bit 15  | Bit 8    | Bit 7   | Bit 0   |

|---------|----------|---------|----------|---------|----------|---------|---------|

| M       | SB       |         |          |         |          | LS      | SB .    |

| Byte ac | ldress 0 | Byte ac | ldress 1 | Byte ad | ldress 2 | Byte ad | dress 3 |

Table 3-3. Default Bit and Byte Ordering in Singlewords and Single Precision Floats

Table 3-4 shows how bits and bytes are ordered in a doubleword.

| Bit 63 Bit 56  |                |                |                |

|----------------|----------------|----------------|----------------|

| MSB            |                |                |                |

| Byte address 0 | Byte address 1 | Byte address 2 | Byte address 3 |

|                |                |                | Bit 7   | Bit 0   |

|----------------|----------------|----------------|---------|---------|

|                |                |                | LS      | SB      |

| Byte address 4 | Byte address 5 | Byte address 6 | Byte ad | dress 7 |

Table 3-4. Default Bit and Byte Ordering in Doublewords, Double Precision Floats and all Vector Types

#### 3.2.2 Aligned and Misaligned Accesses

A memory operand is naturally aligned if its address is an integral multiple of the operand length. Implementations might support accessing unaligned memory operands, but the default behavior is that accesses to unaligned operands result in an alignment exception. See chapter Exception Model on page 261 for information on alignment exception.

| Operand                           | Length  | addr[3:0] if aligned |  |

|-----------------------------------|---------|----------------------|--|

| Byte                              | 8 bits  | Xxxx                 |  |

| Halfword (or half)                | 2 bytes | Xxx0                 |  |

| Singleword (or word)              | 4 bytes | Xx00                 |  |

| Doubleword (or double)            | 8 bytes | X000                 |  |

| Single precision float            | 4 bytes | Xx00                 |  |

| Double precision float            | 8 bytes | X000                 |  |

| Vector of bytes                   | 8 bytes | X000                 |  |

| Vector of halfwords               | 8 bytes | X000                 |  |

| Vector of singlewords             | 8 bytes | X000                 |  |

| Vector of single precision floats | 8 bytes | X000                 |  |

**Table 3-5. Memory Operand Alignment**

OR32 instructions are four bytes long and word-aligned.

### 4 Register Set

#### 4.1 Features

The OpenRISC 1000 register set includes the following principal features:

- ✓ Thirty-two or sixteen 32/64-bit general-purpose registers OpenRISC 1000 implementations optimized for use in FPGAs and ASICs in embedded and similar environments may implement only the first sixteen of the possible thirty-two registers.

- ✓ Thirty-two 64-bit vector/floating-point/DSP registers.

- ✓ All other registers are special-purpose registers defined for each unit separately and accessible through the l.mtspr/l.mfspr instructions.

#### 4.2 Overview

An OpenRISC 1000 processor includes several types of registers: user level general-purpose and special-purpose registers, supervisor level special-purpose registers and unit-dependent registers.

User level general-purpose and special-purpose registers are accessible both in user mode and supervisor mode of operation. Supervisor level special-purpose registers are accessible only in supervisor mode of operation (SR[SM]=1).

Unit dependent registers are usually only accessible in supervisor mode but there can be exceptions to this rule. Accessibility for architecture-defined units is defined in this manual. Accessibility for custom units not covered by this manual will be defined in the appropriate implementation-specific manuals.

#### 4.3 Special-Purpose Registers

The special-purpose registers of all units are grouped into thirty-two groups. Each group can have different register address decoding depending on the maximum theoretical number of registers in that particular group. A group can contain registers from several different units or processes. The SR[SM] bit is also used in register address decoding, as some registers are accessible only in supervisor mode. The l.mtspr and l.mfspr instructions are used for reading and writing registers.

| GROUP# | UNIT DESCRIPTION                                                                                            |

|--------|-------------------------------------------------------------------------------------------------------------|

| 0      | System Control and Status registers                                                                         |

| 1      | Data MMU (in the case of a single unified MMU, groups 1 and 2 decode into a single set of registers)        |

| 2      | Instruction MMU (in the case of a single unified MMU, groups 1 and 2 decode into a single set of registers) |

| GROUP# | UNIT DESCRIPTION                                                                                                |

|--------|-----------------------------------------------------------------------------------------------------------------|

| 3      | Data Cache (in the case of a single unified cache, groups 3 and 4 decode into a single set of registers)        |

| 4      | Instruction Cache (in the case of a single unified cache, groups 3 and 4 decode into a single set of registers) |

| 5      | MAC unit                                                                                                        |

| 6      | Debug unit                                                                                                      |

| 7      | Performance counters unit                                                                                       |

| 8      | Power Management                                                                                                |

| 9      | Programmable Interrupt Controller                                                                               |

| 10     | Tick Timer                                                                                                      |

| 11-23  | Reserved for future use                                                                                         |

| 24-31  | Custom units                                                                                                    |

Table 4-1. Groups of SPRs

An OpenRISC 1000 processor implementation is required to implement at least the special purpose registers from group 0. All other groups are optional, and registers from these groups are implemented only if the implementation has the corresponding unit. Which units are actually implemented may be determined by reading the UPR register from group 0.

An SPR address is made of group index (bits 15-11) and register index (bits 10-0).

| Grp # | Reg# | Reg Name | USER<br>MODE | SUPV<br>MODE | Description                                    |

|-------|------|----------|--------------|--------------|------------------------------------------------|

| 0     | 0    | VR       | -            | R            | Version register                               |

| 0     | 1    | UPR      | _            | R            | Unit Present register                          |

| 0     | 2    | CPUCFGR  | -            | R            | CPU Configuration register                     |

| 0     | 3    | DMMUCFGR | -            | R            | Data MMU Configuration register                |

| 0     | 4    | IMMUCFGR | -            | R            | Instruction MMU Configuration register         |

| 0     | 5    | DCCFGR   | _            | R            | Data Cache Configuration register              |

| 0     | 6    | ICCFGR   | _            | R            | Instruction Cache<br>Configuration register    |

| 0     | 7    | DCFGR    | _            | R            | Debug Configuration register                   |

| 0     | 8    | PCCFGR   | _            | R            | Performance Counters<br>Configuration register |

| 0     | 16   | NPC      | _            | R/W          | PC mapped to SPR space (next PC)               |

| 0     | 17   | SR       | _            | R/W          | Supervision register                           |

| Grp # | Reg#          | Reg Name                  | USER<br>MODE | SUPV<br>MODE | Description                                  |

|-------|---------------|---------------------------|--------------|--------------|----------------------------------------------|

| 0     | 18            | PPC                       | 1            | R/W          | PC mapped to SPR space (previous PC)         |

| 0     | 32-47         | EPCR0-EPCR15              | ı            | R/W          | Exception PC registers                       |

| 0     | 48-63         | EEAR0-EEAR15              | ı            | R/W          | Exception EA registers                       |

| 0     | 64-79         | ESR0-ESR15                | ı            | R/W          | Exception SR registers                       |

| 0     | 1024-<br>1535 | GPR0-GPR511               | -            | R/W          | GPRs mapped to SPR space                     |

| 1     | 0             | DMMUCR                    | _            | R/W          | Data MMU Control register                    |

| 1     | 1             | DMMUPR                    | ı            | R/W          | Data MMU Protection Register                 |

| 1     | 2             | DTLBEIR                   | -            | W            | Data TLB Entry Invalidate register           |

| 1     | 4-7           | DATBMR0-<br>DATBMR3       | -            | R/W          | Data ATB Match registers                     |

| 1     | 8-11          | DATBTR0-<br>DATBTR3       | -            | R/W          | Data ATB Translate registers                 |

| 1     | 512-<br>639   | DTLBW0MR0-<br>DTLBW0MR127 | -            | R/W          | Data TLB Match registers<br>Way 0            |

| 1     | 640-<br>767   | DTLBW0TR0-<br>DTLBW0TR127 | _            | R/W          | Data TLB Translate registers<br>Way 0        |

| 1     | 768-<br>895   | DTLBW1MR0-<br>DTLBW1MR127 | _            | R/W          | Data TLB Match registers<br>Way 1            |

| 1     | 896-<br>1023  | DTLBW1TR0-<br>DTLBW1TR127 | _            | R/W          | Data TLB Translate registers<br>Way 1        |

| 1     | 1024-<br>1151 | DTLBW2MR0-<br>DTLBW2MR127 | _            | R/W          | Data TLB Match registers<br>Way 2            |

| 1     | 1152-<br>1279 | DTLBW2TR0-<br>DTLBW2TR127 | _            | R/W          | Data TLB Translate registers<br>Way 2        |

| 1     | 1280-<br>1407 | DTLBW3MR0-<br>DTLBW3MR127 | -            | R/W          | Data TLB Match registers<br>Way 3            |

| 1     | 1408-<br>1535 | DTLBW3TR0-<br>DTLBW3TR127 | _            | R/W          | Data TLB Translate registers<br>Way 3        |

| 2     | 0             | IMMUCR                    | _            | R/W          | Instruction MMU Control register             |

| 2     | 1             | IMMUPR                    | -            | R/W          | Instruction MMU Protection Register          |

| 2     | 2             | ITLBEIR                   | _            | W            | Instruction TLB Entry<br>Invalidate register |

| 2     | 4-7           | IATBMR0-<br>IATBMR3       | _            | R/W          | Instruction ATB Match registers              |

| 2     | 8-11          | IATBTR0-<br>IATBTR3       | _            | R/W          | Instruction ATB Translate registers          |

| 2     | 512-          | ITLBW0MR0-                | _            | R/W          | Instruction TLB Match                        |

| Grp # | Reg#          | Reg Name                  | USER<br>MODE | SUPV<br>MODE | Description                               |

|-------|---------------|---------------------------|--------------|--------------|-------------------------------------------|

|       | 639           | ITLBW0MR127               |              |              | registers Way 0                           |

| 2     | 640-<br>767   | ITLBW0TR0-<br>ITLBW0TR127 | 1            | R/W          | Instruction TLB Translate registers Way 0 |

| 2     | 768-<br>895   | ITLBW1MR0-<br>ITLBW1MR127 | I            | R/W          | Instruction TLB Match registers Way 1     |

| 2     | 896-<br>1023  | ITLBW1TR0-<br>ITLBW1TR127 | _            | R/W          | Instruction TLB Translate registers Way 1 |

| 2     | 1024-<br>1151 | ITLBW2MR0-<br>ITLBW2MR127 | _            | R/W          | Instruction TLB Match registers Way 2     |

| 2     | 1152-<br>1279 | ITLBW2TR0-<br>ITLBW2TR127 | -            | R/W          | Instruction TLB Translate registers Way 2 |

| 2     | 1280-<br>1407 | ITLBW3MR0-<br>ITLBW3MR127 | _            | R/W          | Instruction TLB Match registers Way 3     |

| 2     | 1408-<br>1535 | ITLBW3TR0-<br>ITLBW3TR127 | 1            | R/W          | Instruction TLB Translate registers Way 3 |

| 3     | 0             | DCCR                      | 1            | R/W          | DC Control register                       |

| 3     | 1             | DCBPR                     | W            | W            | DC Block Prefetch register                |

| 3     | 2             | DCBFR                     | W            | W            | DC Block Flush register                   |

| 3     | 3             | DCBIR                     | -            | W            | DC Block Invalidate register              |

| 3     | 4             | DCBWR                     | W            | W            | DC Block Write-back register              |

| 3     | 5             | DCBLR                     | W            | W            | DC Block Lock register                    |

| 4     | 0             | ICCR                      | -            | R/W          | IC Control register                       |

| 4     | 1             | ICBPR                     | W            | W            | IC Block Prefetch register                |

| 4     | 2             | ICBIR                     | _            | W            | IC Block Invalidate register              |

| 4     | 3             | ICBLR                     | W            | W            | IC Block Lock register                    |

| 5     | 1             | MACLO                     | R/W          | R/W          | MAC Low                                   |

| 5     | 2             | MACHI                     | R/W          | R/W          | MAC High                                  |

| 6     | 0-7           | DVR0-DVR7                 | _            | R/W          | Debug Value registers                     |

| 6     | 8-15          | DCR0-DCR7                 | _            | R/W          | Debug Control registers                   |

| 6     | 16            | DMR1                      | _            | R/W          | Debug Mode register 1                     |

| 6     | 17            | DMR2                      | _            | R/W          | Debug Mode register 2                     |

| 6     | 18-19         | DCWR0-DCWR1               | _            | R/W          | Debug Watchpoint Counter registers        |

| 6     | 20            | DSR                       | _            | R/W          | Debug Stop register                       |

| 6     | 21            | DRR                       | _            | R/W          | Debug Reason register                     |

| 7     | 0-7           | PCCR0-PCCR7               | R*           | R/W          | Performance Counters Count registers      |

| 7     | 8-15          | PCMR0-PCMR7               | _            | R/W          | Performance Counters Mode registers       |

| 8     | 0             | PMR                       | _            | R/W          | Power Management register                 |

| Grp# | Reg# | Reg Name | USER<br>MODE | SUPV<br>MODE | Description               |

|------|------|----------|--------------|--------------|---------------------------|

| 9    | 0    | PICMR    | _            | R/W          | PIC Mask register         |

| 9    | 2    | PICSR    | _            | R/W          | PIC Status register       |

| 10   | 0    | TTMR     | _            | R/W          | Tick Timer Mode register  |

| 10   | 1    | TTCR     | R*           | R/W          | Tick Timer Count register |

Table 4-2. List of All Special-Purpose Registers

#### 4.4 General-Purpose Registers (GPRs)

The thirty-two general-purpose registers are labeled R0-R31 and are 32 bits wide in 32-bit implementations and 64 bits wide in 64-bit implementations. They hold scalar integer data, floting-point data, vectors or memory pointers. Table 4-3 contains a list of general-purpose registers. The GPRs may be accessed as both source and destination registers by ORBIS, ORVDX and ORFPX instructions.

See chapter Application Binary Interface on page 333 for information on floating-point data types.

| Register |     |     |     |     | r31 | r30 |

|----------|-----|-----|-----|-----|-----|-----|

| Register | R29 | R28 | r27 | r26 | r25 | r24 |

| Register | R23 | R22 | r21 | r20 | r19 | r18 |

| Register | R17 | R16 | r15 | r14 | r13 | r12 |

| Register | R11 | r10 | r9  | r8  | r7  | r6  |

| Register | R5  | r4  | r3  | r2  | r1  | r0  |

Table 4-3. General-Purpose Registers

R0 is used as a constant zero. Whether or not R0 is actually hardwired to zero is implementation dependent. **R0 should never be used as a destination register**. Functions of other registers are explained in chapter Application Binary Interfaceon page 333.

An implementation may have several sets of GPRs and use them as shadow registers, switching between them whenever a new exception occurs. The current set is identified by the SR[CID] value.

An implementation is not required to initialize GPRs to zero during the reset procedure. The reset exception handler is responsible for initializing GPRs to zero if that is necessary.

#### 4.5 Support for Custom Number of GPRs

Programs may be compiled with less than thirty-two registers. Unused registers are disabled (set as *fixed* registers) when compiling code. Such code is also executable on normal implementations with thirty-two registers but not vice versa. This feature is quite useful since users are expected to move from less powerful OpenRISC implementations with less than thirty-two registers to more powerful thirty-two register OpenRISC implementations.

If configuration registers are implemented, CPUCFGR[CGF] indicates whether implementation has complete thirty-two general-purpose registers or less than thirty-two registers.

#### 4.6 Supervision Register (SR)

The Supervison register is a 32-bit special-purpose supervisor-level register accessible with the l.mtspr/l.mfspr instructions in supervisor mode only.

The SR value defines the state of the processor.

| Bit        | 31-28 | 27-17     | 16    |

|------------|-------|-----------|-------|

| Identifier | CID   | Reserved  | SUMRA |

| Reset      | 0     | 0         | 0     |

| R/W        | R/W   | Read Only | R/W   |

| Bit        | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Identifier | FO  | EPH | DSX | OVE | OV  | CY  | F   | CE  |

| Reset      | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Bit        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Identifier | LEE | IME | DME | ICE | DCE | IEE | TEE | SM  |

| Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| SM  | Supervisor Mode                            |

|-----|--------------------------------------------|

|     | 0 Processor is in User Mode                |

|     | 1 Processor is in Supervisor Mode          |

| TEE | Tick Timer Exception Enabled               |

|     | 0 Tick Timer Exceptions are not recognized |

|     | 1 Tick Timer Exceptions are recognized     |

| IEE | Interrupt Exception Enabled                |

|        | 0 Interrupts are not recognized                                       |

|--------|-----------------------------------------------------------------------|

|        | 1 Interrupts are recognized                                           |

| DOE    |                                                                       |

| DCE    | Data Cache Enable                                                     |

|        | 0 Data Cache is not enabled 1 Data Cache is enabled                   |

| 105    |                                                                       |

| ICE    | Instruction Cache Enable                                              |

|        | 0 Instruction Cache is not enabled                                    |

|        | 1 Instruction Cache is enabled                                        |

| DME    | Data MMU Enable                                                       |

|        | 0 Data MMU is not enabled                                             |

|        | 1 Data MMU is enabled                                                 |

| IME    | Instruction MMU Enable                                                |

|        | 0 Instruction MMU is not enabled                                      |

|        | 1 Instruction MMU is enabled                                          |

| LEE    | Little Endian Enable                                                  |

|        | 0 Little Endian (LSB) byte ordering is not enabled                    |

|        | 1 Little Endian (LSB) byte ordering is enabled                        |

| CE     | CID Enable                                                            |

|        | CID disabled and shadow registers disabled                            |

|        | 1 CID automatic increment and shadow registers enabled                |

| F      | Flag                                                                  |

|        | Conditional branch flag was cleared by sfXX instructions              |

|        | 1 Conditional branch flag was set by sfXX instructions                |

| CY     | Carry flag                                                            |

|        | 0 No carry out produced by last arithmetic operation                  |

|        | 1 Carry out was produced by last arithmetic operation                 |

| OV     | Overflow flag                                                         |

|        | No overflow occured during last arithmetic operation                  |

|        | 1 Overflow occured during last arithmetic operation                   |

| OVE    | Overflow flag Exception                                               |

|        | 0 Overflow flag does not cause an exception                           |

|        | 1 Overflow flag causes range exception                                |

| DSX    | Delay Slot Exception                                                  |

|        | 0 EPCR points to instruction not in the delay slot                    |

|        | 1 EPCR points to instruction in delay slot                            |

| EPH    | Exception Prefix High                                                 |

|        | 0 Exceptions vectors are located in memory area starting at 0x0       |

|        | 1 Exception vectors are located in memory area starting at 0xF0000000 |

| FO     | Fixed One                                                             |

|        | This bit is always set                                                |

| SUMRA  | SPRs User Mode Read Access                                            |

| GOWINA | 0 All SPRs are inaccessible in user mode                              |

|        | 1 Certain SPRs can be read in user mode                               |

| CID    | Context ID (optional)                                                 |

| CID    | Context in (obtional)                                                 |

|  | 0-15 Current Processor Context |

|--|--------------------------------|

|--|--------------------------------|

Table 4-4. SR Field Descriptions

## 4.7 Exception Program Counter Registers (EPCR0 - EPCR15)

The Exception Program Counter registers are special-purpose supervisor-level registers accessible with the l.mtspr/l.mfspr instructions in supervisor mode. Read access in user mode is possible if it is enabled in PCMRx[SUMRA]. They are 32-bit wide registers in 32-bit implementations and can be wider than 32 bits in 64-bit implementations.

After an exception, the EPCR is set to the program counter address (PC) of the instruction that was interrupted by the exception. If only one EPCR is present in the implementation, it must be saved by the exception handler routine before exception recognition is re-enabled in the SR.

| Bit        | 31-0 |

|------------|------|

| Identifier | EPC  |

| Reset      | 0    |

| R/W        | R/W  |

| EPC | Exception Program Counter Address |

|-----|-----------------------------------|

|-----|-----------------------------------|

Table 4-5. EPCR Field Descriptions

## 4.8 Exception Effective Address Registers (EEAR0-EEAR15)

The Exception Effective Address registers are special-purpose supervisor-level registers accessible with the l.mtspr/l.mfspr instructions in supervisor mode. Read access in user mode is possible if it is enabled in SR[SUMRA]. The EEARs are 32-bit wide registers in 32-bit implementations and can be wider than 32 bits in 64-bit implementations.

After an exception, the EEAR is set to the effective address (EA) generated by the faulting instruction. If only one EEAR is present in the implementation, it must be saved by the exception handler routine before exception recognition is re-enabled in the SR.

| Bit        | 31-0 |

|------------|------|

| Identifier | EEA  |

| Reset      | 0    |

| R/W | R/W                         |

|-----|-----------------------------|

|     |                             |

| EEA | Exception Effective Address |

Table 4-6. EEAR Field Descriptions

## 4.9 Exception Supervision Registers (ESR0-ESR15)

The Exception Supervision registers are special-purpose supervisor-level registers accessible with l.mtspr/l.mfspr instructions in supervisor mode. They are 32 bits wide registers in 32-bit implementations and can be wider than 32 bits in 64-bit implementations.

After an exception, the Supervision register (SR) is copied into the ESR. If only one ESR is present in the implementation, it must be saved by the exception handler routine before exception recognition is re-enabled in the SR.

| Bit        | 31-0 |

|------------|------|

| Identifier | ESR  |

| Reset      | 0    |

| R/W        | R/W  |

| EEA | Exception SR |

|-----|--------------|

Table 4-7. ESR Field Descriptions

## 4.10 Next and Previous Program Counter (NPC and PPC)

The Program Counter registers represent the address just executed and the address instruction just to be executed.

These and the GPR registers mapped into SPR space should only be used for debugging purposes by an external debugger. Applications should use the l.jal instruction to obtain the current program counter and arithmethic instructions to obtain GPR register values.

#### 5 Instruction Set

This chapter describes the OpenRISC 1000 instruction set.

#### 5.1 Features

The OpenRISC 1000 instruction set includes the following principal features:

- ✓ Simple and uniform-length instruction formats featuring five Instruction Subsets

- ✓ OpenRISC Basic Instruction Set (ORBIS32/64) with 32-bit wide instructions aligned on 32-bit boundaries in memory and operating on 32-bit and 64-bit data

- ✓ OpenRISC Vector/DSP eXtension (ORVDX64) with 32-bit wide instructions aligned on 32-bit boundaries in memory and operating on 8-, 16-, 32- and 64-bit data

- ✓ OpenRISC Floating-Point eXtension (ORFPX32/64) with 32-bit wide instructions aligned on 32-bit boundaries in memory and operating on 32-bit and 64-bit data

- ✓ Reserved opcodes for custom instructions

Note: Instructions are divided into instruction classes. Only the basic classes are required to be implemented in an OpenRISC 1000 implementation.

Figure 5-1. Instruction Set

#### 5.2 Overview

OpenRISC 1000 instructions belong to one of the following instruction subsets:

- ✓ ORBIS32:

- > 32-bit integer instructions

- Basic DSP instructions

- > 32-bit load and store instructions

- > Program flow instructions

- > Special instructions

- ✓ ORBIS64:

- > 64-bit integer instructions

- > 64-bit load and store instructions

- ✓ ORFPX32:

- > Single-precision floating-point instructions

- ✓ ORFPX64:

- > Double-precision floating-point instructions

- > 64-bit load and store instructions

- ✓ ORVDX64:

- > Vector instructions

- > DSP instructions

Instructions in each subset are also split into two instruction classes according to implementation importance:

- ✓ Class I

- ✓ Class II

| Class                                                 | Description                                                                                                                                                               |  |  |  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| I Instructions in class I must always be implemented. |                                                                                                                                                                           |  |  |  |

| II                                                    | Instructions from class II are optional and an implementation may choose to use some or all instructions from this class based on requirements of the target application. |  |  |  |