## Written examination TSTE87 2015-06-03

1. (a) Why is the latency of a bit-serial (LSB first) multiplier at least equal to the number of fractional bits?

Solution:

(b) Why are only the loops included when determining the minimal sample period? (And, e.g., not the critical path?)

Solution: Non-recursive parts can be pipelined/retimed.

(c) How is the throughput (number of operations per time unit) related to the execution time?

Solution:

$$\Gamma hroughput = \frac{1}{T_{ext}}$$

(d) What is a redundant number representation? Give one example.

**Solution:** In a redundant number representation there is more than one representation of each number.

(e) How are the iteration period bound,  $T_{\infty}$ , minimal sample period,  $T_{\min}$ , number of operations and number of delay elements respectively affected by unfolding an algorithm a factor N?

## Solution:

- $\bullet$  Iteration period bound: increases a factor N

- Minimal sample period: unchanged

- Number of operations: increases a factor N

- Number of delays elements: unchanged

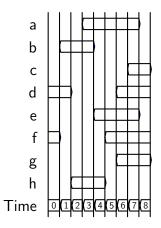

- 2. Consider the memory variable life time diagram in Fig. 1, consisting of variables a to h. This should be realized using single port memories, i.e., memories where a single variable can be either read or written in each time slot.

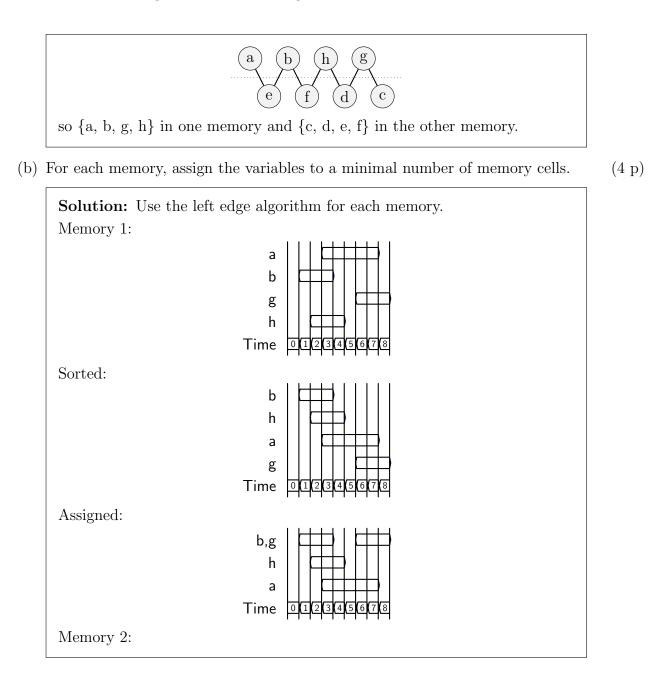

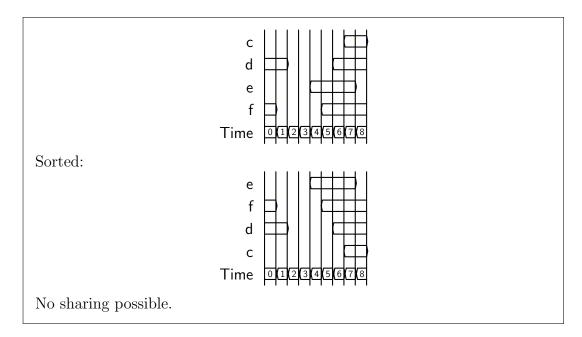

- (a) Divide the variables between a minimal number of memories.

(4 p)

Solution: Exclusion graph based on memory read/writes

(2 p)

(2 p)

(2 p)

(2 p)

Figure 1: Life time diagram for Problem 2.

3. The following expression shall be realized using shifts, additions and subtractions. Draw a realization using as few additions and subtractions as possible.

$$y = 13x_1 - 5x_2 + 25x_3$$

Note that  $25 = 5 \times 5 = 13 \times 2 - 1$ .

Solution:

$$y = 13x_1 - 5x_2 + 25x_3 = 8x_1 + 5(x_1 - x_2 + 5x_3) = 8(x_1 + 2x_3) + 5((x_1 + 2x_3) - x_2) - x_3$$

so five additions/subtractions are required.

4. The expression in Problem 3 is now to be implemented using distributed arithmetic. Determine the ROM contents in a named and stated binary representation.

Solution: Two's complement representation Value ROM content  $x_3$  $x_1$  $x_2$ -5

(4 p)

(4 p)

- 5. Consider the realization of a complex-valued 40-tap (39:th-order) FIR filter in an FPGA. The FPGA can be clocked at a maximum of 500 MHz and the input sample rate is 2.5 GSa/s. For simplicity, assume that each complex multiplier requires four multipliers and that no coefficient symmetry can be used.

- (a) From the following list of FPGAs, which one (a, b, c, or d) would be the most suitable for a direct implementation of the FIR filter, i.e., the design fits but the FPGA is not overly large? Each DSP block contains one multiplier.

| a<br>b      | XC6VLX75T<br>XC6VLX130T                | 288                                                  |                                                                                                                             |

|-------------|----------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| b           | XC6VLX130T                             | 100                                                  |                                                                                                                             |

|             | 11COV LITIOO1                          | 480                                                  |                                                                                                                             |

| с           | XC6VLX195T                             | 640                                                  |                                                                                                                             |

| d           | XC6VSX315T                             | 1344                                                 |                                                                                                                             |

|             |                                        |                                                      |                                                                                                                             |

| $40 \times$ | $\frac{4 \times 2.5 \times 10^9}{2} =$ | 800 multipliers                                      |                                                                                                                             |

|             | $\frac{d}{40 \times }$                 | d XC6VSX315T<br>$40 \times 4 \times 2.5 \times 10^9$ | d XC6VSX315T 1344 $\frac{40 \times 4 \times 2.5 \times 10^9}{40 \times 4 \times 2.5 \times 10^9} = 800 \text{ multipliers}$ |

$$500 imes 10^6$$

- so FPGA d must be selected.

- (b) Now, consider the implementation of the FIR filtering in the frequency domain, i.e., using a DFT/FFT. For an N-point DFT, in this case, N 40 + 1 samples can be processed per iteration (samples + impulse response length 1 = DFT length). Each iteration require the computation of an N-point DFT, N complex multiplications and an N-point IDFT (identical complexity to DFT). The computation of an N-point FFT (with  $N = 2^M$ ) require  $\frac{N}{2} (\log_2 N 1) = \frac{N}{2} (M 1)$  complex multiplications. Assuming a "perfect" resource utilization, i.e., no worrying about scheduling the algorithms etc, which is the most suitable FPGA? Hint: the optimal complexity (in multiplications per sample processed) is found for about four times more samples than impulse response length for each iteration.

Solution: Each DFT-mult-IDFT iteration require

$$\left(\frac{N}{2}\left(\log_2 N - 1\right) + N + \frac{N}{2}\left(\log_2 N - 1\right)\right) = N\log_2 N \text{ complex multiplication}$$

and will process N-39 samples. Hence, the number of complex multiplications per sample is

$$\frac{N\log_2 N}{N-39}$$

Complex multiplications per sample, N = 64

$$\frac{64 \times 6}{25} = 15.36\tag{2}$$

Complex multiplications per sample, N = 128

$$\frac{128 \times 7}{89} \approx 10.07\tag{3}$$

(4 p)

(1)

Complex multiplications per sample, N = 256

$$\frac{256 \times 8}{217} \approx 9.44\tag{4}$$

Complex multiplications per sample, N = 512

$$\frac{512 \times 9}{473} \approx 9.74$$

(5)

Best result for N = 256. Number of multipliers needed:

$$\frac{9.44 \times 4 \times 2.5 \times 10^9}{500 \times 10^6} \approx 189\tag{6}$$

so FPGA a can be used instead.

(c) Assuming that you utilize all multipliers in the selected FPGAs for (a) and (b), what are the respective resulting clock frequencies required?

**Solution:** For (a) FPGA d is selected which have 1344 DSP blocks compared to the 800 needed. Hence, the new clock frequency is  $500 \times \frac{800}{1344} \approx 298$  MHz. For (b) FPGA a is selected which have 288 DSP blocks compared to the 189 needed. Hence, the new clock frequency is  $500 \times \frac{189}{288} \approx 328$  MHz.

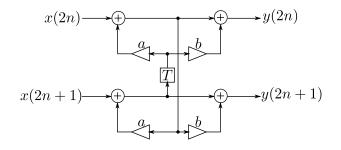

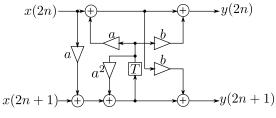

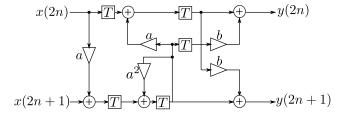

6. Consider the unfolded first-order filter in Fig. 2.

Figure 2: Unfolded first-order filter.

(a) Determine the minimal sample period,  $T_{\min}$ , for the algorithm.

Solution:

$$T_{\min} = \frac{T_{\infty}}{2} = \frac{\frac{2T_{L,mult} + 2T_{L,add}}{1}}{2} = \frac{2T_{L,mult} + 2T_{L,add}}{2} = T_{L,mult} + T_{L,add}$$

(b) Apply algorithm transformations and/or pipelining/retiming to obtain  $T_{cp} = T_{\infty} = T_{L,mult} + T_{L,add}$ , i.e., there should be at most one multiplier and one adder

(2 p)

in the critical path and critical loop, respectively. Ignore finite word length effects.

## Solution:

$$\begin{cases} y(2n) &= x(2n) + (a+b)v(n) \\ y(2n+1) &= (a+b)x(2n) + x(2n+1) + a(a+b)v(n) \\ v(n+1) &= ax(2n) + x(2+1) + aav(n) \end{cases}$$

Focus on the loop, merge the two multiplications by  $\boldsymbol{a}$  and reorder the additions:

Pipeline and retime:

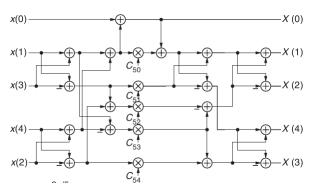

7. In Fig. 3, the block diagram of a 5-point DFT based on Winograd short-DFT algorithm is shown. This should be implemented using a time-multiplexed sharedmemory architecture with homogeneous non-preemptive processing elements. There are two types of processing elements: multipliers and adders (which can also perform subtractions). All signals are complex-valued, however, the processing elements are also complex-valued. The latency of a multiplier is two clock cycles and the latency of an adder is one clock cycle. Both types of processing elements have an execution time of one clock cycle. The implementation should be operated in a cyclic manner, i.e., you can pipeline the block diagram arbitrarily. In one scheduling period, the inputs should arrive one per time units in order  $x(0), x(1), \ldots$  and outputs exit one per time unit in order  $X(0), X(1), \ldots$ , note that this can be readily obtained using shimming delays.

Figure 3: 5-point Winograd DFT.

(a) Determine the critical path,  $T_{cp}$ .

$T_{cp} = T_{L,mult} + 5T_{L,add} = 7$  clock cycles

- (b) Determine the precedence graph.

- (c) Determine the minimum scheduling period assuming that one multiplier PE is used. (Ignore the additions for now.)

Solution:

$$N_{\rm PE} = \frac{\sum T_{\rm exe}}{T_{\rm schedule}} \Rightarrow T_{\rm schedule} = \frac{\sum T_{\rm exe}}{N_{\rm PE}} = \frac{5 \times 1}{1} = 5 \text{ time units}$$

(7)

(d) Based on the scheduling period from (a) determine the minimum amount of adder PEs.

## Solution:

$$N_{\rm PE} = \frac{\sum T_{\rm exe}}{T_{\rm schedule}} = \frac{17 \times 1}{5} = 3.4 \text{ adder PEs} \Rightarrow 4 \text{ adder PEs}$$

(8)

(2 p)

(6 p)

(2 p)

- (e) Schedule the algorithm using one multiplier, a minimum amount of adder PEs and the minimum scheduling period. It is OK to drop the signs from the sub-tractions.

- (f) What is the latency of the resulting schedule (from input x(i) to output X(i))? Compare to the critical path,  $T_{cp}$ .

- (g) A direct computation of the DFT requires multiplying the input vector by a  $5 \times 5$  complex-valued DFT matrix. What are the savings in additions/subtractions and multiplications, respectively, using the Winograd 5-point DFT compared to a direct computation? Note that for the first row and the first column of the DFT matrix, the coefficients are 1, so those multiplications should be ignored.

| Solution:          |                        |                           |

|--------------------|------------------------|---------------------------|

|                    | Additions/subtractions | Multiplications           |

| Direct computation | $5 \times (5-1) = 20$  | $(5-1) \times (5-1) = 16$ |

| Winograd           | 17                     | 5                         |

| Savings            | 3                      | 11                        |

| Relative savings   | 15%                    | 68.75%                    |

(8 p)

(2 p)