# **Exam TEN1 in TSTE85 Low Power Electronics**

| Time:                       | Friday 11 January 2019, 8:00–12:00                    |

|-----------------------------|-------------------------------------------------------|

| Place:                      | G34                                                   |

| <b>Responsible teacher:</b> | Mark Vesterbacka, phone 013-281324                    |

| Allowed aids:               | Calculator and appended formula page                  |

| Maximum score:              | 70 points                                             |

| Grades:                     | 50 points for 5<br>40 points for 4<br>30 points for 3 |

| Solutions:                  | Posted on the course web                              |

| Results:                    | Posted through LADOK by Tuesday 29 January 2019       |

- 1.

- a) Give examples on historical applications that have been driving forces in the field of low power electronics. (3 p)

- b) Describe how the following software strategies can be used to obtain a low power system: *transition strategies*, *load-change strategies*, *adaptation strategies*. (3 p)

- c) Describe the impact of average and peak power consumption on a chip design. (2 p)

- d) Why is it more power efficient to use an on-chip inductor compared with an external inductor? (2 p)

- e) Explain how precomputation of a logic function can be used to reduce the power consumption. (2 p)

- 2. Explain what a static leakage current in a CMOS circuit is and give two examples of how static leakage currents can be reduced. (4 p)

- 3. In Figure 1 a static CMOS inverter is driving an identical inverter and an interconnect. The interconnect is assumed to be short in length and is modeled as a lumped capacitor. The parasitic capacitances in the two inverters are dominated by the transistor capacitances. The input capacitance of the inverter is  $C_{in}$ , the output capacitance is  $C_{out}$ , and the interconnect capacitance is  $C_w$ . The power supply voltage is  $V_{DD} = 1.2$  V and the threshold voltage for the transistors is  $|V_T| = 0.4$  V. Assume  $C_{in} = C_{out} = C_0$ ,  $C_w = 4C_0$ . Neglect channel length modulation in calculation of MOSFET currents ( $\lambda \approx 0$ ).

Figure 1. Inverter loaded with interconnect and an identical inverter.

- a) Estimate the relative change in dynamic power consumption when the transistor widths are increased to double the original size, and voltage scaling is used to maintain the total propagation delay from the input of the first inverter to the input of the second inverter. Assume long transistor channels with saturated MOSFETs during charge. (5 p)

- b) Estimate the relative change in dynamic power consumption when the transistor widths are increased to double the original size, and voltage scaling is used to maintain the total propagation delay from the input of the first inverter to the input of the second inverter. Assume short transistor channels with r = 1.5 during charge. (5 p)

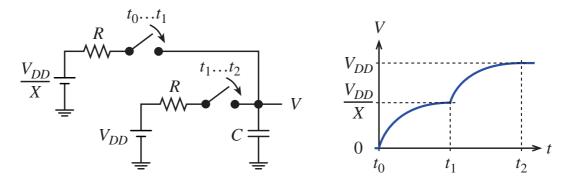

4. The capacitor *C* is charged in sequence by two power supplies as shown in Figure 2. At time  $t_0$  the first power supply with supply voltage  $V_{DD}/X$  is connected. When the voltage *V* over *C* has settled at time  $t_1$ , the first power supply is disconnected and the second power supply with supply voltage  $V_{DD}$  is connected to *C*. The voltage *V* has finally settled at time  $t_2$ .

Figure 2. Stepwise charging of a capacitor.

- a) How much energy is stored in the capacitor *C* at time  $t_1$ ? (2 p)

- b) How much energy is stored in the capacitor *C* at time  $t_2$ ? (2 p)

- c) How much energy has been drawn from the power supplies between time  $t_0$  and  $t_2$  due to the charging of *C*? (4 p)

- d) How should the value of X be chosen to minimize the energy drawn from the power supplies as derived in c)?

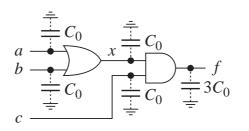

- 5. A logic circuit is shown in Figure 3. Determine the dynamic power consumption due to charging and discharging of the indicated capacitors in circuit nodes *a*, *b*, *c*, *x*, and *F*, where the unit capacitance  $C_0 = 5.0$  fF. Assume static CMOS logic with a power supply voltage  $V_{DD} = 1.2$  V and clock frequency f = 1 GHz. The input signals are glitch free, uncorrelated, and random with one's probabilities P(a=1) = 0.1, P(b=1) = 0.2, and P(c=1) = 0.3.

Figure 3. Logic circuit.

- a) Solve the problem assuming a zero-delay model. (6 p)

- b) Solve the problem assuming a unit-delay model. (6 p)

- 6. Consider an ideal analog integrator circuit where all current taken from the supply is used to charge the integrating capacitor at the output. The supply voltage is  $V_{DD}$  and the output capacitance is *C*. A sinusoidal signal with frequency *f* and voltage swing  $V_{pp} < V_{DD}$  is output. Assume the signal-to-noise ratio to be determined by the thermal noise according to  $SNR = 10 \log(CV_{pp}^2) 10 \log(8kT)$ , where *k* is Boltzmann's constant and *T* is the absolute temperature.

- a) Derive an expression for the dissipated power. (2 p)

- b) Show that the power dissipation for the circuit is determined by the requirements on SNR, operating frequency, and temperature. (5 p)

- 7. Four numbers should be added with three two-input adders. The numbers are input from registers.

- a) What structure of connecting the adders is preferred from a low power point of view? Motivate your answer.

(3 p)

- b) How can the power consumption be reduced using pipelining? What are the effects on the implementation? (4 p)

- c) How can the power consumption be reduced using interleaving? What are the effects on the implementation? (4 p)

- d) How is the power consumption affected if both pipelining and interleaving are applied to the circuit?

(2 p)

## **TSTE85 FORMULAS**

### Circuits

| Transition activity             | $\alpha = \alpha_{01} + \alpha_{10} = 2\alpha_{01} = 2\alpha_{10}$          |

|---------------------------------|-----------------------------------------------------------------------------|

| Switch activity                 | $a = \sum_{i} \alpha_{01,i} C_i / \sum_{i} C_i$                             |

| Switched capacitance            | $C_{sw} = a \sum_{i} C_{i}$                                                 |

| Dynamic power consumption       | $P_d = f_{clk} C_{sw} V_{pp} V_{DD}$                                        |

| Short-circuit power consumption | $P_{sc} = a f_{clk} t_{sc} I_{peak} V_{DD}$                                 |

| Propagation time                | $t_{p} \propto V_{DD} / \left( V_{DD} - V_{T} \right)^{r}, 1 \leq r \leq 2$ |

#### **MOSFETs**

| Threshold voltage                   | $V_{T} = V_{T0} + \gamma \left( \sqrt{\left  V_{SB} - 2\Phi_{F} \right } - \sqrt{\left  2\Phi_{F} \right } \right)$                                                                                                    |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Weak inversion ( $V_{GT} < 0$ )     | $I_{D} = I_{D0} (W/L) e^{- V_{GT} /(n_{s}V_{\Theta})} (1 + \lambda V_{DS})$<br>where<br>$V_{\Theta} \approx 26 \text{ mV } @ T = 300 \text{ K}$<br>$n_{s} \text{ can be calculated from } S = n_{s}V_{\Theta} \ln(10)$ |

| Strong inversion ( $V_{GT} \ge 0$ ) | $I_{D} = k' (W/L) V_{min} ( V_{GT}  - V_{min}/2) (1 + \lambda V_{DS})$<br>where<br>$V_{min} = \min( V_{GT} ,  V_{DS} ,  V_{DSAT} )  \text{(corresponding to saturation, resistive, and velocity saturation modes)}$    |

| Gate-oxide leakage                  | $I_{G} = k_{1} W \left( V_{ox} / t_{ox} \right)^{2} e^{-k_{2} t_{ox} / V_{ox}}$                                                                                                                                        |

### Logic

$\overline{f\left(x, y, z, \dots, +, \cdot\right)} = f\left(\overline{x}, \overline{y}, \overline{z}, \dots, \cdot, +\right)$   $f_{\overline{x}} = f\left(x, y, z, \dots\right)\Big|_{x=0}, f_{\overline{x}} = f\left(x, y, z, \dots\right)\Big|_{x=1}$   $f\left(x, y, z, \dots\right) = \overline{x} \cdot f_{\overline{x}} + x \cdot f_{\overline{x}} = \left(x + f_{\overline{x}}\right)\left(\overline{x} + f_{\overline{x}}\right)$   $ODC_{x} = f_{\overline{x}}f_{x} + \overline{f_{\overline{x}}}\overline{f_{x}}$

Cofactors

Expansion in sum and product

Shannon's expansion theorem

Observability Don't Care set