Kent Palmkvist

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07

2

# Agenda

- $\bullet \ Microprogrammed \ control \ structures$

- Microprogramming

2024-10-07

#### **Practical issues**

- Handin part 2 deadline today (monday 7/10 at 23:30)

- Individual work!

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07

1

#### Lab 3

- Deadline one week after project completion

- Uses an existing design, only add microcode definition

- Ones and zeros in a memory  $\,$

- Results always checked by me

- Send email and ask for me to check (or go to my office and ask)

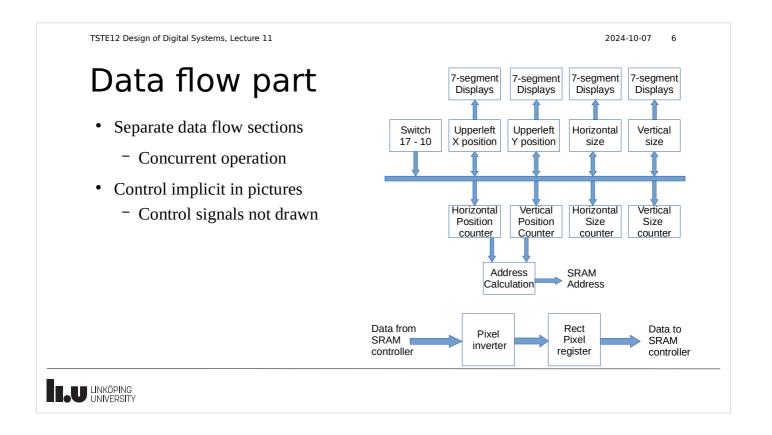

TSTE12 Design of Digital Systems, Lecture 11 2024-10-07 Larger system description • Lab 3 system VGA VGA - Image stored in SRAM Screen Control - Enter rectangle coordinates from switches - Invert color in the image SRAM **SRAM** Control · Mixed control and data flow -segment Switches Rectangle Display, **Pushbuttons** Generator LEDs **FPGA** LINKÖPING UNIVERSITY

2024-10-07

#### 7

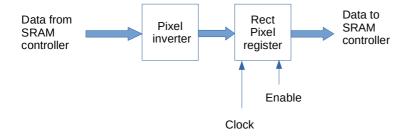

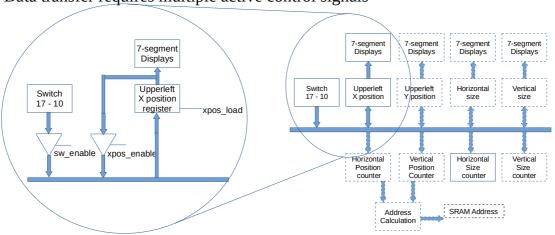

# Control signal details

- There are more details hidden in the data flow description

- Implicit clock, enable and other control signals

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07

Ω

# Multiple control signals necessary

Data transfer requires multiple active control signals

2024-10-07

### Large number of control signals

#### Bit position Function

- StoreRectData Store the inverted value of the latest data read from SRAM

- ReadSW17\_10 Read the settings of the switch 17 downto 10

- Rect-RD Start a read from the SRAM

- Rect-WR Start a write of the Rectangle data register into SRAM

- NextHorPos Increment horizontal position counter

- NextVertPos Increment vertical position counter

- DecHorCnt Decrement horizontal counter

- DecVertCnt Decrement vertical counter

- SetHorPos Set the value of the horizontal position counter

- SetVertPos Set the value of the vertical position counter

- SetHorCnt Set the value of the horizontal counter

- SetVertCnt Set the value of the vertical counter

- LoadUpperLeftX Set the display showing upper left X value

- LoadUpperLeftY Set the display showing upper left Y value

- LoadSizeX Set the display showing the horizontal size

- LoadSizeY Set the display showing the vertical size

- ReadUpperLeftX Read the value from the upper left X display register ReadUpperLeftY Read the value from the upper left Y display register

- ReadSizeX Read the value from the horizontal size display register

- ReadSizeY Read the value from the vertical size display register

- condition select.

- jump address loaded into the microprogram address counter if the condition is true

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 10

#### Control machine contains large number of states

- Selection of coordinates

- Upper left x, y of rectangle

- Width, hight of rectangle

- Update coordinate value

- Loop: read data, invert, write data, increment adress

- Address should run line by line, if necessary increment vertical address and restart horizontal address

- Total adress calculated automatically as y\*1024+x

2024-10-07 11

# Partitioning of Finite State Machine (FSM)

- · Main problem: Large set of possible sequences

- Dedicated FSM

- Complex to design

- Hard to modify

- Efficient

- Alternative: Microcoded FSM

- Structured, simple to design and modify

- Large overhead for small state machines

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 12

#### Microcoded FSM

- Some applications requires a longer or complex control step sequence

- E.g. controller for a microprocessor datapath

- · Some applications are too simple for a microprocessor design

- Datapath control

- Some microprocessors contains a microprogrammed controller

- Allow patching of processor

- E.g.; 68000 processor family

2024-10-07 13

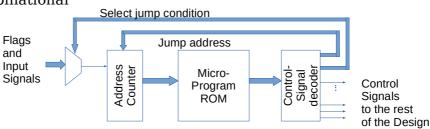

### Creating a microcontroller

- · Simple control machine

- ROM + register (FSM based on lookup table)

- · Replace register with a counter

- Next state usually corresponds to the next adress i the Lookup table

- Remove need for an adress to be specified in every control word

- Possible jump controlled by special control bit

- Conditional jump

- Control selects condition input, forcing adress load if active

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 14

#### Basic structure

- Expected sequence stored in ROM

- Once combination/state in each adress

- One clocked block

- Address counter

- All other combinational

2024-10-07 15

#### **Behavior**

- Moore machine only

- Control outputs never directly dependent on input

- · Conditional jump limited

- Adress +1 or one branch possible in current structure

- · Corresponds to single if-else

- Possible to expand hardware to support multichoice branching

- · Corresponds to a case-statement

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 16

#### **Timing**

- Expected signal update sequence

- Clock edge -> new adress

- New adress -> new control values

- New control values -> new next address

- Some control signals affect outputs in the datapath directly

- Example: output enable signals

- Some signals affect values on following clock edge

- Example: register load

- To move a value between a register to another

- In the same clock cycle enable the output register and the load enable of the reciever register

- The reciver register will contain the new value at the start of the next clock cycle

2024-10-07 17

# Programming

- Sequences are simple to create

- Signal sequence, auto increment counter

- Branching possible

- Number of concurrent branch adresses may be limited

- Combine sequences

- All sequences stored in one ROM

| Addr | contents |

|------|----------|

| 0    | S0       |

| 1    | S1       |

| 2    | S2       |

| 3    | Sa       |

| 4    | Sb       |

| 5    | Sc       |

| 6    | S6       |

| 7    | S7       |

| 8    | S8       |

| 9    | Sw       |

| 10   | Sx       |

| 11   | Sy       |

|      |          |

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 18

# Control signals

- Current example have long propagation delay (ROM lookup etc.)

- · Current example may have glitches on control signals

- Should not be a problem if design is fully synchronous

- · Additional registers may be added

- ROM output / control bit decode

- Will delay control signals relative to branching!

2024-10-07 19

### Control word (ROM output)

- · Can be split into different sections

- Individual control pins

- Branch selection

- Branch address

- · Individual bits controls data-path of the system

- · Branch related bits control sequence in controller

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 20

#### **Branch**

- Branch selection

- Encoded selection possible

- · Branch implemented as address register load

- · Branch may be done based on more than one input bit

- Example: microcontroller in microprocessor branch on status bit combinations such as zero or negative

2024-10-07 21

#### Branch, cont.

- · More specialized version possible if important

- Select 1 out of N (e.g., decode OPCODE in a processor)

- Dedicated hardware that compute start adress (small ROM)

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 22

# Design steps

- Partition into data flow and FSM

- Indicate control signals

- Create FSM graph

- Limit branching

- Define reset state

- Find sequences

- What should happen in which order

- Initially ignore if things can be done in parallel

2024-10-07 23

#### Design steps, cont.

- Compact sequences

- Datapaths may support multiple activities at once

- · Possibly find repeated sequences

- Sequence with same controls and same end

- · Assign addresses to sections of code, adjust branch addresses

- Translate to binary contents in memory

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 24

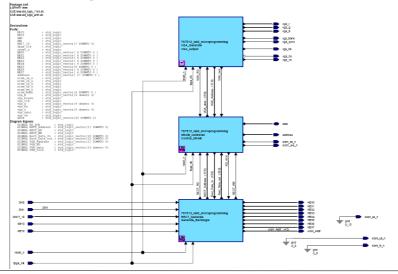

# Lab example structure

Lab example structure, cont.

Linkoping

Lin

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 26

#### Lab example, ROM

- Replace contents in ROM

- Use comment text as help

- Keep at least one '1' in each column of the control signals

- Not necessary for branch address or jump condition

- May get synthesis errors if not included

ARCHITECTURE behav OF microprogram IS

SUBTYPE memword is bit\_vector(28 downto 0); TYPE memarray is array (0 to 31) of memword;

```

CONSTANT microprogmem : memarray :=

LL

00

ee

aa

aa

oR

dd

dd

jmp

Ne D S S UU

re

UU

exDeSeSe ppLLppRR

ea

xtecetet ppooppee

Rd

eSRR tVcVtVtV eeaaeeaa

d

cWee HeHeHeHe rrddrrdd

t1cc ororor LLSSLLSS

D7tt rtrtrtrt eeiieeii

PPCCPPCC ffzzffzz

t1RW oonnoonn tteettee

branch

a0DR ssttsstt XYXYXYXY

Addr

(B"0000_00000000_00000000_0000_00000"

0

B"0000_00000000_00000000_0000_00000"

B"0000_00000000_00000000_0000_00000"

2

B"0000_00000000_00000000_0000_00000",

3

B"0000_00000000_00000000_0000_00000",

```

LINKÖPING UNIVERSITY

2024-10-07 27

# Lab example task

- Key press detection

- Multiple branch, wait for activation

- · Switch setting detection

- Multiple input branch

- Load/store coordinate info

- Multiple load/store?

- · Memory access

- Wait for acknowledge

- · Wait for key release after completing task

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 28

#### Example microcode use in processor

- Material from "TSEA83 Computer Hardware and Architecture" (by Michael Josefsson)

- Small simple microprocessor design

- Programming model is only accumulator, stack, program counter, index register, memory

- Shows fetch, decode and execute of one instruction

- Load accumulator with constant \$12.

- www.isy.liu.se/edu/kurs/TSTE12/forelasning/mikroprogram.pdf

2024-10-07

# Assembly programmers model of the microprocessor example

- Three registers accessible: A, PC, SP

- PC = program counter, SP = stack pointer, A = ackumulator

- Addressing modes: 6 possible

- Immediate (next byte is the value)

- Absolute (next byte is adress to value)

- ....

- Instructions: initially only LDA, STA and ADD

- LDA: load register A from memory

- STA: store register A into memory

- ADD: add a value from memory to the current value of A

TSTE12 Design of Digital Systems, Lecture 11

2024-10-07 30

#### Next time

- Microprocessor structure

- Assembly level programming

- C-level hardware access