## TODAY Processes: order of execution inside a process, processes for combinational logic, case statement, for... loop, taking care of the sensitivity list, ... Lab 4 2

### WHAT DOES THIS CIRCUIT DO?

```

process (clk, reset)

begin

if reset = '1' then

z <= (others => '0');

elsif rising_edge (clk) then

if UD = '1' then

z <= z + 1;

else

z <= z - 1;

end if;

end if;

end process;</pre>

```

As usual, to know what it does you only need to draw the circuit. 3

# <text>

### ... AND THIS ONE?

```

process (clk, reset)

begin

if reset = '1' then

z <= (others => '0');

elsif rising_edge (clk) then

if UD = '1' then

z <= z + 1;

end if;

z <= z - 1;

end if;

end process;</pre>

```

## PROCESS EXECUTION A process is evaluated only when there is a change of one of the signals in the sensitivity list. Only in that moment, the entire process is evaluated. Output signals are assigned the last value that they are given during the process evaluation. If no value is assigned to an output of a process during an execution of the process, then the output keeps its previous value. Thus, it is important to define which is

the value of the output for each possible combination of inputs. Otherwise we may have unexpected behaviors.

### WHAT DOES THIS CIRCUIT DO?

```

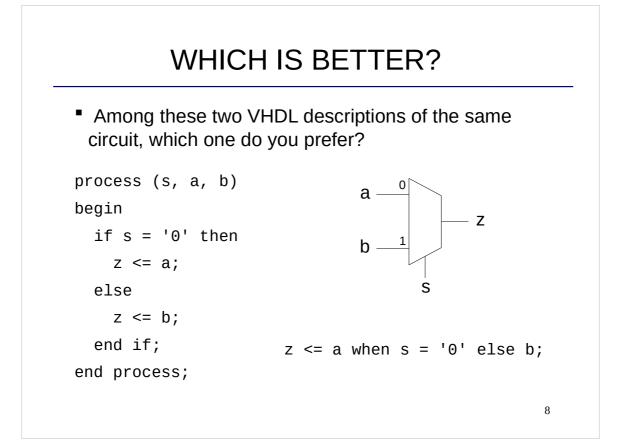

process (s, a, b)

begin

if s = '0' then

z <= a;

else

z <= b;

end if;

end process;</pre>

```

Is it a combinational circuit or a sequential one?

### PROCESS FOR COMBINATIONAL LOGIC

- We can use processes for describing combinational logic, not only sequential one.

- In most cases, however, the description of a combinational circuit using processes is more complicated and more difficult to understand than the normal description. Thus, try not to use processes for combinational logic unless it is strictly necessary.

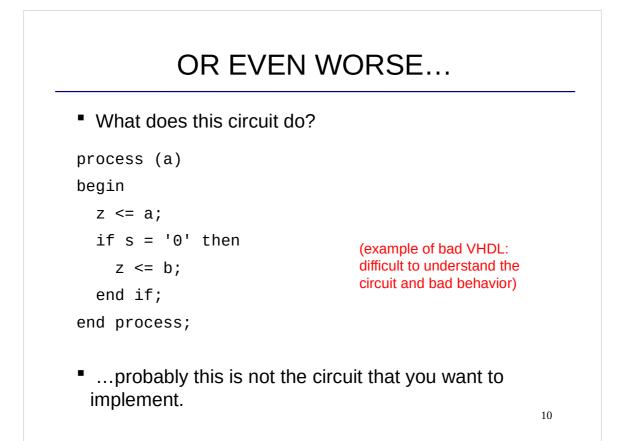

- We also have to be careful. What happens here?:

```

process (s)

begin

if s = '0' then

z <= a;

else

z <= b;

end if;

end process;</pre>

```

(example of bad VHDL)

| FUNCTION                                     |     |     |   | REG RAM | ROM |

|----------------------------------------------|-----|-----|---|---------|-----|

| Calculate logic functions                    | х   |     |   |         |     |

| Calculate mathematical operations            |     |     | х |         |     |

| Delay a signal                               |     |     |   | х       |     |

| Store signals                                |     |     |   | х       |     |

| Compare signals                              | (X) |     | Х |         |     |

| Detect a transition in a signal              | х   |     |   | Х       |     |

| Count                                        | (X) |     | х | х       |     |

| Select among several signals                 |     | x   |   |         |     |

| Transform serial-parallel or parallel-serial |     | (X) |   | х       |     |

| Store constant values                        |     |     |   |         | x   |

| Create a state machines                      | х   |     |   | х       |     |

|                                              |     |     |   |         |     |

|                                              |     |     |   |         |     |

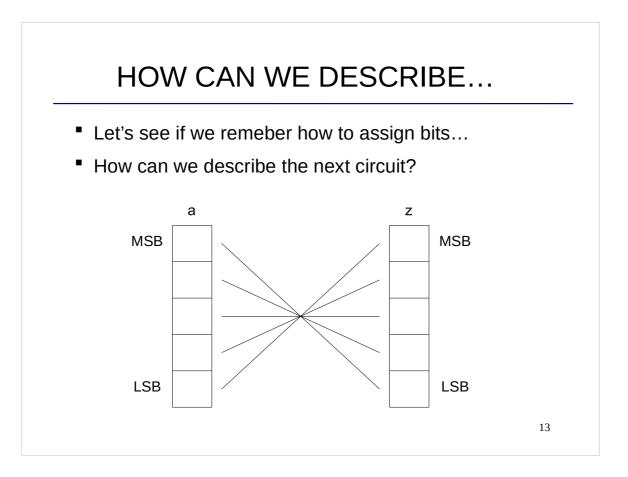

### FOR ... LOOP

First option: normal assignments:

```

z(4) <= a(0);

```

```

z(3) <= a(1);

z(2) <= a(2);

```

```

2(2) = u(2)

```

```

z(1) <= a(3);

z(0) <= a(4);

```

```

Second option: for...loop statement:

```

```

process (a)

```

begin

```

for i in 0 to 4 loop

```

```

z(i) <= a(4-i);

```

end loop;

end process;

Which description would you prefer if a and z have 32 bits?

14

### CASE STATEMENT: EXAMPLE 1

Case statement for sequential logic:

to change under other circumstances).

```

process(clk) --IMP: clk: the only triggering signal

begin

if rising_edge (clk)

case s is

when '0' => z <= a;

when '1' => z <= b;

end case;

end if;

end process

• Note that in sequential logic, the sensitivity list of the process only

needs to include the clk and reset (sequential logic does not need

```

```

CASE STATEMENT: EXAMPLE 2

Case statement for combinational logic:

process(s, a, b)

begin

case s is

when '0' => z <= a;

when '1' => z <= b;

end case;

end process

Note that s, a and b need to be in the sensitivity list.

Do you recognize this circuit?

```

### LAB 4

- Control the audio codec used to input/output analog waveforms

- · Get audio signal into FPGA, modify, send back out

- Audio codec communicates with FPGA in serial form

- Compare with lab 2, keyboard data recieved in serial form

- Input signal in stereo, can reuse parts of the design

- Use hierarchy (block diagram) to use the same design in two situations

18

### LAB 4

- Control the audio codec used to input/output analog waveforms

- · Get audio signal into FPGA, modify, send back out

- Input signal in stereo, can reuse parts of the design

- Use hierarchy (block diagram) to use the same design in two situations

- Audio codec communicates with FPGA in serial form

- Compare with lab 2, keyboard data recieved in serial form

- Processing inside FPGA expect parallel form (vector)

- Left data in, Left data out, Right data in, Right data out, Irsel

- Irsel change indicate new input value

### LAB 4

- Hierarchical design

- Ctrl block to create control signals and clocks

- Implemented as a counter + decoding/selection of bits

- Channel\_Mod block to convert between serial and parallell form

- · Shift registers only active when block is selected

- Only 16 of 32 input bits should be saved in register

### 20

### CHECKLIST FOR LECTURE 7

- VHDL processes:

- order of execution inside a process.

- taking care of the sensitivity list.

- processes for combinational circuits.

- for...loop.

- case statement.

- Lab 4

### AT HOME

- Review the checklist for lecture 7 and check that you understand all the concepts and you know how to use them.

- Start prepare for lab 4