# Data types. Memories. FIFO/Buffer. Description of the Project. Description of Lab 3.

#### DATA TYPES

- VHDL is strongly typed: The type of each signal must always be clear.

- Operators depend on the type. Example: the operator < gives a different result for signed and unsigned, and cannot be used with std\_logic\_vector.

- Some standard types (predefined in VHDL):

```

type boolean is (true, false);

type integer is range -2147483648 to +2147483647;

type real -- real value

type time -- integer number plus unit (ns, ms,...)

Some types are synthesizable, such as boolean or integer and

```

- Some types are synthesizable, such as boolean or integer and some types are not, such as real or time.

- Good description and further information on data types: [R4].

3

## TYPES OF TYPES Integer types: type integer is range -2147483648 to +2147483647; type short is range -128 to 127;

Subtypes:

subtype natural is integer range 0 to integer'high;

Enumeration:

```

type std_logic is ('U','X','0','1','Z','W','L','H','-');

type bit is ('0','1')

```

type boolean is (false, true);

Array:

type memory is array (0 to 2\*\*bitsAddr -1) of std\_logic\_vector (WL -1 downto 0);

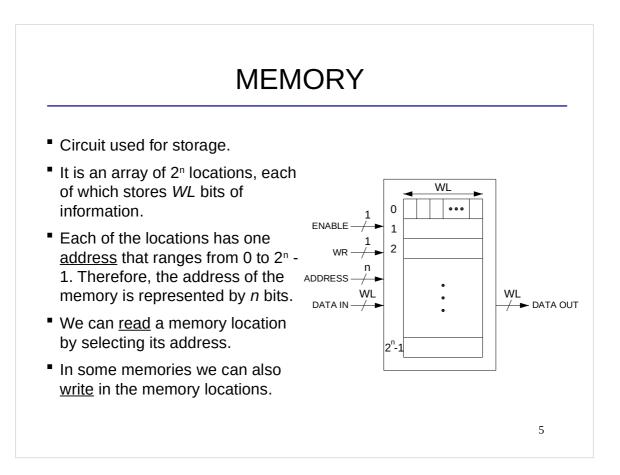

#### TYPES OF MEMORY

- Internal memory (we can create them in the FPGA):

- $\hfill\square$  RAM: Random Access Memory (we can read and write to it).

- $\hfill \ensuremath{\,\mathbb{I}}$  ROM: Read Only Memory (fixed values that we cannot modify).

- External memory (outside the FPGA):

- $\ensuremath{\,{\rm I}}$  RAM and ROM: They can be external as well.

- <sup>I</sup> SRAM: Static RAM (static = does not need refresh).

- <sup>I</sup> SDRAM: Synchronous Dynamic RAM (dynamic = needs refresh).

- $\hfill\square$  DDR SDRAM: Double Data Rate SDRAM (upper and lower edge).

- $\square$  FLASH (non volatile = the content is not erased without power).

- The DE2-115 board includes 2x 64MB SDRAM, a 2 MB SRAM and an 8 MB FLASH.

#### **ROM IN VHDL**

#### RAM IN VHDL

### DUAL-PORT RAM

- Dual-Port: memory in which it is possible to write on a memory location and read from another one. Obviously, it uses more resources (more area) than a single-port memory.

- wAddr: write address; rAddr: read address.

```

process (clk)

begin

if rising_edge (clk) then

if we = '1' then

RAM_content (to_integer(unsigned(wAddr))) <= data_in;

end if;

data_out_reg <= data_out; -- If we want to register the output

end if;

end process;

data_out <= RAM_content (to_integer(unsigned(rAddr)));

9

```

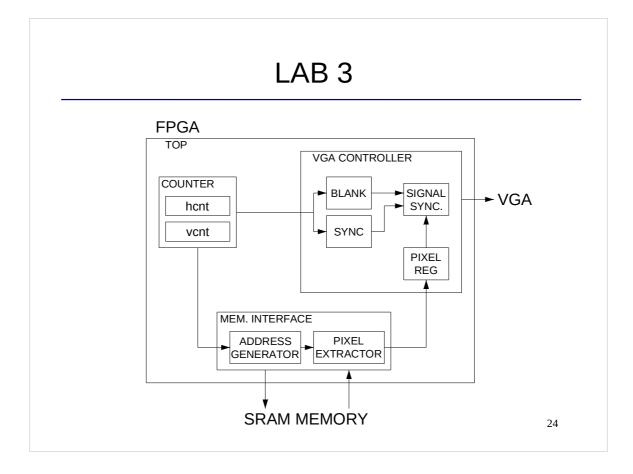

#### PROJECT

- Aim: Develop a complete functional system using the DE2-115 board and the FPGA included in it.

- Task: Use the DE2-115 board to modify/analyze a sound signal (in stereo) that is generated by a phone. The input sound signal shall be converted into digital form and modified on the FPGA. The output sound shall be sent to the loudspeakers. Information related to the signal will be displayed graphically on a VGA attached to the board. The red and green LEDs and 7-segment displays on the DE2-115 board can also be used for this purpose. Everything can be controlled using the push buttons and switches on the board, or from an attached keyboard.

11

#### GENERAL REQUIREMENTS

- It has to fit in the DE2-115 board and in the FPGA.

- All the hardware on the board can be used: push buttons, displays, switches, SRAM memory, infrared port, etc.

- All groups must implement a digital volume control and balance for the incoming sound signal. The volume shall have at least 10 levels of resolution, and the balance shall also have at least 10 levels.

- Apart from these general requirements, each project group has to choose an alternative task.

#### ALTERNATIVE TASKS

- 1) Digital Osciloscope.

- 2) Signal level indicator.

- 3) Echo.

- 4) Equalizer (recommended course in digital filters).

- 5) Task proposed by the students.

Together with the specific task, each project group has to propose a small "improvement" or distinctive feature that makes their system different to any other project.

#### SOME PROJECTS OF PREVIOUS STUDENTS WERE

- 1) Sound board

- 2) Piano

- 3) Tamagotchi

- 4) Videogame

- 5) Karaoke

- 6) ...

#### PHASES OF THE PROJECT

- Create the project groups.

- Define the requirements of the system:

- Write the Requirement Specification document.

- Hardware design:

- Do the hardware design of the system.

- Write the Design Specification and the Project Plan documents.

- First Presentation.

- Description in VHDL:

- Do the VHDL description in the lab.

- Write the Project Report document.

- Final Presentation and Demo.

15

#### CREATING THE GROUPS

- Groups of approx. 6 people.

- Decide your group and sign up between Sep. 8<sup>th</sup> and 9<sup>th</sup>.

- Use an existing excel sheet in Teams

- Group members must:

- Pass labs 1 and 2 to be allowed to do the project (deadline Sep. 12<sup>th</sup>).

- We will publish the list of project groups on Sep. 9<sup>th</sup>

- Lab deadline on Sep. 12<sup>th</sup> may force changes to project groups

#### **DEFINITION OF REQUIREMENTS**

- As soon as your group is confirmed (on Sep 10<sup>th</sup>), book the first meeting with the supervisor.

- To book the meeting, the supervisor will have a list on the board outside the MUX:en lab, where you can write your group number.

- First meeting (Sep. 12<sup>th</sup> or 13<sup>th</sup>):

- Discuss the project tasks that you have thought about. Ask questions that you have. Decide the project manager.

- After the meeting, write the Requirement Specification. Submit it 24h before the second meeting.

- Second meeting (Sep. 15<sup>th</sup> or 16<sup>th</sup>):

- Discuss the proposed Requirement Specification with the 17 supervisor.

#### HARDWARE DESIGN PART

- In this phase you have to do the hardware design part of your system (no VHDL implementation).

- The result of this phase will be the Design Specification and Project Plan documents, and the First Presentation.

- The supervisor and the other teachers will be available for discussions. You will also have a third meeting with the supervisor, where you discuss the first version of the Design Specification.

- It is important that you plan this phase well. Doing the hardware design and explaining it in the document takes time and cannot be done in a few days.

#### DESCRIPTION IN VHDL PART

- In this phase, you have to describe your design in VHDL.

- The result of this phase will be the Project Report and the Final Presentation.

- The lab rooms will be available and you are welcome at any time.

- Your supervisor and the other teachers will be available to help you.

- If you did a good design, the description in VHDL should be easy to do. For debugging, prepare a good test bench.

19

#### DOCUMENTS

- Information that you have to read and use:

- Project Specification.

- Guidelines to Write the Documents for the Project.

- How to Design a HW System.

- How to Describe a HW Circuit.

- Template for the Time Reports.

- Document that you have to create (in English):

- Requirement Specification.

- Design Specification and Project Plan.

- Project Report.

- (Optional) Video.

- First Presentation, Final presentation.

#### **MEETING ROOM**

- It is located at the entrance of the MUX1-3 labs.

- Students can book it at any time.

- There is a calendar at the entrance of the room to book it.

- It is not allowed to eat in the meeting room. If you want to eat, go to the student kitchen that is at entrance 25, very close to the labs.

21

#### GRADING

- To pass the project you have to pass all the parts of the project:

- Requirement Specification.

- Design Specification and Project Plan.

- First Presentation

- Project Report.

- Final presentation and Demo.

#### TO TAKE INTO ACCOUNT

- In today's presentation we have seen a summary of the project. The complete information is in the **Project** Specification document. Read it carefully.

- The Project Specification is clearly divided in phases, so that you know what you have to do at each time.

- For writing documents, read also carefully the Guidelines to Write the Documents for the project.

- Deadlines are shown on the web page of the course.

- If you get stuck, do not waste time. Ask the teachers!

#### **CHECKLIST FOR LECTURE 5**

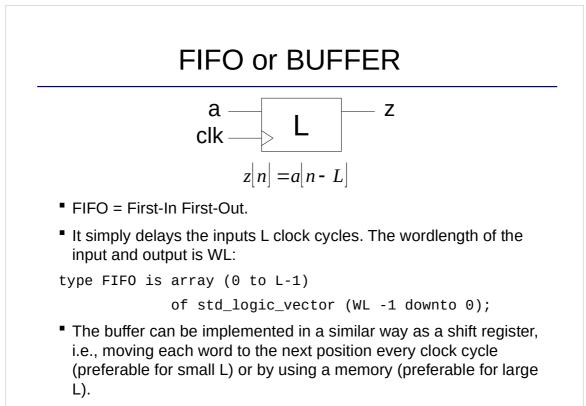

- Storage circuits: memory types, RAM, ROM, FIFO/Buffer.

- VHDL: type, boolean, real, time, enumeration, array, RAM, Dual-port RAM, ROM.

- Description of the project (development part).

- Description of Lab 3.

25

#### AT HOME

- Review the checklist for lecture 5 and check that you understand all the concepts and you know how to use them.

- Read the Project Specification document carefully.

- Find classmates to form a group together with them.

- Prepare Lab 3.