Lecture 6: Lab 2 intro, Pitfalls when coding, debugging, Design for FPGAs

Material by Andreas Ehliar

LINKÖPING UNIVERSITY

TSEA44: Computer hardware - a system on a chip

2022-11-22 2

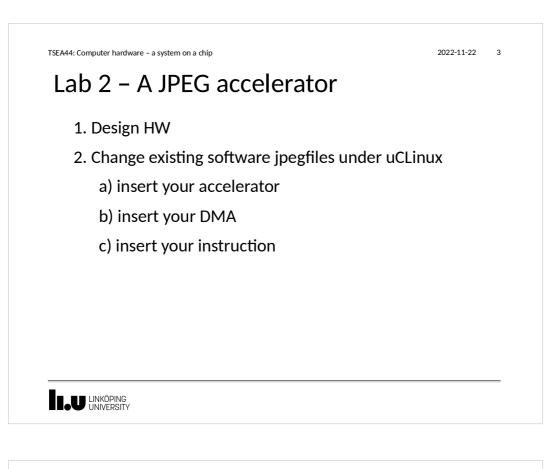

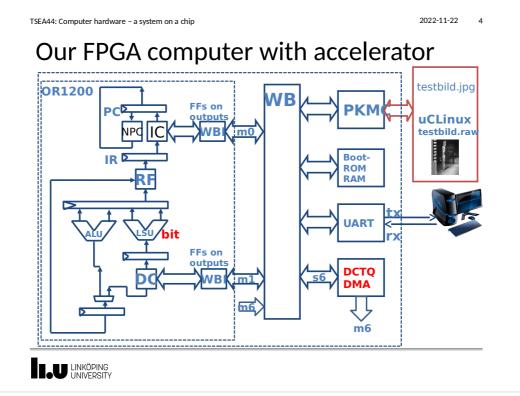

#### Agenda

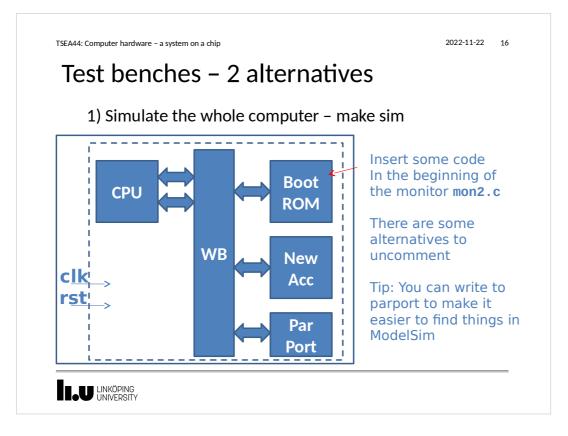

- Lab2 introduction (shown already at end of lecture 4)

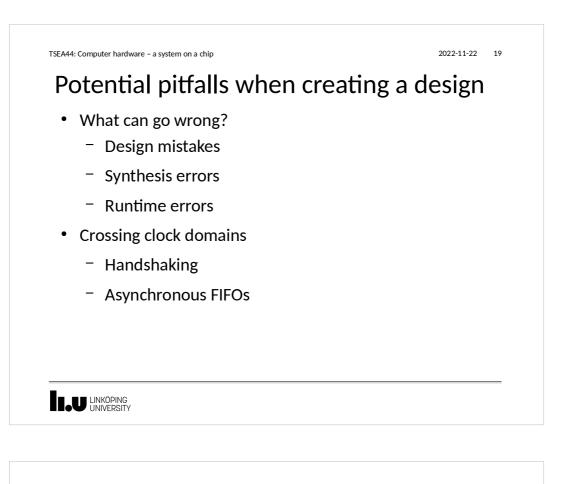

- Pitfalls when writing code

- Debugging

- Influence of goal hardware on architecture and code style

2022-11-22

8

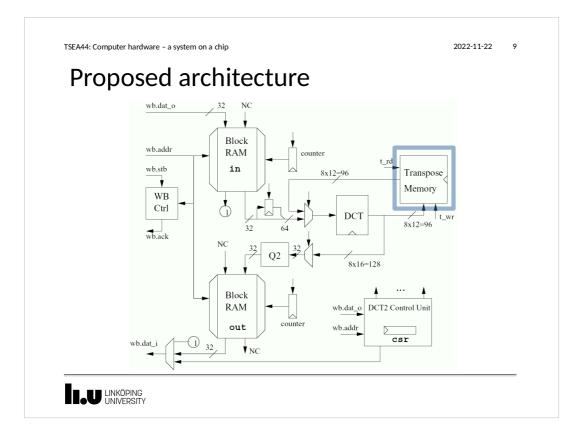

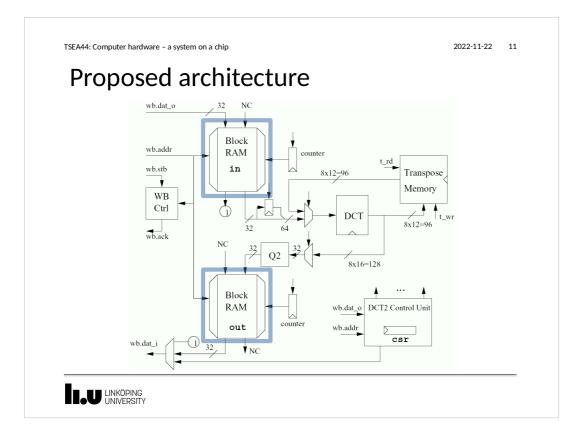

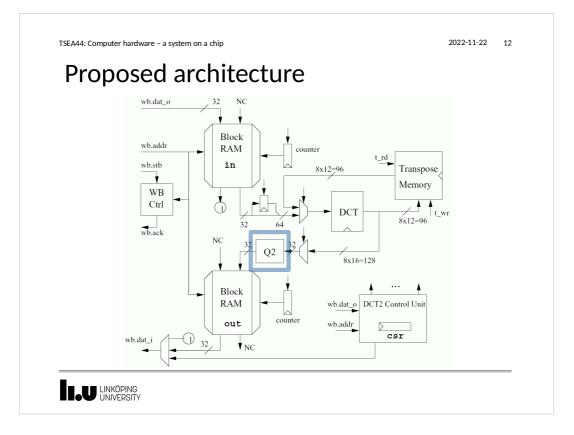

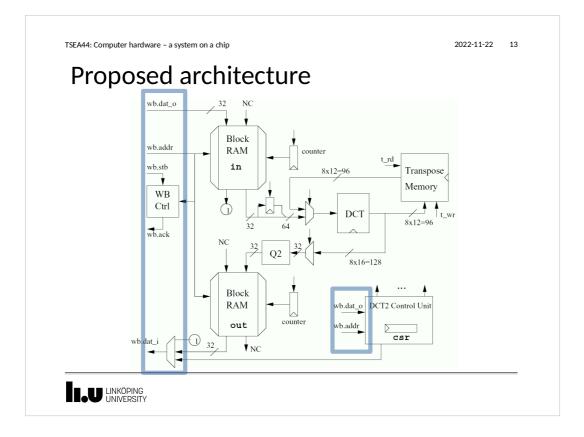

#### DCT module

- Given to you

- 1D DCT

- 8 in ports (12 bits), 8 out ports (16 bits)

- Fix point arithmetic

- Straightforward implementation of Loeffler's algorithm

```

2022-11-22 18

TSEA44: Computer hardware - a system on a chip

wb_tasks.sv

module wishbone_tasks(wishbone.master wb);

int result = 0;

reg oldack;

reg [31:0] olddat;

always @(posedge wb.clk) begin

oldack <= wb.ack;

olddat <= wb.dat_i;</pre>

end

task m_read(input [31:0] adr, output logic [31:0] data);

begin

@(posedge wb.clk);

wb.adr <= adr;

wb.stb <= 1'b1;</pre>

wb.we <= 1'b0;

wb.cyc <= 1'b1;

wb.stb <= 1'b0;

wb.we <= 1'b0;

wb.cyc <= 1'b0;</pre>

wb.sel <= 4'hf;</pre>

wb.sel <= 4'h0;

@(posedge wb.clk);

data = olddat;

#1;

while (!oldack) begin

end

endtask // m_read

@(posedge wb.clk);

#1;

endmodule // wishbone_tasks

end

```

2022-11-22 20

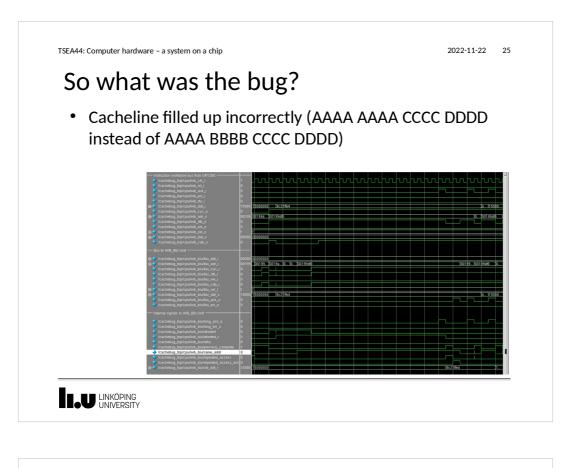

#### A design bug

- Symptom: The boot sequence of uClinux hangs after a second when the Icache is on.

- Uclinux boots ok with Icache off

- No problems detected in the monitor when the icache is on

2022-11-22 24

#### Handling long simulation runtime, cont.

- Now you can pinpoint the time interval where the crash happened

- Restore the checkpoint in Modelsim that occured closest before the actual crash

- vsim -restore 600ms.chk

- Debug as usual (by adding signals to wave window/etc)

2022-11-22 26

# What if you cannot find a bug during simulation?

- Very likely you have some undefined behavior in your design

- Race condition in RTL code (blocking vs non-blocking assignment)

- Incorrect use of "don't cares"

- You are not crossing clock domains correctly

- etc.

- Not so likely:

- You have triggered a bug in the CAD tools

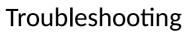

• Post Place-and-Route (PAR) simulation

- Generate a new netlist using netgen

- Simulation done with LUTs and FF

Available for lab0! make sim\_lab0\_sdf See lab webpage

2022-11-22 30

#### Simulation ok, but still not working?

- Add measurement logic to the FPGA Design

- Use switches and LEDs

- Chipscope/Signaltap

- Add logic analyzer function to the FPGA design

- Store samples in blockRAM or similar

- Communicate with PC over JTAG

- Warning!

- Many people think signaltap/chipscope replace simulation. It does not! Better to spend time writing better testbench

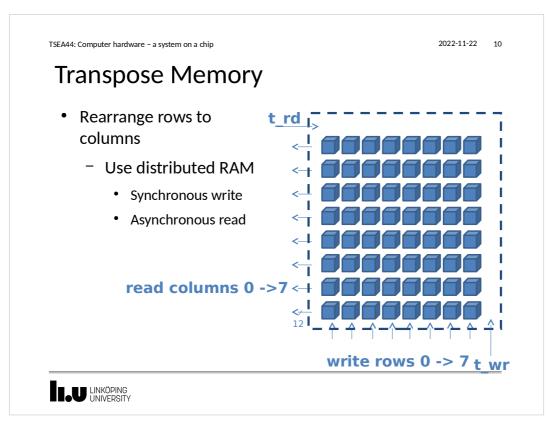

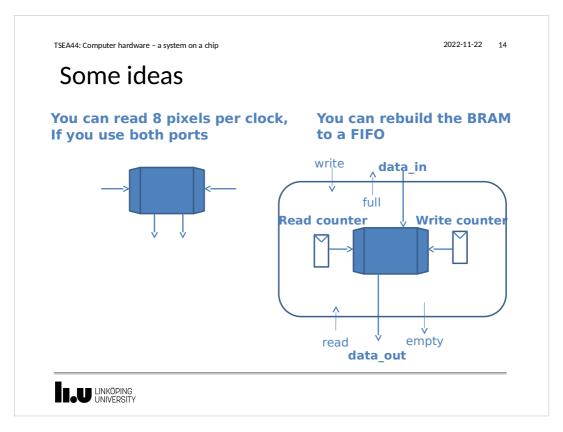

### Memory guidelines

- Standard rule: Large memories should be synchronous

- For high frequency design you want to register the output of the memory as well.

- For power reasons you should not enable the memory unless necessary

- Double check that your enables work when inferring a memory!

- Smaller memories may be asynchronous if necessary

- You should not have a reset signal for your memory array

- Easy to forget for shift registers!

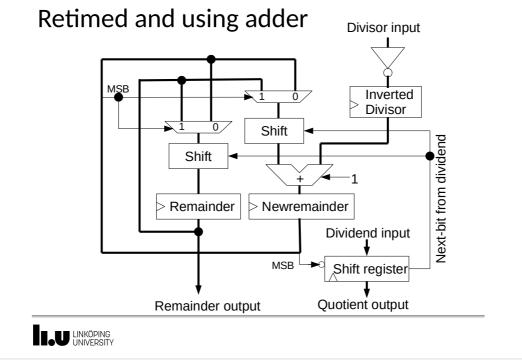

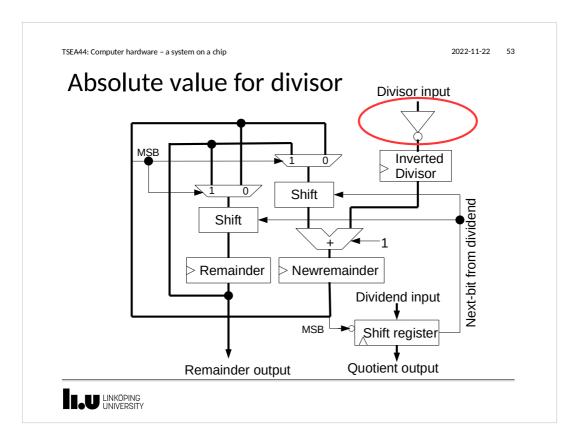

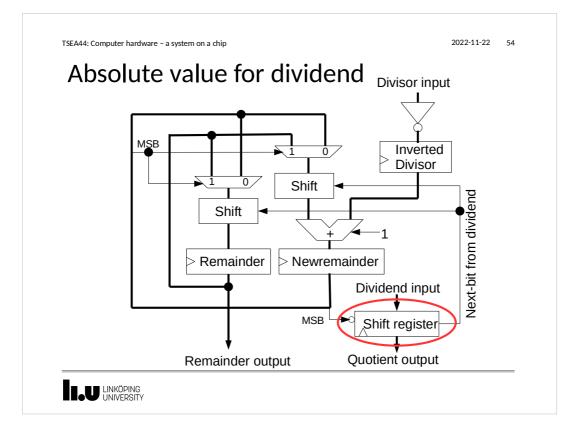

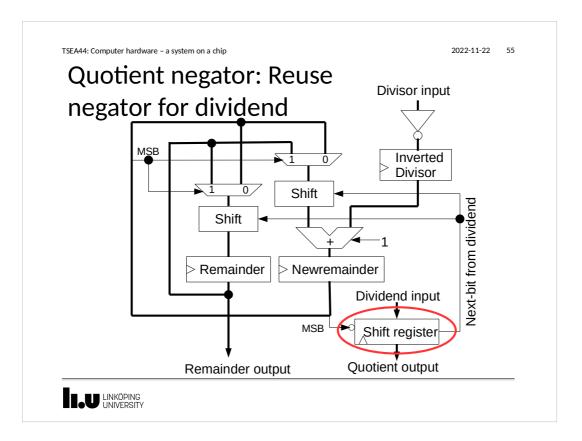

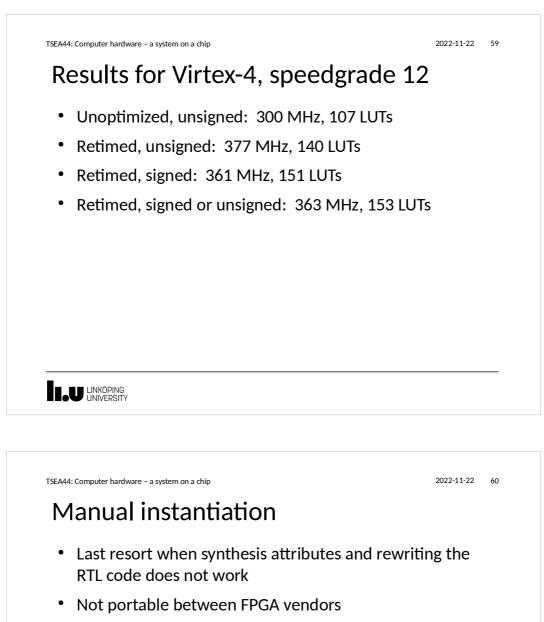

#### Dealing with negative numbers

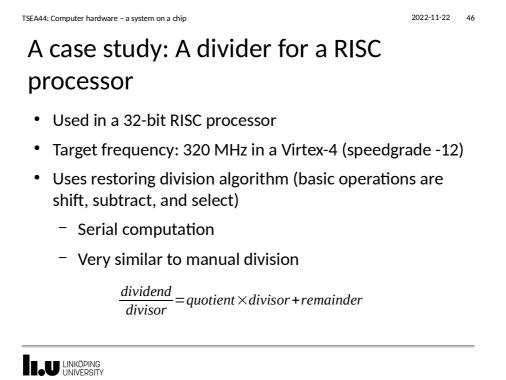

- Idea: Take absolute value of dividend and divisor

- Negate quotient and remainder if necessary

- For a 32 bit divider this seems to require around 128 extra LUTs...

2022-11-22 58

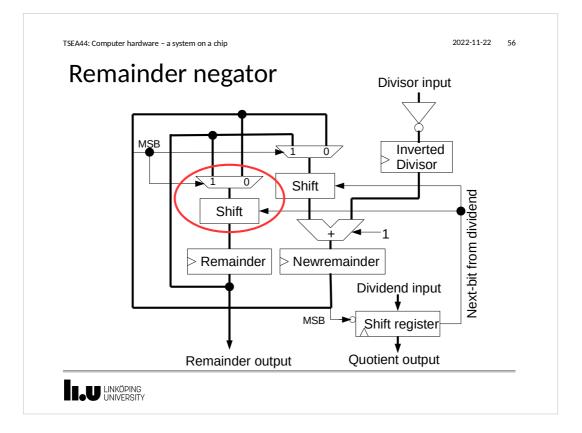

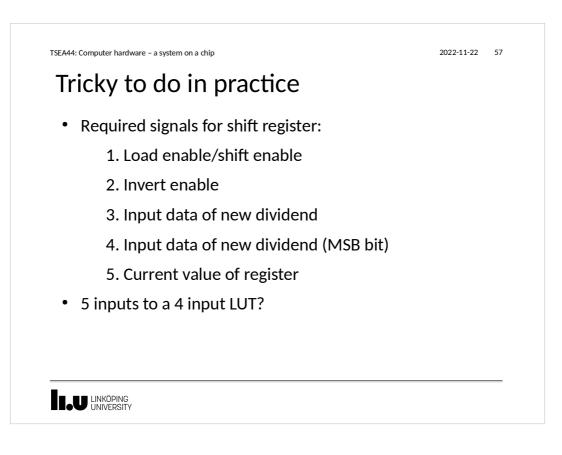

#### Tricky to do in practice - Solution

- Solution: Skip MSB of dividend input for ABS operation

- Always invert the dividend, only add 1 as a carry in if appropriate

- This can be implemented by adding a few extra LSB bits

- If we had a positive value we can compensate for the inversion at shift out

- We can even add a control bit to select between signed/unsigned division

- Manual instantiation was necessary to actually implement this

- Suprisingly portable to ASIC however

• Well documented in various application notes

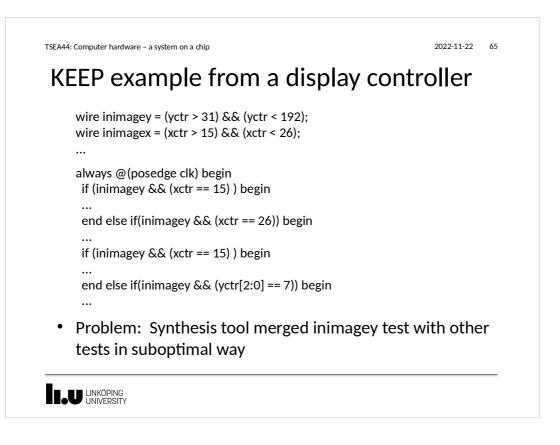

2022-11-22 64

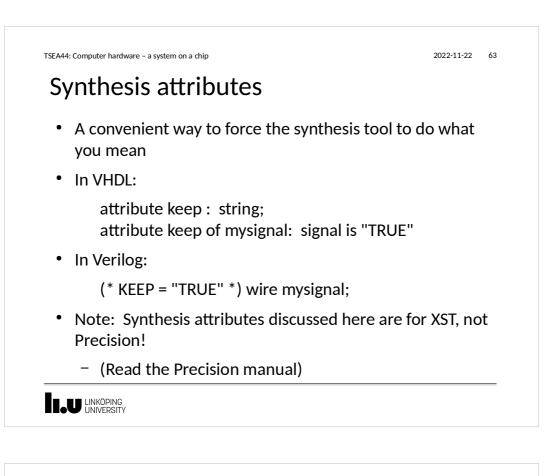

### Synthesis attribute KEEP

- Preserves the selected signal

- Use case:

- The synthesis tool makes a bad optimization decision.

- By using KEEP you can ensure that a certain signal is not hidden inside a LUT and hence guide the optimization process

```

TSEA44: Computer hardware - a system on a chip

```

2022-11-22 66

# Solution: Force inimagey and inimagex to be separate signals

(\* KEEP = "TRUE" \*) wire inimagey; (\* KEEP = "TRUE" \*) wire inimagex;

assign inimagey = (yctr > 31) && (yctr < 192); assign inimagex = (xctr > 15) && (xctr < 26);

- Saved area in an area constrained situation

- Especially important when targetting both CPLD and FPGAs with a single IP core

Two signals into mux control signal

\_\_\_\_\_