# TSEA44: Computer hardware – a system on a chip

Lecture 7: DMA, lab3, testbenches

TSEA44: Computer hardware - a system on a chip

#### Today

- Hints for documentation

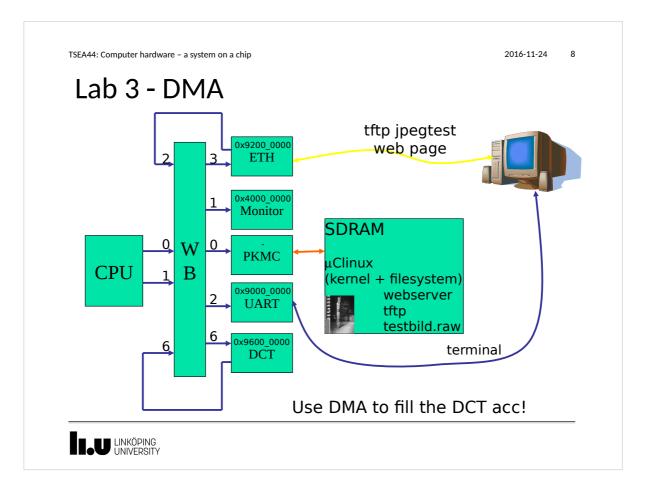

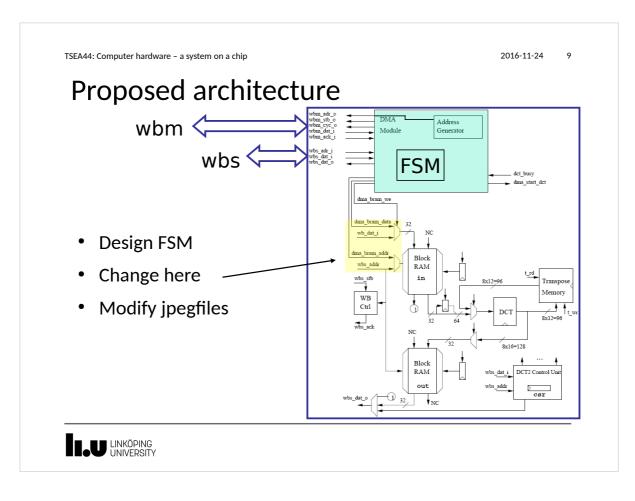

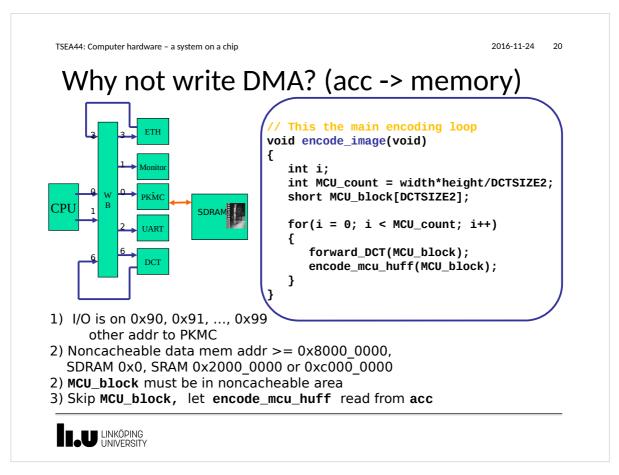

- DMA

- Lab3

- Testbenches

2016-11-24

2

TSEA44: Computer hardware - a system on a chip

#### 2016-11-24

4

#### **Creating schematics**

- Alternatives

- Openoffice/libreoffice diagram tool (I use this for slides)

- Inkscape (potentially very nice looking, very cumbersome though)

- Dia (decent if you have RTL library for it)

- TikZ (if you really like latex)

- MS Paint (I'm only kidding)

- Hand drawn schematics from whiteboard/paper

- Quality problems...

- Visio (if you have a license for it)

```

TSEA44: Computer hardware - a system on a chip

```

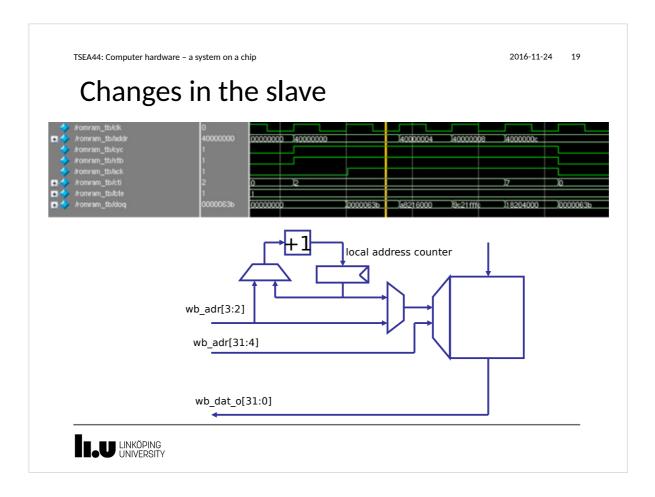

## Address generation

- We want to transfer block by block (8x8)

- Address generator must konw format (width, height) of image

testbild.raw

|                                 | •                             |                     | mory                   |                 |                      |                             | • /                 |                  |                     |                          |                |

|---------------------------------|-------------------------------|---------------------|------------------------|-----------------|----------------------|-----------------------------|---------------------|------------------|---------------------|--------------------------|----------------|

| wave - default                  | i                             |                     |                        |                 |                      |                             |                     |                  |                     |                          |                |

| le <u>E</u> dit ⊻iew <u>I</u> n | sert F <u>o</u> rmat <u>T</u> | ools <u>W</u> indow |                        |                 |                      |                             |                     |                  |                     |                          |                |

| 🖻 🖥 🖨 🎇                         | 🕺 🖻 🛍                         | # 🖌 🕹               | 🕺 T= 🗕 🗍 I 🗈           | 1 🖓 🎆           | 14.6.                | -54 nim ¥                   | 1 년 및               | ( y)=   🔊        |                     |                          | đ              |

|                                 | Ð, Q, Q, 🖪                    | 3+   ≣≹             |                        |                 |                      |                             |                     |                  |                     |                          |                |

|                                 | St1                           |                     |                        |                 |                      |                             |                     |                  |                     |                          |                |

| <b>⊕</b> ∲ adr<br>⊕∲ <- dat     | 90000003<br>zzzzzzz           | 4000319c            | )000000800<br>(00f0ff6 |                 | <u>)(40)(00)</u><br> | 40 (00)(40                  | . <u>(</u> 96000804 | <u> 140196</u> ] | (40)(00000804<br>(( | <u>(40</u> )<br>2000fff0 | .) <u>(00)</u> |

| ⊕–-∲dat-><br>-∳stb              | 00030003<br>St0               | 00000000            | <u>XOOfOff6e</u>       | <u>)00)00</u> . | <u>. XooXooX</u>     | 00 <u>)</u> 00 <u>)</u> 000 | 00000               |                  | XOOOOffio           | <u> (00.</u>             | <u>, (00 )</u> |

| s0_ack                          | 510<br>510                    |                     |                        |                 |                      |                             |                     |                  |                     |                          |                |

| — PARPORT —<br>⊕-� out_pad_o    | 0000000                       | 0000003             |                        |                 |                      |                             |                     |                  |                     |                          |                |

|                                 |                               |                     |                        |                 |                      |                             |                     |                  |                     |                          |                |

| Now                             | 00000000 ps                   |                     | 718400 ns              |                 |                      |                             | 1                   |                  |                     | 7103                     | 00 ns          |

| Cursor 1                        | 739995184 ps                  |                     | 7 16400 hs             |                 |                      | 7188                        | ou ns               |                  |                     | 7192                     | oo ns          |

| Cursor 2<br>Cursor 3            | 716922301 ps<br>712093092 ps  |                     |                        |                 |                      |                             |                     |                  |                     |                          |                |

| Cursor 4                        | 698544481 ps                  |                     |                        |                 |                      |                             |                     |                  |                     |                          |                |

| <                               | 4 F                           | KI                  |                        | lta: 4          |                      |                             |                     |                  |                     |                          |                |

| TSEA44: Computer hardware - a system on a | a chip |

|-------------------------------------------|--------|

|-------------------------------------------|--------|

2016-11-24 18

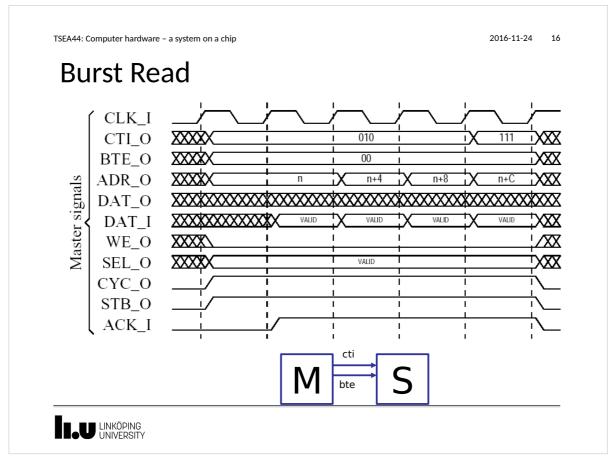

#### Burst cycle types

| Signal group | Value   | Description                  |

|--------------|---------|------------------------------|

| cti          | 000     | Classic cycle                |

|              | 001     | Constant address burst cycle |

|              | 010     | Incrementing burst cycle     |

|              | 011-110 | Reserved                     |

|              | 111     | End of burst                 |

| bte          | 00      | Linear burst                 |

|              | 01      | 4-beat wrap burst            |

|              | 10      | 8-beat wrap burst            |

|              | 11      | 16-beat wrap burst           |

TSEA44: Computer hardware - a system on a chip

#### Burst access

- Note: Only the SRAM memory controller i the Leela memory controller has burst support

- It is a graphics controller not used in our lab setup

```

TSEA44: Computer hardware - a system on a chip

2016-11-24

24

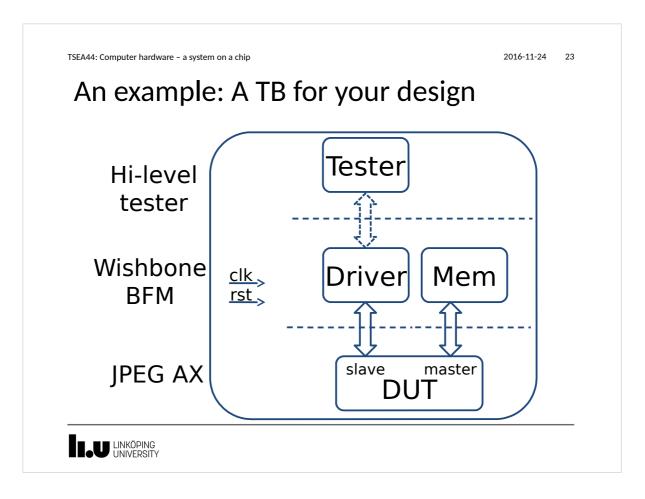

Testbench: top level

module jpeg_top_tb();

clk = 1'b0;

logic

rst = 1'b1;

logic

wishbone wb(clk,rst), wbm(clk,rst);

initial begin

#75 rst = 1'b0;

end

always #20 clk = ~clk;

// Instantiate the tester

tester tester0();

// Instantiate the drivers

wishbone_tasks wb0(.*);

// Instantiate the DUT

jpeg_top dut(.*);

mem memO(.*);

endmodule // jpeg_top_tb

```

```

TSEA44: Computer hardware - a system on a chip

2016-11-24

25

Testbench: Hi-level tester

program tester();

int result = 0;

int d = 32'h01020304;

initial begin

for (int i=0; i<16; i++) begin</pre>

jpeg_top_tb.wb0.m_write(32'h96000000 + 4*i, d); // fill inmem

d += 32'h04040404;

end

jpeg_top_tb.wb0.m_write(32'h96001000, 32'h01000000); // start ax

while (result != 32'h8000000)

jpeg_top_tb.wb0.m_read(32'h96001000,result);

// wait for ax

for (int j=0; j<8; j++) begin</pre>

for (int i=0; i<4; i++) begin</pre>

// print outmem

jpeg_top_tb.wb0.m_read(32'h96000800 + 4*i + j*16,result);

$fwrite(1,"%5d ", result >>> 16);

$fwrite(1,"%5d ", (result << 16) >>>16);

end

$fwrite(1,"\n");

end

end

endprogram // tester

```

```

TSEA44: Computer hardware - a system on a chip

2016-11-24

26

Testbench: mem

module mem(wishbone.slave wbm);

logic [7:0] rom[0:2047];

logic [1:0] state;

logic [8:0] adr;

integer

blockx, blocky, x, y, i;

initial begin

// A test image, same as dma_dct_hw.c

for (blocky=0; blocky<`HEIGHT; blocky++)</pre>

for (blockx=0; blockx<`WIDTH; blockx++)</pre>

for (i=1, y=0; y<8; y++)

for (x=0; x<8; x++)</pre>

rom[blockx*8+x+(blocky*8+y)*`PITCH] = i++; // these are not wishbone cycles

end

assign wbm.err = 1'b0;

assign wbm.rty = 1'b0;

always_ff @(posedge wbm.clk)

if (wbm.rst)

assign wbm.ack = state[1];

state <= 2'h0;</pre>

else

always_ff @(posedge wbm.clk)

case (state)

adr <= wbm.adr[8:0];</pre>

2'h0: if (wbm.stb) state <= 2'h1;

assign wbm.dat_i = {rom[adr], rom[adr+1],

2'h1: state <= 2'h2;

rom[adr+2], rom[adr+3]};

2'h2: state <= 2'h0;

endmodule // mem

endcase

```

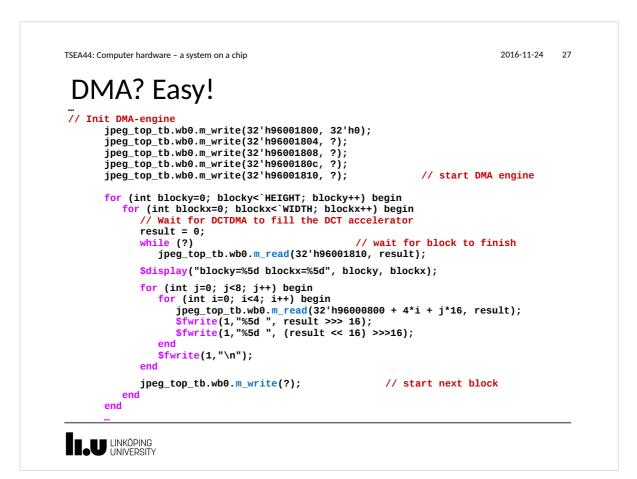

```

TSEA44: Computer hardware - a system on a chip

2016-11-24

28

// ***************

task m_read(input [31:0] adr,

wishbone_tasks.sv

output logic [31:0] data);

begin

@(posedge wb.clk);

wb.adr <= adr;

wb.stb <= 1'b1;

May/may not consume time

wb.we <= 1'b0;

•

May/may not be synthable

wb.cyc <= 1'b1;

•

Do not contain always/initial

wb.sel <= 4'hf;

Do not return values. Pass via output,

@(posedge wb.clk);

#1;

module wishbone_tasks(wishbone.master wb);

while (!oldack) begin

int result = 0;

@(posedge wb.clk);

reg oldack;

#1;

reg [31:0] olddat;

end

wb.stb <= 1'b0;

always_ff @(posedge wb.clk) begin

wb.we <= 1'b0;

oldack <= wb.ack;

wb.cyc <= 1'b0;

olddat <= wb.dat_i;</pre>

wb.sel <= 4'h0;

end

data = olddat;

adı

end

m_read

wh

endtask // m_read

data<

// ********

task m_write(input [31:0] adr,

adr

input [31:0] dat);

write

// similar to m_read

dat

<u>endtask // m_write</u>

endmodule // wishbone_tasks

28

```

```

TSEA44: Computer hardware - a system on a chip

```

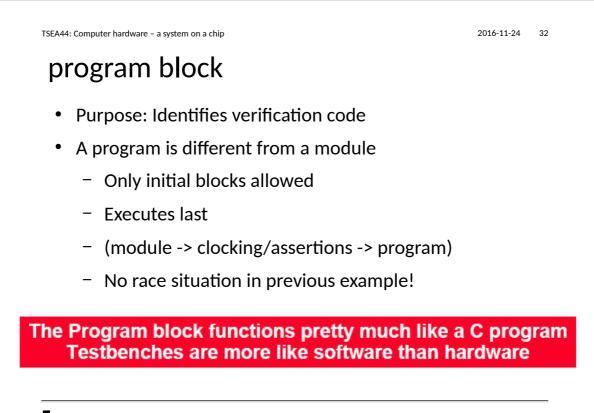

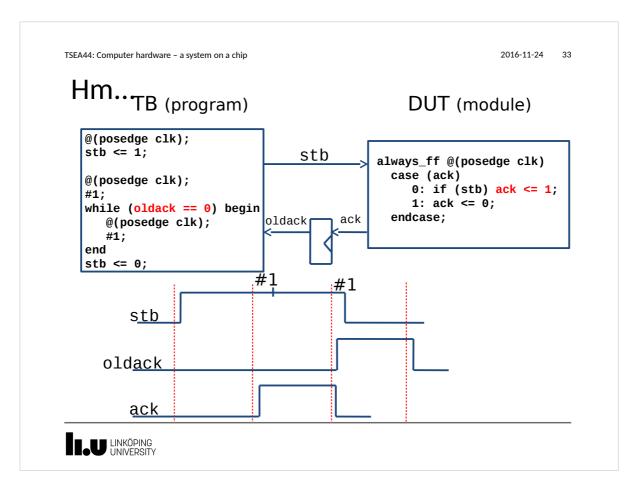

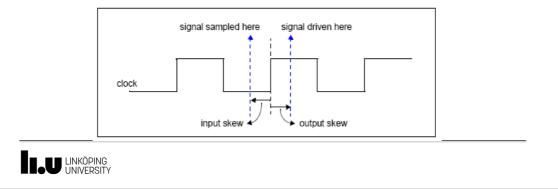

## **Clocking block**

SystemVerilog adds the clocking block that identifies clock signals, and capture the timing and synchronization requirements of the blocks being modeled.

A clocking block assembles signals that are synchronous to a particular clock, and makes their timing explicit.

The clocking block is a key element in cycle-based methodology, which enables users to write testbenches at a higher level of abstraction. Rather than focusing on signals and transitions in time, the test can be defined in terms of cycles and transactions.

#### Possible to simulate setup and hold time

| TSEA44: Computer hardware – a system on a chip                                | 2016-11-24 35                                                                                         |  |  |  |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| Clocking block                                                                |                                                                                                       |  |  |  |

|                                                                               | <pre>module tb();</pre>                                                                               |  |  |  |

| <pre>interface wishbone(input clk,rst);</pre>                                 | logic clk = 1'b0;<br>logic rst = 1'b1;                                                                |  |  |  |

| wire stb,ack;                                                                 | <pre>// instantiate a WB wishbone wb(clk,rst);</pre>                                                  |  |  |  |

| clocking cb @(posedge clk);<br>input ack;<br>output stb;<br>endclocking // cb | <pre>initial begin     #75 rst = 1'b0; end</pre>                                                      |  |  |  |

| modport tb (clocking cb,<br>input clk,rst);                                   | always #20 clk = ~clk;                                                                                |  |  |  |

| endinterface // wishbone                                                      | <pre>// Instantiate the DUT jpeg_top dut(.*);</pre>                                                   |  |  |  |

|                                                                               | <pre>// Instantiate the tester    tester tester0(.*);    mem mem0(.*); endmodule // jpeg_top_tb</pre> |  |  |  |

```

2016-11-24 36

TSEA44: Computer hardware - a system on a chip

Clocking block

program tester(wishbone.tb wb);

module jpeg_top(wishbone wb);

reg state;

....

initial begin

assign wb.ack = state;

for (int i=0; i<3; i++) begin</pre>

wb.cb.stb <= 0;

always_ff @(posedge wb.clk)

##1;

if (wb.rst)

wb.cb.stb <= 1;

state <= 1'b0;</pre>

while (wb.cb.ack==0)

else if(state)

##1;

state <= 1'b0;</pre>

else if (wb.stb)

state <= 1'b1;</pre>

end

end

endprogram // tester

endmodule // jpeg_top

stb

<

ack

```

```

TSEA44: Computer hardware - a system on a chip

```

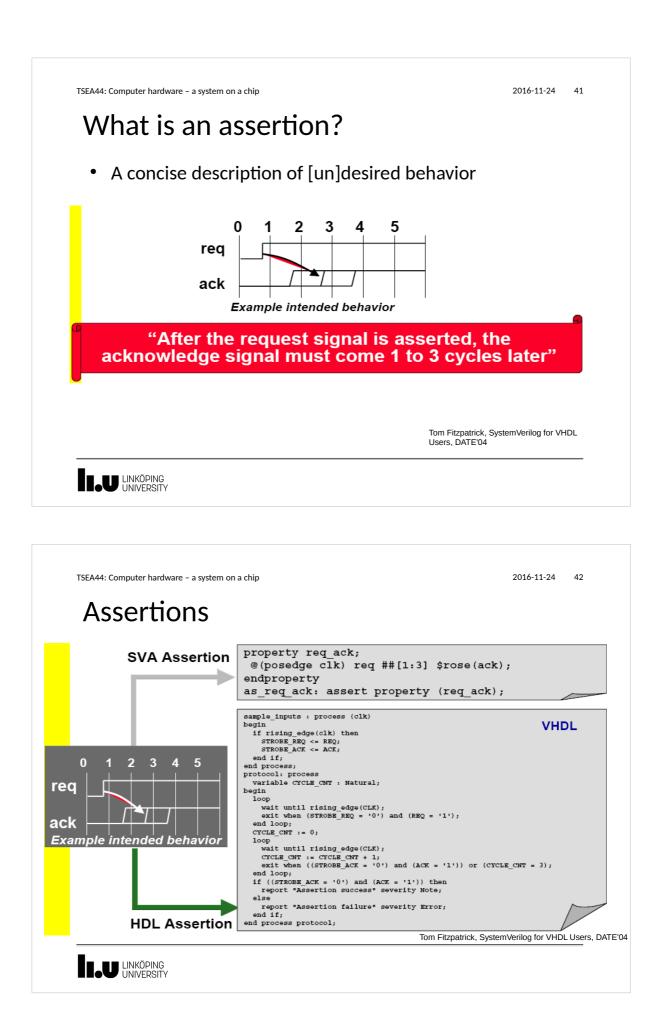

## **Object Oriented Programming**

- SV includes OOP

- Classes can be defined

- Inside a program

- Inside a module

- Stand alone

- assert checks that the property is never violated

- cover tracks all occurrences of property

a1: assert p1 else \$display("grr");

```

property s2a;

@(posedge clk) disable iff (rst)

$rose(stb) |-> ##[0:16] $rose(ack);

endproperty

a_s2a:assert property (s2a) else

$display(" (%0t)(%m) Delayed ack on addr %h",

$time, adr);

```

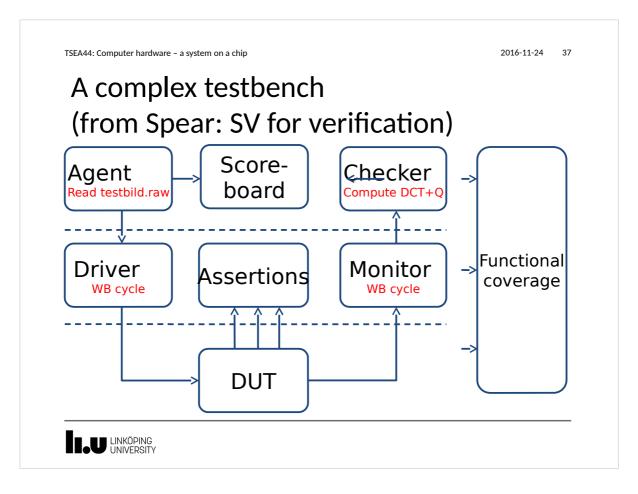

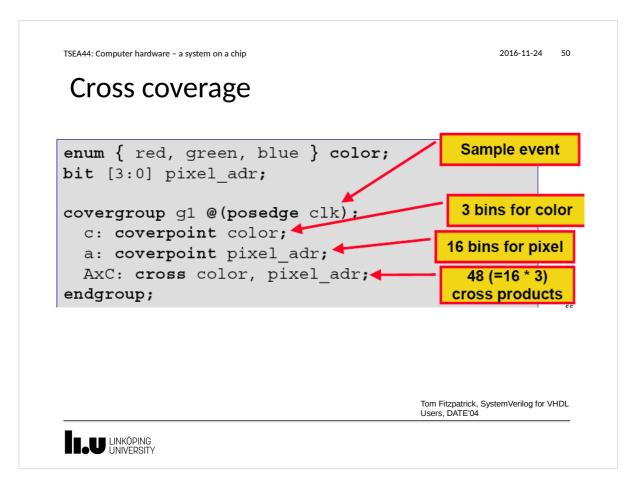

2016-11-24 47 TSEA44: Computer hardware - a system on a chip Coverage Code coverage (code profiling) reflects how thorough the HDL code was exercised Functional Coverage (histogram binning) perceives the design from a user's or a system point of view - Have you covered all of your typical scenarios? - Error cases? Corner cases? Protocols? Functional coverage also allows relationships. ٠ "OK, I've covered every state in my state machine, but did I ever have an interrupt at the same time? When the input buffer was full, did I have all types of packets injected? Did I ever inject two errorneous packets in a row?"

TSEA44: Computer hardware - a system on a chip 2016-11-24 48 memory mem = new(); Coverage // Task to drive values task drive (input [7:0] a, input [7:0] d, input r); DUT With Coverage #5 en <= 1; module simple\_coverage(); addr <= a; <= r; rw logic [7:0] addr; data <= d; logic [7:0] data; par <= ^d; logic par; \$display ("@%2tns Address :%d data %x, logic rw: rw %x, parity %x", logic en; \$time,a,d,r, ^d); #5 en <= 0; // Coverage Group rw <= 0; covergroup memory @ (posedge en); data <= 0; address : coverpoint addr { par <= 0; addr <= 0; bins low = {0,50}; bins med = {51,150}; bins high = {151,255}; <= 0; rw endtask parity : coverpoint par { // Testvector generation bins even = {0}; initial begin bins odd = {1}; en = 0; repeat (10) begin read\_write : coverpoint rw {

bins read = {0}; drive (\$random,\$random,\$random); end bins write = {1}; #10 \$finish; } end endgroup endmodule

| Report                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <pre># @ 5ns Address : 36 data 81, rw 1, pari # @15ns Address : 99 data 0d, rw 1, pari # @25ns Address :101 data 12, rw 1, pari # @35ns Address : 13 data 76, rw 1, pari # @45ns Address :237 data 8c, rw 1, pari # @COVERGBOUD COVERAGE5, rw 0, pari # @COVERGBOUD COVERAGE5, rw 0, pari # @COVERGBOUD COVERAGE5, rw 0, pari # @COVERGE0.</pre> | ModelSim sa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ays:                 |

| # @ <del>65ns Address :229 data 77; rw 0, par</del><br># @ <b>Covergroup</b> ss :143 data f2, rw 0, par                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

| TYPE /simple_coverage/memory<br>Coverpoint memory::address<br>covered/total bins:<br>bin low<br>bin med<br>bin high<br>Coverpoint memory::parity<br>covered/total bins:<br>bin even<br>bin odd<br>Coverpoint memory::read_write<br>covered/total bins:<br>bin read<br>bin write<br>TOTAL COVERGROUP COVERAGE: 44.                                | 44.4% 100 Uncovered<br>33.3% 100 Uncovered<br>1 3<br>9 1 Covered<br>0 1 ZERO<br>0 1 ZERO<br>50.0% 100 Uncovered<br>1 2<br>9 1 Covered<br>0 1 ZERO | Report<br>generator: |

```

TSEA44: Computer hardware - a system on a chip

2016-11-24

52

Constrained randomization

program rc;

class Bus;

rand bit[31:0] addr;

rand bit[31:0] data;

constraint word_align {addr[1:0] == 2'b0;

addr[31:24] == 8'h99;}

endclass // Bus

initial begin

Bus bus = new;

repeat (50) begin

if ( bus.randomize() == 1 )

else

$display ("Randomization failed.\n");

end

end

endprogram // rc

```