# **EXERCISE COLLECTION FOR TSEA26** Design of Embedded DSP Processors

# Version 1.5.3

# ANDREAS EHLIAR

with contributions from Oscar Gustafsson and Frans Skarman

# Contents

| 0        | Abo            | out the Exercises                                                                                                                             | 9  |

|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|          | 0.1            | Notes About the C/Pseudo Code in the Exercises                                                                                                | 9  |

|          | 0.2            | On the Use of RTL Code                                                                                                                        | 10 |

|          |                | 0.2.1 Syntax                                                                                                                                  | 10 |

|          |                | 0.2.2 Hardware Multiplexing                                                                                                                   | 11 |

|          |                | 0.2.3 Clocked structures in HDL                                                                                                               | 12 |

| 1        | Intr           | oductory Exercises                                                                                                                            | 13 |

|          | 1.1            | (easy)                                                                                                                                        | 13 |

|          | 1.2            | (intermediate)                                                                                                                                | 13 |

|          | 1.3            | (intermediate)                                                                                                                                | 13 |

| <b>2</b> | $\mathbf{Exe}$ | rcises for Arithmetic and Logic Unit (ALU)                                                                                                    | 15 |

|          | 2.1            | (easy)                                                                                                                                        | 15 |

|          | 2.2            | (easy)                                                                                                                                        | 15 |

|          | 2.3            | (intermediate)                                                                                                                                | 16 |

|          | 2.4            | $(challenging) \ldots \ldots$ | 17 |

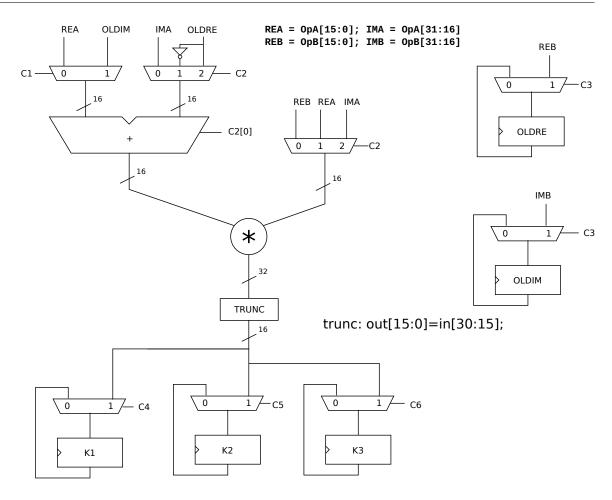

| 3        | $\mathbf{Exe}$ | crcises for Multiply-and-Accumulate (MAC) Unit                                                                                                | 19 |

|          | 3.1            | (easy)                                                                                                                                        | 19 |

|          | 3.2            | (intermediate)                                                                                                                                | 20 |

|          | 3.3            | $(\mathrm{intermediate}) \ \ldots \ $                                 | 21 |

|          | 3.4            | (easy)                                                                                                                                                | 23 |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          | 3.5            | (challenging)                                                                                                                                         | 23 |

|          | 3.6            | (intermediate)                                                                                                                                        | 23 |

|          | 3.7            | $(challenging) \ldots \ldots$  | 25 |

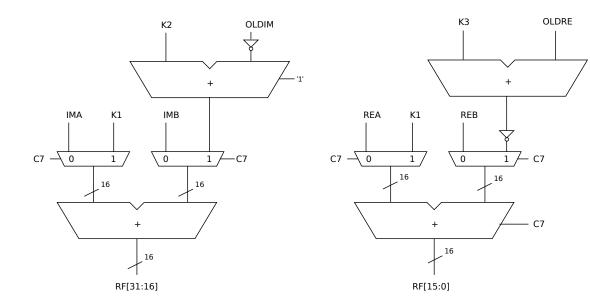

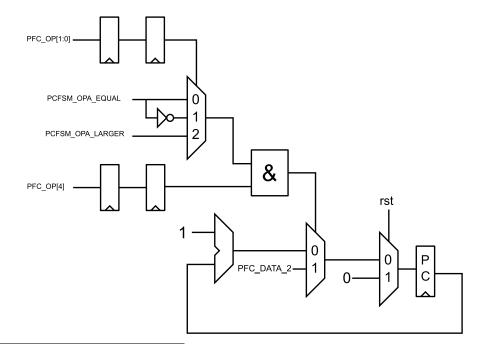

| 4        | Exe            | rcises for Program Flow Control (PFC) Unit                                                                                                            | 27 |

|          | 4.1            | (intermediate)                                                                                                                                        | 27 |

|          | 4.2            | $(challenging) \ldots \ldots$         | 29 |

|          | 4.3            | (easy)                                                                                                                                                | 30 |

|          | 4.4            | $(intermediate) \ldots \ldots$ | 31 |

| <b>5</b> | Exe            | rcises for Address Generation Unit (AGU)                                                                                                              | 33 |

|          | 5.1            | (easy)                                                                                                                                                | 33 |

|          | 5.2            | (intermediate)                                                                                                                                        | 34 |

|          | 5.3            | (intermediate)                                                                                                                                        | 36 |

|          | 5.4            | $(challenging) \dots \dots$                     | 37 |

| 6        | Exe            | rcises for Accelerated Custom Instructions                                                                                                            | 39 |

|          | 6.1            | (intermediate)                                                                                                                                        | 39 |

|          | 6.2            | $(intermediate) \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                                               | 40 |

|          | 6.3            | $(intermediate) \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                                               | 42 |

| 7        | $\mathbf{Des}$ | ign Challenge: Design a DSP Processor                                                                                                                 | 43 |

|          | 7.1            | Approach 1: Solving the entire exercise as it is written                                                                                              | 43 |

|          | 7.2            | Approach 2: Complete assembler-implementation, incomplete hardware                                                                                    | 43 |

|          | 7.3            | Approach 3: Incomplete assembler-implementation, incomplete hardware .                                                                                | 43 |

|          | 7.4            | Approach 4: Same as approach 3 but with a simplified pipeline                                                                                         | 44 |

|          | 7.5            | The task                                                                                                                                              | 44 |

|          | 7.6            | Instruction format                                                                                                                                    | 46 |

|    | 7.7  | Constraints                                                                                                                | 46         |

|----|------|----------------------------------------------------------------------------------------------------------------------------|------------|

|    | 7.8  | Hints                                                                                                                      | 46         |

|    | 7.9  | Our computation kernels                                                                                                    | 17         |

|    |      | 7.9.1 Function 1: sanitize_buffer_values()                                                                                 | 17         |

|    |      | 7.9.2 Function 2: butterfly() $\ldots \ldots 4$             | 48         |

|    |      | 7.9.3 Function 3: fir()                                                                                                    | 49         |

|    |      | 7.9.4 Function 4: getbits() $\ldots \ldots $  | 50         |

|    |      | 7.9.5 Function 5: preprocess() $\ldots \ldots $      | 50         |

|    |      | 7.9.6 Function 6: prepare_data() $\ldots \ldots $           | 51         |

|    |      | 7.9.7 Function 7: dot16()                                                                                                  | 52         |

|    |      | 7.9.8 Function 8: find_val() $\ldots \ldots $ | 53         |

| 8  | Solu | tions Proposals for the Introductory Exercises 5                                                                           | 55         |

| U  | 1.1  |                                                                                                                            |            |

|    | 1.1  |                                                                                                                            | 55         |

|    | 1.2  |                                                                                                                            |            |

|    | 1.5  |                                                                                                                            | )0         |

| 9  | ALU  | U Solution Proposals 6                                                                                                     | 61         |

|    | 2.1  |                                                                                                                            | 62         |

|    | 2.2  |                                                                                                                            | 63         |

|    | 2.3  |                                                                                                                            | 64         |

|    | 2.4  | · · · · · · · · · · · · · · · · · · ·                                                                                      | 67         |

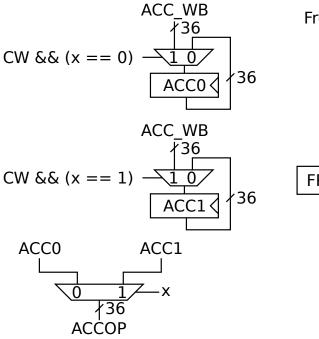

| 10 | МА   | C Unit Solution Proposals 6                                                                                                | <b>6</b> 9 |

| 10 |      | -                                                                                                                          | -          |

|    | 3.1  |                                                                                                                            | 59<br>70   |

|    | 3.2  |                                                                                                                            | 70<br>     |

|    | 3.3  |                                                                                                                            | 72         |

|    | 3.4  |                                                                                                                            | 74         |

|                                                                                    | 3.5                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74                                                                                                                                         |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Ę                                                                                  | 3.6                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77                                                                                                                                         |

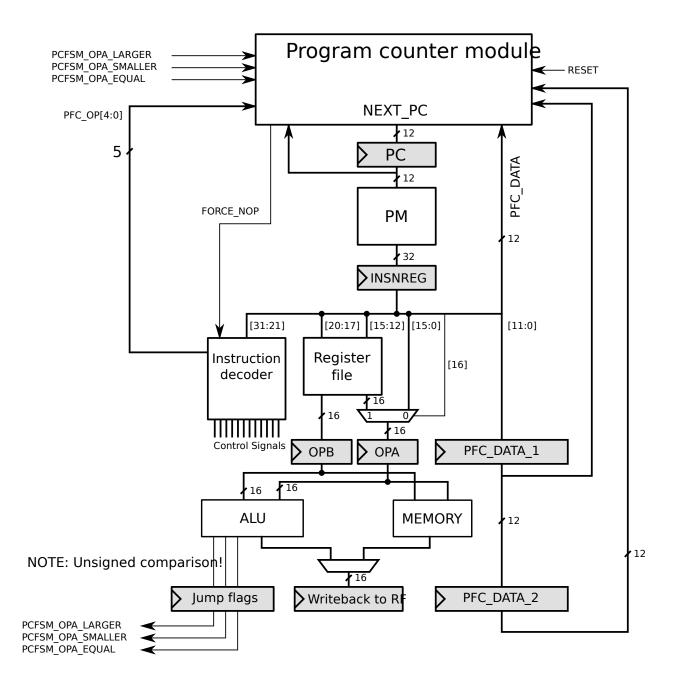

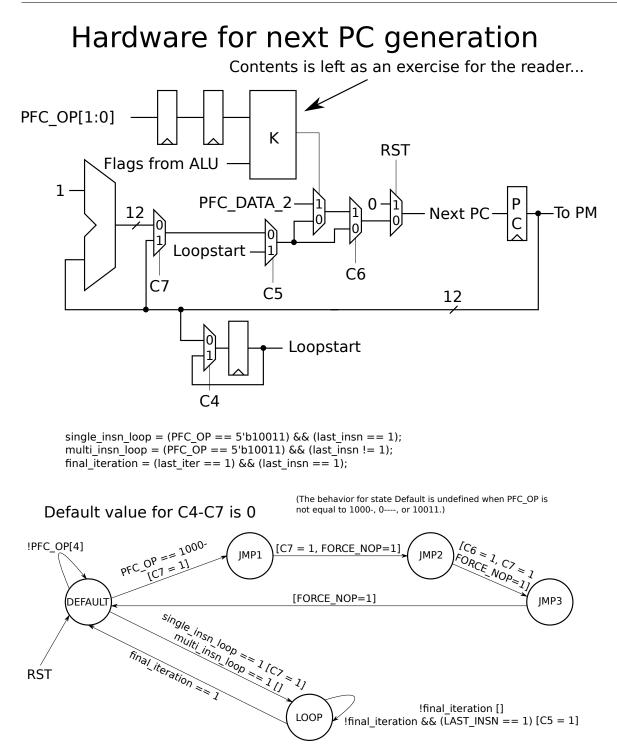

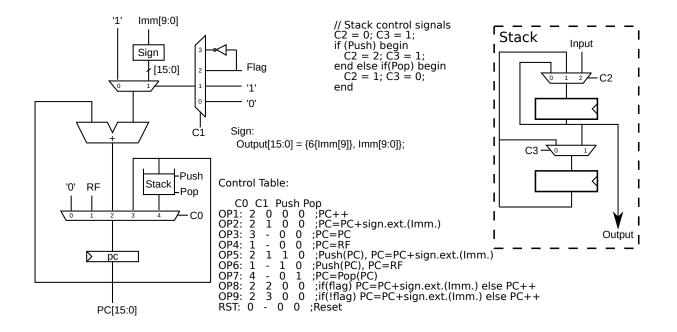

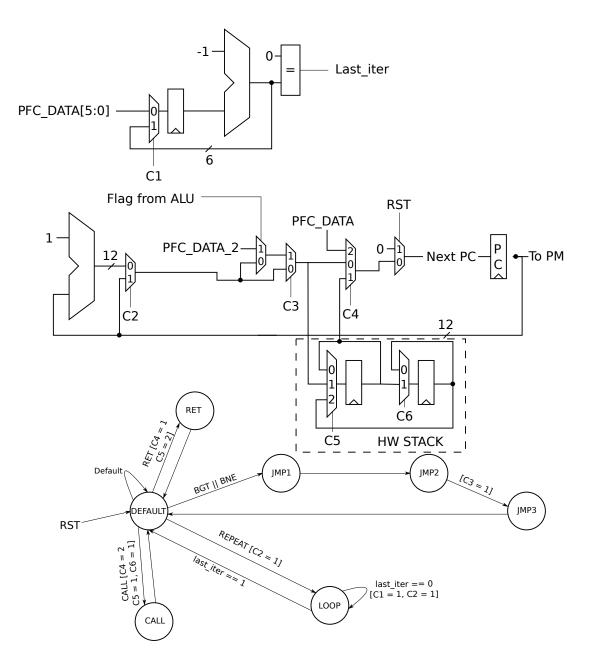

| 11 I                                                                               | PFC                                                               | Unit Solution Proposals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81                                                                                                                                         |

| 4                                                                                  | 1.1                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81                                                                                                                                         |

| 4                                                                                  | 1.2                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83                                                                                                                                         |

| 4                                                                                  | 1.3                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87                                                                                                                                         |

| 4                                                                                  | 1.4                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87                                                                                                                                         |

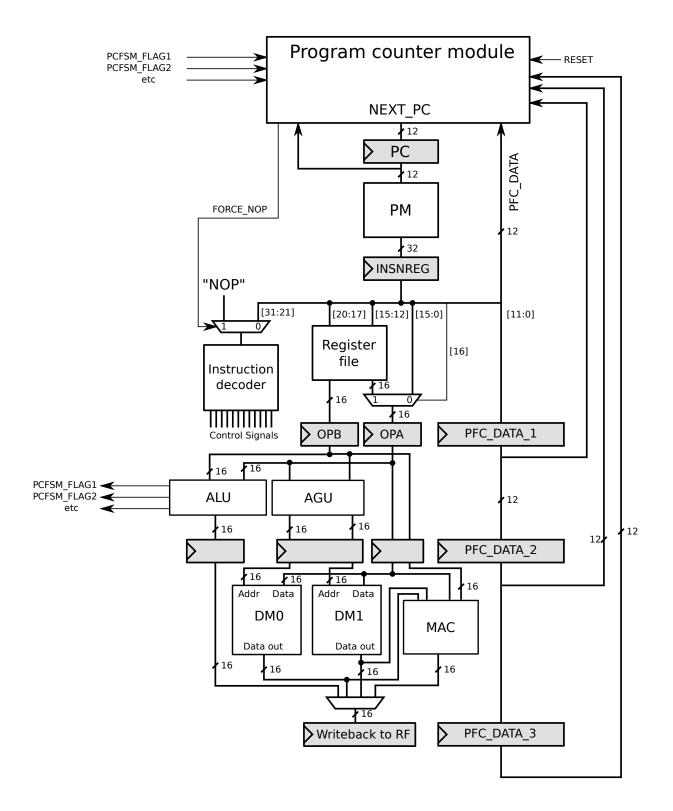

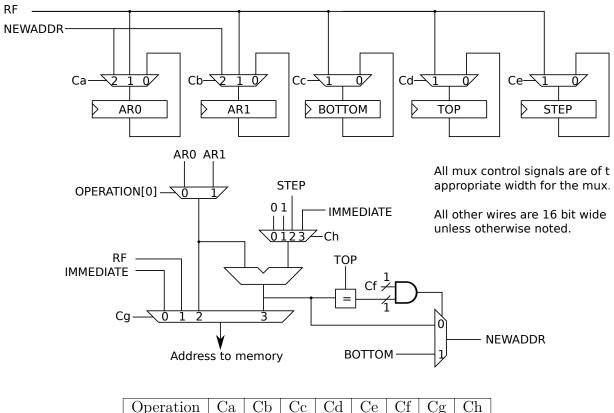

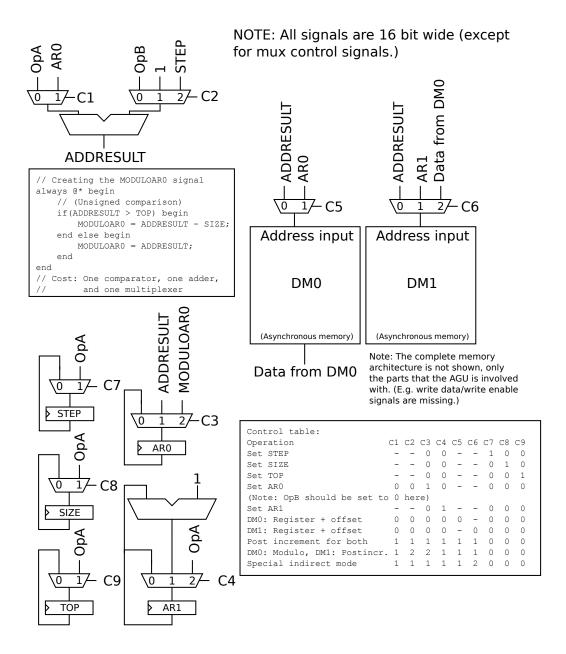

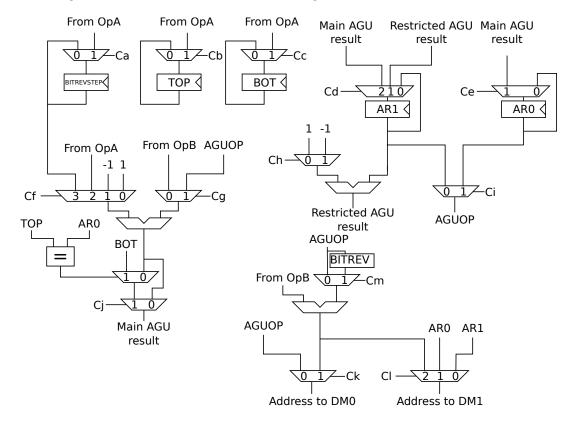

| 12 /                                                                               | AGU                                                               | U Solution Proposals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 93                                                                                                                                         |

| Ę                                                                                  | 5.1                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 93                                                                                                                                         |

| Ę                                                                                  | 5.2                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 94                                                                                                                                         |

| Ę                                                                                  | 5.3                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 95                                                                                                                                         |

| Ę                                                                                  | 5.4                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 97                                                                                                                                         |

|                                                                                    |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                            |

| 13 4                                                                               | Acce                                                              | elerated Instructions Solution Proposals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 99                                                                                                                                         |

|                                                                                    | <b>Acce</b><br>5.1                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>99</b><br>99                                                                                                                            |

| 6                                                                                  |                                                                   | -<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                            |

| 6                                                                                  | 3.1<br>3.2                                                        | -<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99<br>102                                                                                                                                  |

| 6                                                                                  | 5.1<br>5.2<br>5.3                                                 | -<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99<br>102                                                                                                                                  |

| 6<br>6<br>14 S                                                                     | 5.1<br>5.2<br>5.3<br><b>Solu</b>                                  | -<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99<br>102<br>103<br>05                                                                                                                     |

| 6<br>6<br>14 \$<br>1                                                               | 5.1<br>5.2<br>5.3<br><b>Solu</b><br>14.1                          | tion Proposal for the Design Challenge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul><li>99</li><li>102</li><li>103</li><li>05</li><li>105</li></ul>                                                                        |

| 6<br>6<br>14 \$<br>1                                                               | 5.1<br>5.2<br>5.3<br><b>Solu</b><br>14.1                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>99</li> <li>102</li> <li>103</li> <li>05</li> <li>105</li> <li>105</li> </ul>                                                     |

| 6<br>6<br>14 \$<br>1                                                               | 5.1<br>5.2<br>5.3<br>5 <b>01u</b><br>14.1                         | Image: Antion Proposal for the Design Challenge       1         Image: Correction checklist       1         A Note on the Proposed Solutions       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>99</li> <li>102</li> <li>103</li> <li>05</li> <li>105</li> <li>105</li> <li>106</li> </ul>                                        |

| 6<br>6<br>14<br>1<br>1<br>1                                                        | 5.1<br>5.2<br>5.3<br>5 <b>01u</b><br>14.1<br>14.2                 | Image: The second se | <ul> <li>99</li> <li>102</li> <li>103</li> <li>05</li> <li>105</li> <li>106</li> <li>106</li> </ul>                                        |

| 6<br>6<br>14 \$<br>1<br>1<br>1                                                     | 5.1<br>5.2<br>5.3<br>5 <b>01u</b><br>14.1<br>14.2                 | Image: Antion Proposal for the Design Challenge       1         Image: Antion Proposal for the Design Challenge       1         Correction checklist       1         A Note on the Proposed Solutions       1         14.2.1 A note on delay slots       1         Function 1: sanitize_buffer_values       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>99</li> <li>102</li> <li>103</li> <li>05</li> <li>105</li> <li>106</li> <li>106</li> <li>106</li> <li>107</li> </ul>              |

| 6<br>6<br>14<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 5.1<br>5.2<br>5.3<br>5 <b>01u</b><br>14.1<br>14.2<br>14.3<br>14.3 | Ition Proposal for the Design Challenge       1         Correction checklist       1         A Note on the Proposed Solutions       1         14.2.1 A note on delay slots       1         Function 1: sanitize_buffer_values       1         Function 2: butterfly       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>99</li> <li>102</li> <li>103</li> <li>05</li> <li>105</li> <li>106</li> <li>106</li> <li>106</li> <li>107</li> <li>109</li> </ul> |

| 14.8 Function 6: prepare_data() $\ldots \ldots \ldots$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14.9 Function 7: dot16()                                                                                                                                               |

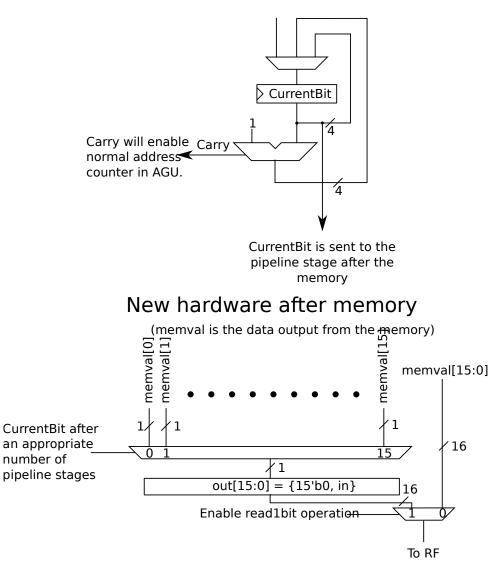

| 14.10Function 8: find_val()                                                                                                                                            |

| 14.11Final instruction list                                                                                                                                            |

| 14.12Required addressing modes                                                                                                                                         |

| 14.13ALU                                                                                                                                                               |

| 14.14PC                                                                                                                                                                |

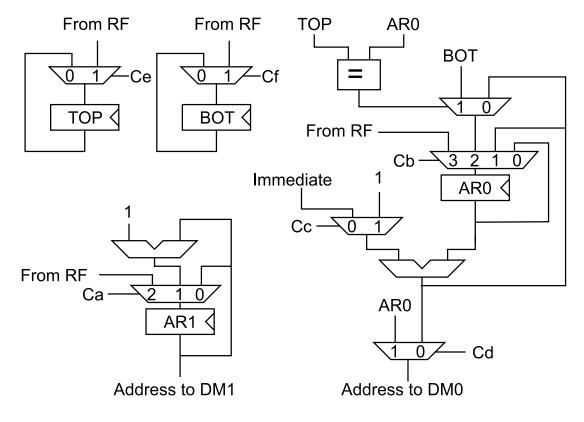

| 14.15AGU                                                                                                                                                               |

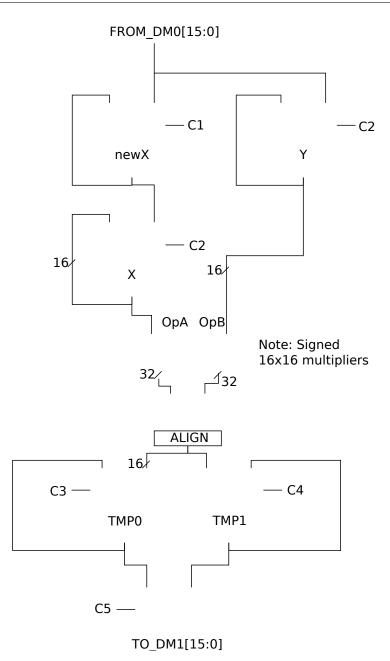

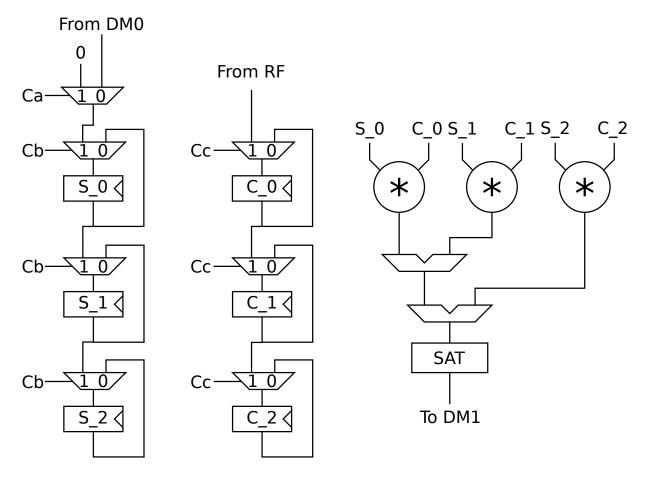

| 14.16MAC                                                                                                                                                               |

|                                                                                                                                                                        |

### 15 Version history

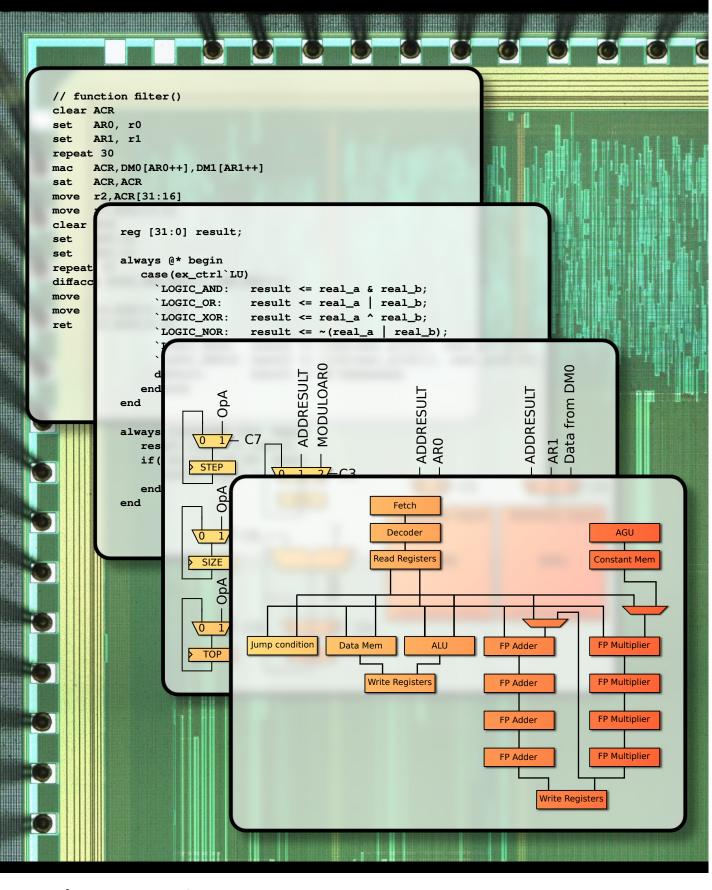

# 0 About the Exercises

The exercises in this book are meant to show fairly realistic situations. While it is seldom feasible to create an exercise which is fully realistic, it has been tried to create exercises which contains situations that you could realistically expect to see in a real ASIP. Or for that matter when designing an accelerator for a certain task in for example an FPGA.

Many of these exercises can be solved in different ways, particularly the intermediate and challenging exercises. In the solution proposals, the aim is to provide a fairly realistic solution proposal. For example, often long critical paths or solutions which would require an awkward datapath pipeline are avoided. The hope is that this will lead to some more interesting solution proposals which will allow you to learn a new trick or two. (However, do not worry too much if you would not come up with these tricks yourself, as you typically do not need to worry about for example the critical path on the exam.)

Feedback on these exercises, particularly any bugs you may have found are very welcome.

### 0.1 Notes About the C/Pseudo Code in the Exercises

C-like pseudo code is used in the exercises in this document. This is hopefully not a problem as the C code is usually kept simple and should be easy to understand for anyone who has taken an introductory course in C or C++. However, datatypes from  $\mathtt{stdint.h}$  are often used, which may not have been covered in such a course:

- int8\_t: 8-bit signed integer

- int16\_t: 16-bit signed integer

- int32\_t: 32-bit signed integer

- uint8\_t: 8-bit unsigned integer

- uint16\_t: 16-bit unsigned integer

- uint32\_t: 32-bit unsigned integer

(In essence, this is a way to guarantee that certain sizes are used, as C does not guarantee that for example a short will always be 16 bits.)

In these exercises it is assumed that two's complement format will be used to store the signed integers although the C standard does not offer such guarantees<sup>1</sup>.

### 0.2 On the Use of RTL Code

Note that RTL code, in the form of Verilog, has been used to explain certain parts of the schematics that would be awkward to draw using schematic symbols.

It is encouraged to do the same while solving these exercises if you think a certain part of the schematic is easier to explain using Verilog or VHDL. However, keep the following in mind if you want to use Verilog/VHDL:

#### 0.2.1 Syntax

When correcting the exam, the correct Verilog/VHDL syntax is in general not crucial. However, there are a few situations where the syntax is quite important. The most common example is the replication operator in Verilog.

If you are unsure about the syntax, please write a comment about what you actually intend to do.

<sup>&</sup>lt;sup>1</sup>Which can lead to disastrous results, see for example http://www.phrack.org/issues.html?issue= 60&id=10#article.

#### 0.2.2 Hardware Multiplexing

If you use Verilog or VHDL you need to write it in such a way that the hardware multiplexing is obvious. For example, the following is a **bad** example of a design since the hardware multiplexing is not obvious:

```

/* Create a simple ALU with add, subtract, xor and or */

reg [31:0] result;

always @(posedge clk) begin : ALU

case(Ca)

0: result = A + B;

1: result = A - B;

2: result = A ^ B;

3: result = A | B;

endcase

end

```

In the example above, it is not clear that the same adder can be used for the addition and subtraction. Although a good synthesis tool will probably detect this, one of the the goals of this course is to show that you understand the details of microarchitecture design (such as hardware multiplexing), instead of relying on the tools to do it for you. While the tools will probably do a good job in many cases, you will see in lab 2 that good knowledge of hardware multiplexing can reduce the area and critical path of a design by allowing you to redesign it in such a way that it is possible to do hardware multiplexing.

In contrast, if you want to create an ALU where hardware multiplexing is obvious, the following would be a better example:

```

reg carry_in;

always @* begin

if(Cb) begin

carry_in = 1;

op_b = B;

end else begin

carry_in = 0;

op_b = ~B;

end

end

always @(posedge clk) begin

case(Cc)

0: result = A + op_b + carry_in;

1: result = A \cap B;

2: result = A \mid B;

endcase

end

```

### 0.2.3 Clocked structures in HDL

Another detail that you need to be careful about is clocking. Historically, many students that use VHDL or Verilog on the exam forget to indicate that a clock is used for registers and flip-flops. So if you want to create a clocked structure (such as a flag register in an ALU) please make sure that you actually indicate that a clock is used (for example by using an always @(posedge clk) statement in Verilog).

# **1** Introductory Exercises

## Exercise 1.1 (easy)

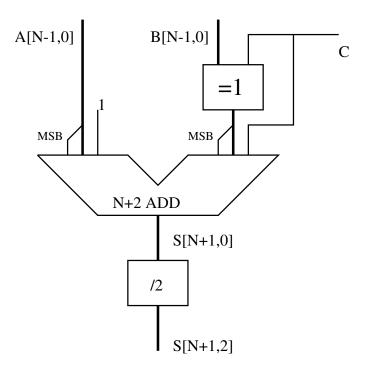

Draw the schematic of a simple computing module which should perform the following tasks, depending on the value of the control signal C:

- C=0: Y = (A + B)/2

- C=1: Y = (A B)/2

No special rounding is needed in this exercise. However, you are only allowed to use one adder.

## Exercise 1.2 (intermediate)

Write efficient assembler code for a DSP processor such as the Senior processor for a 32-tap FIR filter. The FIR filter should operate on a 1000 long vector located in memory 0. (You can assume that this vector begins with 31 zeros and ends with 31 zeros.). The filter coefficients are stored in ROM0.

### Exercise 1.3 (intermediate)

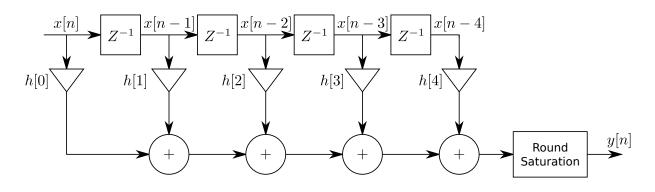

Write efficient assembler code for a DSP processor such as the Senior processor for the following filter structure.

For a 5-tap filter it will be significantly faster to use an unrolled loop and store intermediate values in registers rather than using a ring buffer in memory.

#### CHAPTER 1. INTRODUCTORY EXERCISES

You can assume that the following instruction will handle output and inputs of samples:

| in r0,0x10  | ; | Fetch sample  |

|-------------|---|---------------|

| out 0x11,r0 | ; | Output sample |

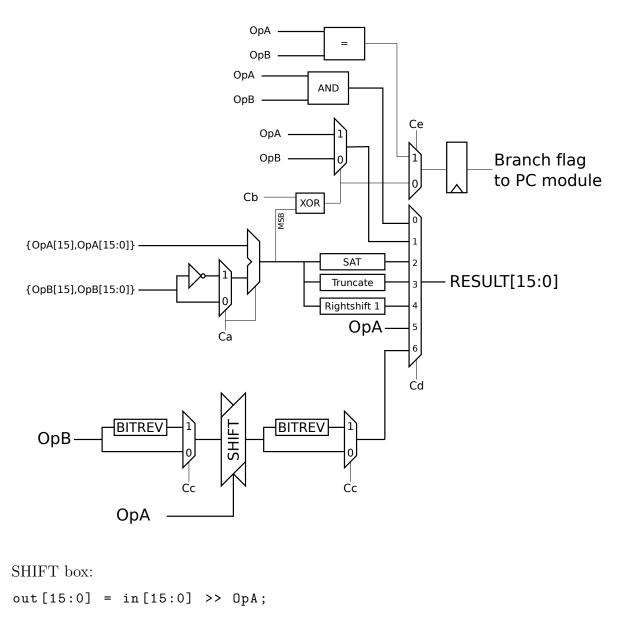

# 2 Exercises for Arithmetic and Logic Unit (ALU)

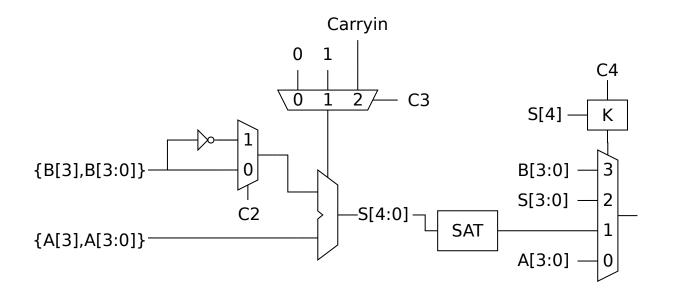

## Exercise 2.1 (easy)

Design an arithmetic unit using minimal HW and implement the following functions. Annotate your design clearly.

- OP1:  $A[3:0] + B[3:0] + Carry_in$

- OP2: Saturate(A[3:0] + B[3:0])

- OP3: Saturate(A[3:0] B[3:0])

- OP4: if  $(A[3:0] \ge B[3:0])$  result  $\Leftarrow A$  else result  $\Leftarrow B$ ;

Clearly specify all the black boxes. Operand A and B are signed numbers.

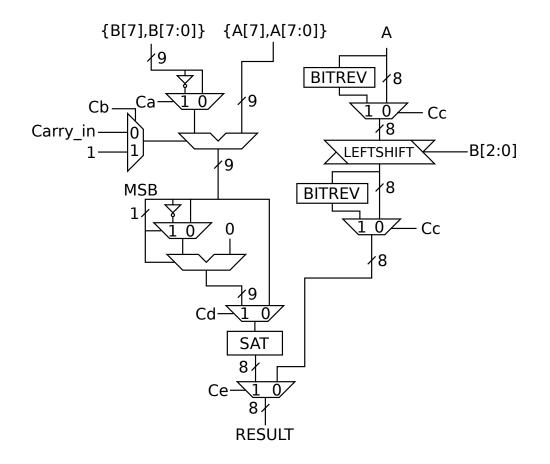

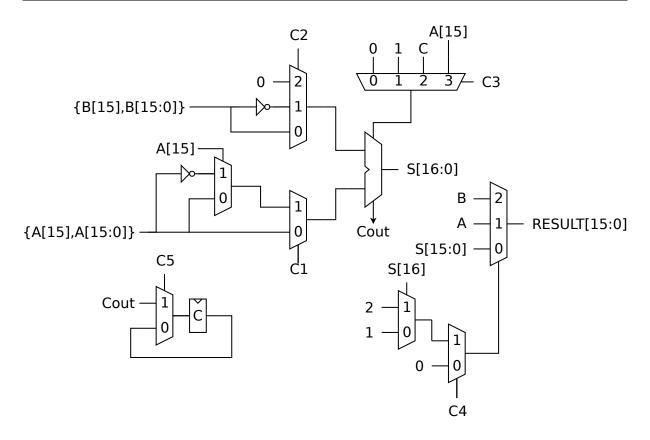

# Exercise 2.2 (easy)

- OP0: RESULT = A + B + Carry\_in

- OP1: RESULT = A B

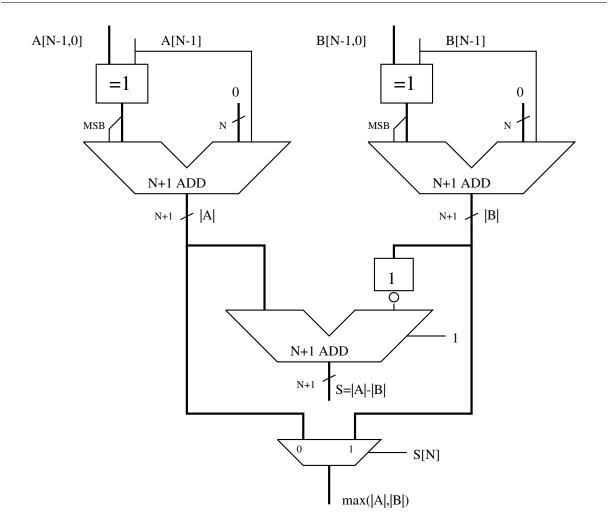

- OP2: RESULT = ABS(B A)

- OP3: RESULT = LEFTSHIFT(A, B[2:0]) (Shift A left by B[2:0] times)

- OP4: RESULT = RIGHTSHIFT(A, B[2:0]) (Shift A right by B[2:0] times (not arithmetic shift))

#### **Constraints:**

Overflow must be handled for ABS(B - A). It is up to you if you want to handle overflow in any other case.

- You should minimize the amount of hardware such as adders and shifters.

- A is 8 bits wide, B is 8 bits wide, Carry\_in is 1 bit wide. RESULT is 8 bits wide.