## **TSTE86** Homework 5: Synchronization

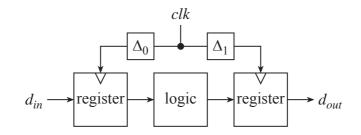

The following times apply to the pipelined datapath shown in Figure 1:

| Clock period                  | $T_{\rm clk}$             | = | 1000 ps |

|-------------------------------|---------------------------|---|---------|

| Register, setup               | <i>t</i> <sub>su</sub>    | = | 150 ps  |

| Register, hold                | <i>t</i> <sub>hold</sub>  | = | 100 ps  |

| Register, max clock-to-output | $t_{c-q}$                 | = | 250 ps  |

| Register, min clock-to-output | $t_{c-q,cd}$              | = | 200 ps  |

| Logic, max propagation        | <i>t</i> <sub>logic</sub> | = | 500 ps  |

| Logic, min propagation        | $t_{\rm logic,cd}$        | = | 450 ps  |

Figure 1. Pipelined datapath with clock delays  $\Delta_0$  and  $\Delta_1$ .

The clock is delayed with  $\Delta_1 = 300$  ps to the right register. What range of delay  $\Delta_0$  is acceptable from the clock to the first register?