TSEI05 ANTIK Kent Palmkvist 6

\*

kentp@isy.liu.se http://www.es.is

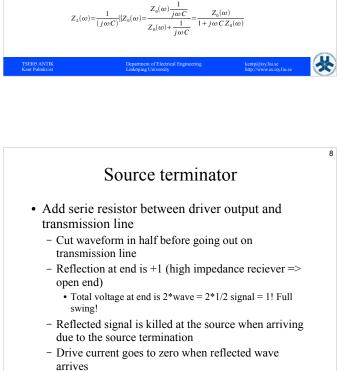

## Comparison end vs source termination

10

×

12

kentp@isy.liu.se http://www.es.is

- Source usually resistive plus small inductance

- End usually capacitive

- Mismatch between Z0 and capacitive load in end termination probably worse than serie resistor mismatch (usually less reflections in source termination)

- Worst case drive current is  $\Delta V/2Z0$ . For end termination with Vcc/2 bias this is also true (voltage swing is only half, but Z0 impedance)

## Accuracy requirements for termination

- Problem knowing both transmission line impedance and resistor value

- Safe choise: source and end termination - Kill reflections in both ends