# Lecture 3, Opamps

#### Operational amplifiers, high-gain, high-speed

## What did we do last time?

#### **Multi-stage amplifiers**

Increases gain

Increases number of poles

#### **Frequency domain**

Stability

Phase margin

LIU EXPANDING REALITY

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

## What will we do today?

#### Wrap-up the discussion on compensation and stability

Two-stage amplifiers

Three compensation methods

#### **Operational amplifiers**

Characteristics

Operation

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

87 of 252

# The problem: Stability, cont'd

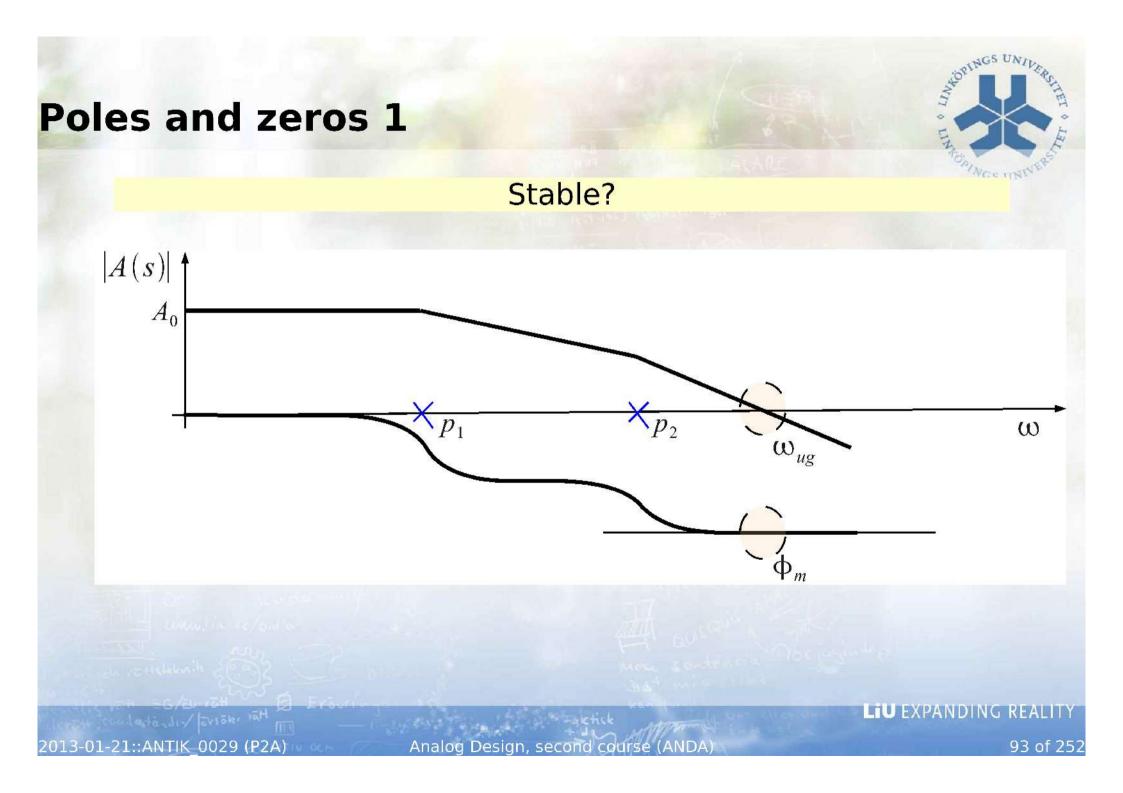

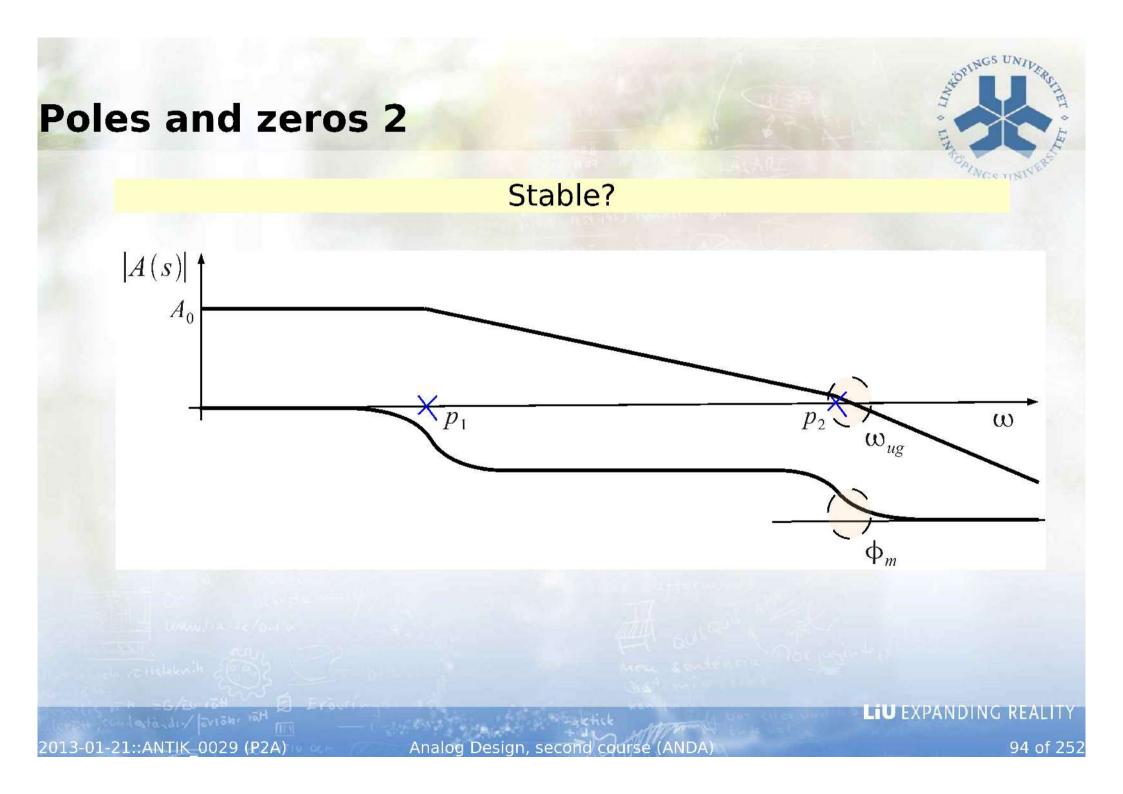

#### **Bode plot**

What happens to the transfer characteristics?

Phase margin

Feedback factor

#### **Step response**

Settling

Oscillations

#### Critically damped at 70 degrees

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

## We need to be a bit more systematic

# ST COMMENSURINGS UNIVERSITY OF LANDONINGS UNIVERSITY

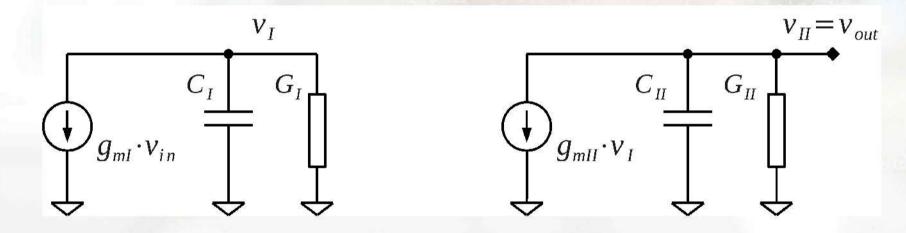

#### One model (high-impedance load) and focus on two-pole

$$p_1 = \frac{G_I}{C_I}, p_2 = \frac{G_{II}}{C_{II}}, A_1 = \frac{g_{mI}}{G_I}, A_2 = \frac{g_{mII}}{G_{II}}$$

LIU EXPANDING REALITY

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

## **Dominant pole assumption (output)**

Assuming pole splitting,  $p_2 \gg p_1$ , gives us

$$A(s) = \frac{A_1 \cdot A_2}{\left|1 + \frac{s}{p_{11}}\right| \cdot \left|1 + \frac{s}{p_{12}}\right|} \approx \frac{A_1 \cdot A_2}{1 + \frac{s}{p_1} + \frac{s^2}{p_1 \cdot p_2}}$$

This implies:  $\omega_{ug} \approx A_1 \cdot A_2 \cdot p_1$  and

2013-01-21::ANTIK\_0029 (P2A)

$$\Phi_{m} = 180 - \arg A(j \omega_{ug}) = 180 - \operatorname{atan} \frac{\omega_{ug}}{p_{1}} - \operatorname{atan} \frac{\omega_{ug}}{p_{2}} \approx 90 - \operatorname{atan} \frac{\omega_{ug}}{p_{2}}$$

$$\Phi_{m} \approx 90 - \operatorname{atan} \left| A_{0} \cdot \frac{p_{1}}{p_{2}} \right|$$

LIU EXPANDING REALITY

Analog Design, second course (ANDA)

## The formulas (dominant load!)

**Unity-gain frequency**

$$\omega_{ug} \approx \frac{g_{mI} \cdot g_{mII}}{G_I \cdot G_{II}} \cdot \frac{G_{II}}{C_{II}} = \frac{g_{mI} \cdot g_{mII}}{G_I \cdot C_{II}}$$

**Phase margin**

$$\phi_{m} \approx 90 - atan \frac{\omega_{ug}}{p_{2}} = 90 - atan \frac{\frac{g_{mI} \cdot g_{mII}}{G_{I} \cdot C_{II}}}{\frac{G_{I}}{C_{I}}} = 90 - atan \frac{g_{mI} \cdot g_{mII} \cdot C_{I}}{G_{I}^{2} \cdot C_{II}}$$

etc., etc., etc. -- We need to be a bit more organized...

2013-01-21::ANTIK 0029 (P2A)

Analog Design, second course (ANDA)

91 of 252

Analog Design, second course (ANDA

2013-01-21::ANTIK\_0029 (P2A)

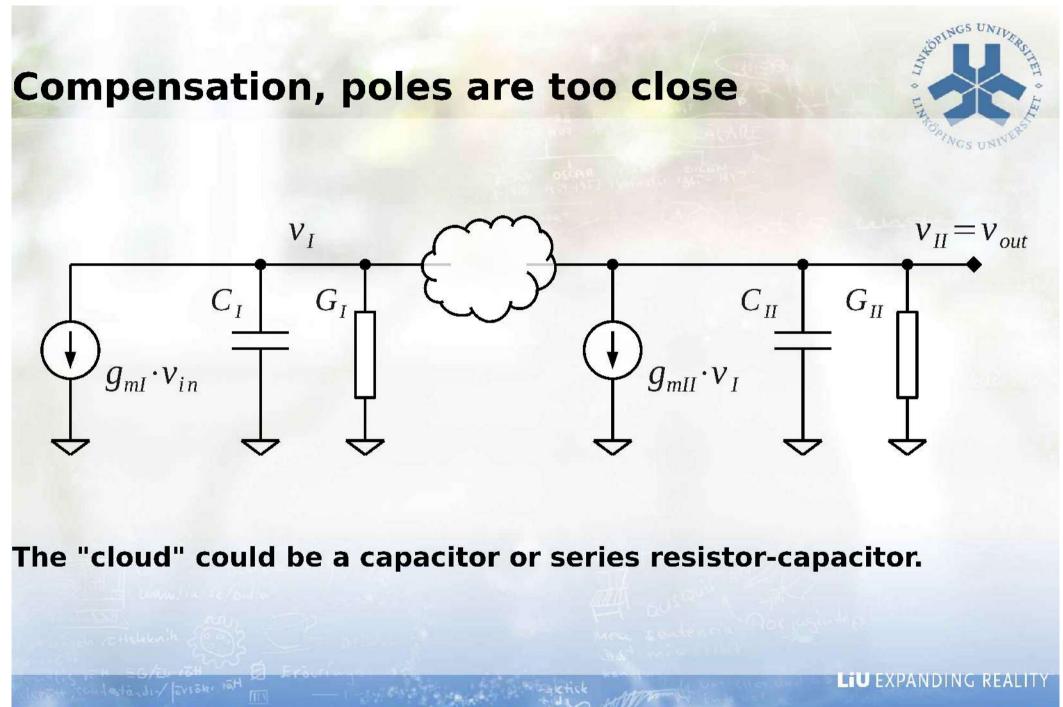

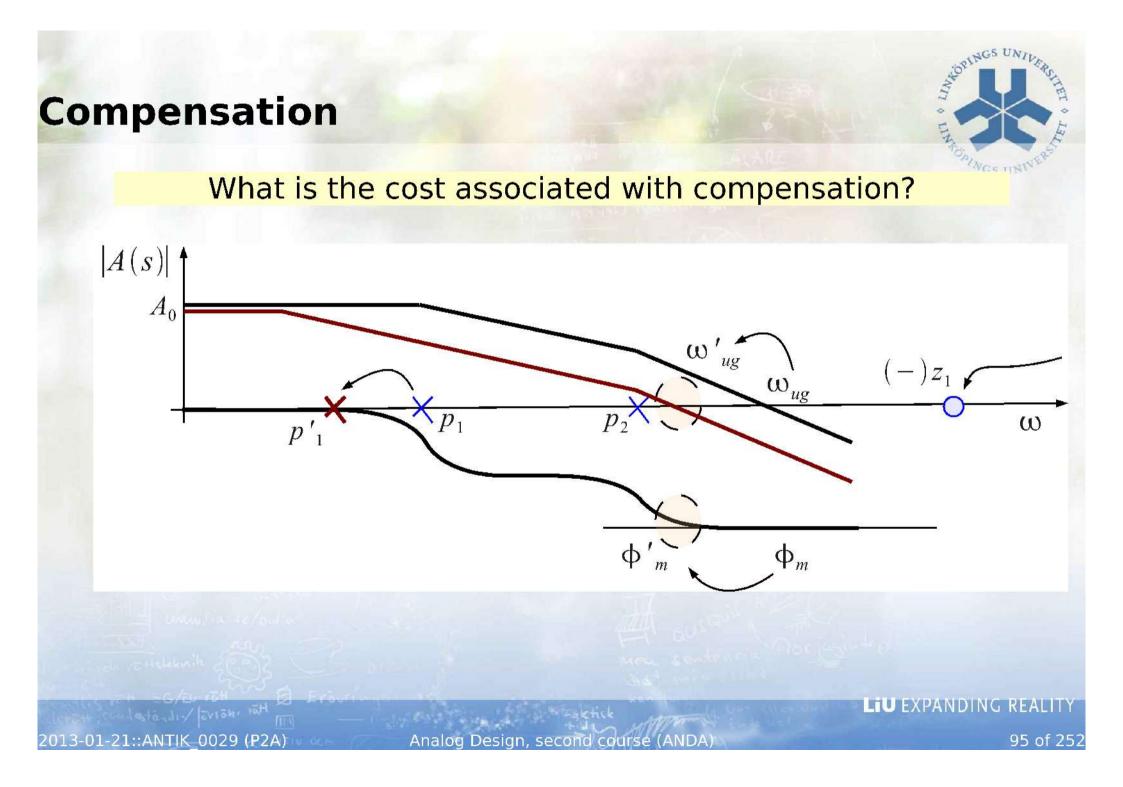

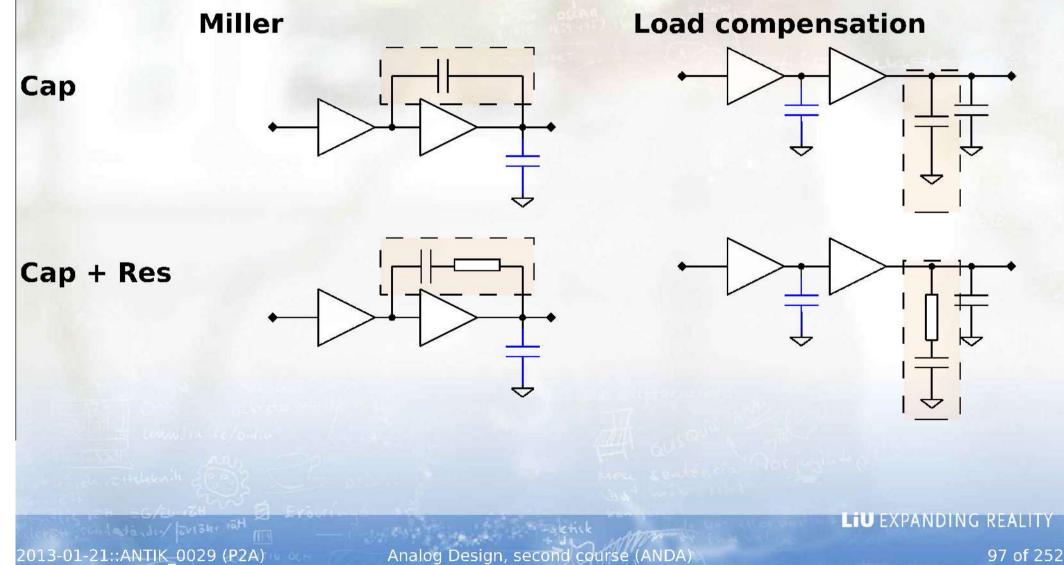

## **Compensation, two cases:**

#### 1) "Internal" node sees a low-impedance node

Typically: output load dominates, drive a capacitive load

Load-compensation, i.e., increase cap externally

#### 2) "Internal" node sees a high-impedance node

Typically: internal load dominates, drive a resistive load

Miller-compensation, i.e., utilize the second-stage gain to multiply  $C_c$

Design, second course

#### As always, some exceptions to the rule:

Nested compensation, active compensation, ... and more ...

# **Compensation compiled:**

# **Compensation, Miller capacitance**

| Introduced zero             | Parasitic pole                  | Dominant pole                                       | Unity-gain                         |

|-----------------------------|---------------------------------|-----------------------------------------------------|------------------------------------|

| $z_1 = \frac{g_{mII}}{C_C}$ | $p_2 = \frac{-g_{mII}}{C_{II}}$ | $p_1 = \frac{-G_I \cdot G_{II}}{g_{mII} \cdot C_C}$ | $\omega_{ug} = \frac{g_{mI}}{C_C}$ |

| Introduced zero                    | Parasitic pole                      | Phase margin |  |

|------------------------------------|-------------------------------------|--------------|--|

| $z_1 \approx 10 \cdot \omega_{ug}$ | $p_2 \approx 2.2 \cdot \omega_{ug}$ | ≈60          |  |

Dominant pole moves "down", parasitic pole moves "up"

Parasitic zero added (harmful for phase margin)

LIU EXPANDING REALITY

Analog Design, second course (ANDA)

# **Compensation, Nulling resistor 1**

| Introduced zero                                                   | Parasitic poles                                                           | <b>Dominant pole</b> Unity-gain                                                                                                                                                          |

|-------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $z_1 = \frac{g_{mII}}{C_C} \cdot \frac{1}{1 - R_Z \cdot g_{mII}}$ | $p_2 = \frac{-g_{mII}}{C_{II}}, p_3 = \frac{-1}{R_Z \cdot C_{II}}$        | $p_1 = \frac{-G_I \cdot G_{II}}{g_{mII} \cdot C_C} \qquad \qquad$ |

|                                                                   | $R_{Z} = \frac{1}{g_{mII}} \cdot \left  1 + \frac{C_{II}}{C_{C}} \right $ |                                                                                                                                                                                          |

|                                                                   |                                                                           |                                                                                                                                                                                          |

| Introduced zero                                                   | Parasitic pole                                                            | Phase margin                                                                                                                                                                             |

| $z_1 \rightarrow p_2$                                             | $p_3 \approx 1.73 \cdot \omega_{ug}$                                      | ≈60                                                                                                                                                                                      |

|                                                                   |                                                                           |                                                                                                                                                                                          |

|                                                                   |                                                                           |                                                                                                                                                                                          |

| Levent coulestander / Eviater ralt                                | Erouting active active me                                                 | LIU EXPANDING REALITY                                                                                                                                                                    |

| 2013-01-21::ANTIK_0029 (P2A)                                      | Analog Design, second course (                                            | ANDA) 99 of 252                                                                                                                                                                          |

# **Compensation, Nulling resistor 2**

| Introduced zero                                                   | Parasitic poles                                                                      | Dominant pole Unity-gain                                                                                                                                                                 |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $z_1 = \frac{g_{mII}}{C_C} \cdot \frac{1}{1 - R_Z \cdot g_{mII}}$ | $p_2 = \frac{-g_{mII}}{C_{II}}, p_3 = \frac{-1}{R_Z \cdot C_{II}}$                   | $p_1 = \frac{-G_I \cdot G_{II}}{g_{mII} \cdot C_C} \qquad \qquad$ |

|                                                                   | $R_z = \frac{1}{g_{mII}}$                                                            |                                                                                                                                                                                          |

|                                                                   |                                                                                      |                                                                                                                                                                                          |

|                                                                   |                                                                                      |                                                                                                                                                                                          |

| Introduced zero                                                   | Parasitic pole                                                                       | Phase margin                                                                                                                                                                             |

| Introduced zero<br>$z_1 \rightarrow \infty$                       | Parasitic pole<br>$p_2 \approx 1.73 \cdot \omega_{ug}, \ p_3 > 10 \cdot \omega_{ug}$ | Phase margin<br>≈60                                                                                                                                                                      |

|                                                                   |                                                                                      |                                                                                                                                                                                          |

| $z_1 \rightarrow \infty$                                          |                                                                                      |                                                                                                                                                                                          |

| $z_1 \rightarrow \infty$                                          |                                                                                      |                                                                                                                                                                                          |

**Rule-of-thumbs for hand-calculation**

17 . HA COMMERCIAL

Use e.g. MATLAB to support calculations for understanding

/site/edu/es/ANTIK/antikLab/m/antikPoleZero.m

/site/edu/es/ANTIK/antikLab/m/antikSettling.m

In the end, use the simulator.

It has to be robust over temperature and other variations.

Analog Design, second course (AND)

Hand calculations are incorrect per definition

Model corresponds quite well with circuit once you have identified the different stages

See for example exercises

-01-21::ANTIK\_0029 (P2A

LIU EXPANDING REALITY

## **Operational amplifiers**

#### **Operational amplifiers (OP)**

drive resistive loads

have zero output impedance, zero input impedance, infinite gain

act like a voltage source

#### **Operational transconductance amplifiers (OTA)**

drive capacitive loads

have infinite output impedance, zero input impedance, infinite gain

Analog Design, second course

act like a current source

-21::ANTIK-0029 (P2A

LIU EXPANDING REALITY

LIU EXPANDING REALITY

103 of 252

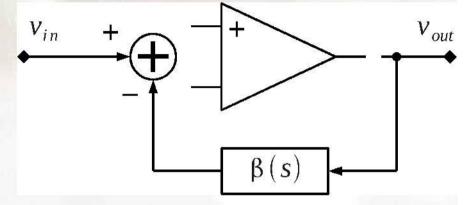

# Why do you want controlled feedback?

#### Gain is now under control!

No variation with gm/gds, instead it is given by passive components

#### "Unlimited" drive capability

Isolation of input and output

#### **Linearization**

...ANTIK\_0029

Remember, it is a regulation loop. It is designed to track the changes, anything added in the loop will be supressed.

Design, second course

## **Practical concerns**

#### Limited gain

Open-loop gain vs. closed-loop gain

#### Bandwidth

Speed

2013-01-21::ANTIK 0029 (P2A)

#### **Offset error**

Mismatch will cause an offset - how do we handle this?

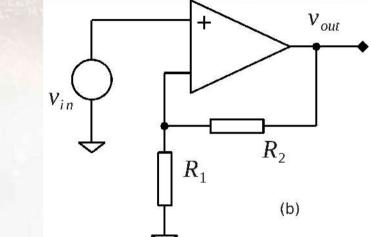

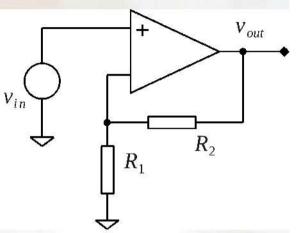

# **Limited gain**

$$\frac{R_1}{R_1 + R_2} \cdot v_{out} = v_{in} \Rightarrow \frac{v_{out}}{v_{in}} = \frac{R_1 + R_2}{R_1} = \Gamma$$

#### Non-ideal gain case:

$$\begin{aligned} v_{out} &= A_0 \cdot \left[ v_{in} - \frac{R_1}{R_1 + R_2} \cdot v_{out} \right] \Rightarrow \frac{v_{out}}{v_{in}} = \frac{1}{\frac{1}{A_0} + \frac{R_1}{R_1 + R_2}} = \\ &= \frac{R_1 + R_2}{R_1} \cdot \frac{1}{1 + \frac{R_1 + R_2}{A_0 \cdot R_1}} = \frac{\Gamma}{1 + \frac{\Gamma}{A_0}} \end{aligned}$$

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

AtionINGS .

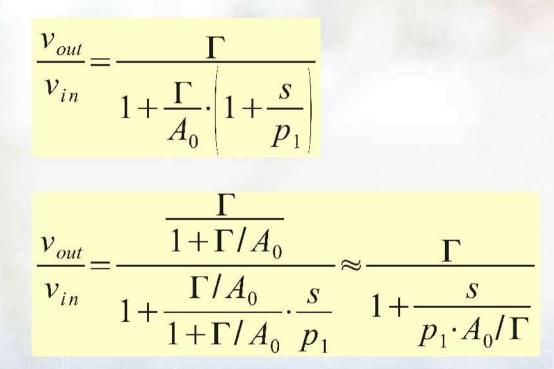

## Bandwidth

013-01-21::ANTIK\_0029 (P2A)

#### Single-pole (ignore effect of impedance):

#### The amplifier will band-limit the system!

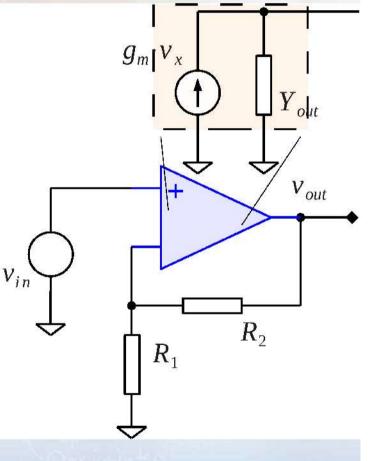

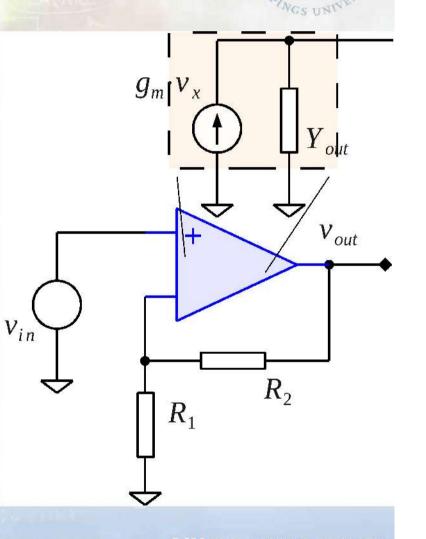

## More detailed model

$$v_x = \frac{R_1}{R_1 + R_2} \cdot v_{out}$$

$$g_m(v_{in} - v_x) + (0 - v_{out})Y_{out} + \frac{0 - v_{out}}{R_1 + R_2} = 0$$

$$g_{m}v_{in} = v_{out} \cdot \left[Y_{out} + \frac{1 + R_{1}g_{m}}{R_{1} + R_{2}}\right]$$

$$\frac{v_{out}}{v_{in}} = \frac{\Gamma}{1 + \frac{1}{g_m R_1} + \frac{\Gamma}{g_m / Y_{out}}}, \text{ etc., etc.}$$

StopINGS U.

LIU EXPANDING REALITY

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

## **Other practical concerns wrt. current**

#### **Feedback with resistors**

An OP given with a certain current drive capability will put requirements on the resistor sizes

What is the maximum swing?

What is the DC level?

2013-01-21::ANTIK\_0029 (P2A)

108 of 252

## Other practical concerns wrt. gain

#### Integrator

Effect of limited gain on integration

operation. Maximum integration is  $A_0$ .

#### Low-pass filter

-01-21::ANTIK\_0029

Effect on the filter bandwidth

#### How fast?

A closed-loop gain of 10 and a bandwidth of 25 MHz

## The "741 amplifier"

#### **Texas instruments**

opa 336 - what is the bandwidth?

opa 358 - what is the DC gain?

#### **Analog Devices**

AD854x - what is the DC gain, or what is the open-loop bandwidth?

LIU EXPANDING REALITY

2013-01-21::ANTIK\_0029 (P2A)

# **Operational amplifier architectures**

#### **Examples**

Telescopic

Two-stage

Folded-cascode

Current-mirror

Essentially just cascaded stages of different kinds

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

111 of 252

## **Telescopic OTA**

Stack many cascodes on top of each-other and use gainboosting, etc.

#### Omitted, since it is not applicable for modern processes.

The swing is eaten up.

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

LIU EXPANDING REALITY

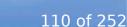

## **Two-stage OP/OTA**

StippINGS UN

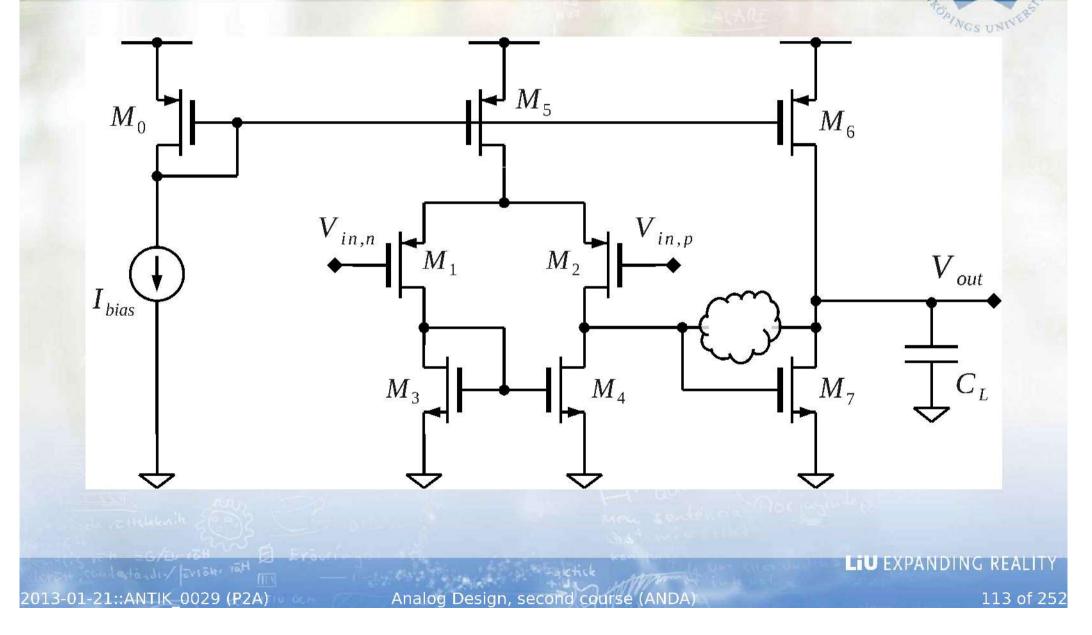

## **Current-mirror OP/OTA**

Storings UN

#### StopINGS . **Folded-cascode OP/OTA** NGS UN $V_{b,1}$ $M_3$ $M_{\scriptscriptstyle A}$ $V_{b,2}$ $V_{b,2}$ $M_6$ $M_7$ V<sub>out</sub>, p $V_{out,n}$ $V_{b,3}$ $V_{b,3}$ $M_1$ $M_2$ $M_9$ ${M}_8$ $V_{in,p}$ $V_{in,n}$ $C_L$ $V_{b,4}$ $V_{b,4}$ $V_{b,5}$ $M_{11}$ $M_{10}$ $M_5$

LIU EXPANDING REALITY

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

115 of 252

$C_L$

# **OP/OTA** Compilation

#### **Cookbook recipes**

Hand-outs with step-by-step explanation of the design of OP/OTAs

http://www.es.isy.liu.se/courses/ANDA/download/opampRef/ANTIK\_0N NN\_LN\_opampHandsouts\_A.pdf

**Compensation techniques**

http://www.es.isy.liu.se/courses/ANDA/download/opampRef/ANTIK\_0N NN\_LN\_opampCompensationTable\_A.pdf

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

LIU EXPANDING REALITY

## **Amplifier classes**

Not really covered in this course.

Analog Design, second course (ANDA

#### Different classes, such as

Class A, B, AB, C, D, E, F, G, H, I, K, S, T, Z, etc.

#### **Class** A

Essentially the common-source stage

**Class AB**

2013-01-21::ANTIK\_0029 (P2A

Essentially a push-pull configured class A

LIU EXPANDING REALITY

### What did we do today?

Wrapped up the CMOS part of the course

Wrapped a discussion on stability and compensation

Looked on the opamp

macro level

chip level

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

118 of 252

## What will we do next time?

# AND ANCS UNIVERSIT

#### Distortion

How is linearity of analog circuits defined?

What other cost measures are there to define analog quality?

#### Noise

What are the fundamental limits on performance and range?

What are the mathematical tools to find them?

2013-01-21::ANTIK\_0029 (P2A)

Analog Design, second course (ANDA)

119 of 252