# Lecture 9, ANIK

#### Data converters 1

har colui, seno

www.liu.sc/onlin

skovinch vettsteknih 2002 urrätt endlig vett EG/EU.vett crett, chalestands/ Evsek vätt s afterwards

Distaminasih

# What did we do last time?

Noise and distortion

Understanding the simplest circuit noise

Understanding some of the sources of distortion

LIU EXPANDING REALITY

2012-02-20::ANTIK\_0025 (P9A)

Analog (and discrete-time) integrated circuits

### What will we do today?

Data converter fundamentals

DACs

ADCs

2012-02-20::ANTIK 0025 (P9A)

Transfer characteristics

Error measures

Typical architectures

LIU EXPANDING REALITY

### **Data converters fundamentals**

#### DAC

Represents a digital signal with an analog signal To control something To transmit something (a modulated signal)

#### ADC

Represents an analog signal with a digital signal To measure something To receive something (a modulated signal)

#### And there are others:

.20…ANTIK\_0025 (P9

Time-to-digital converters Frequency-to-digital converters etc.

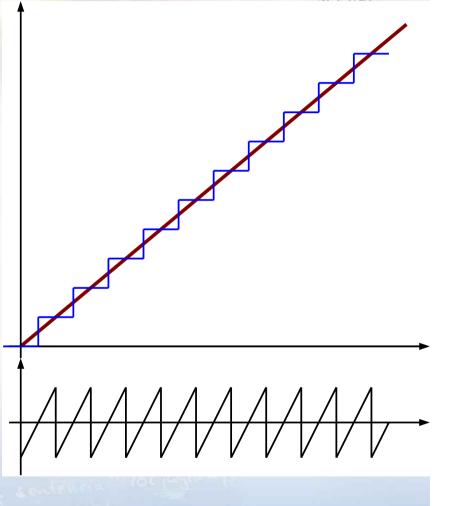

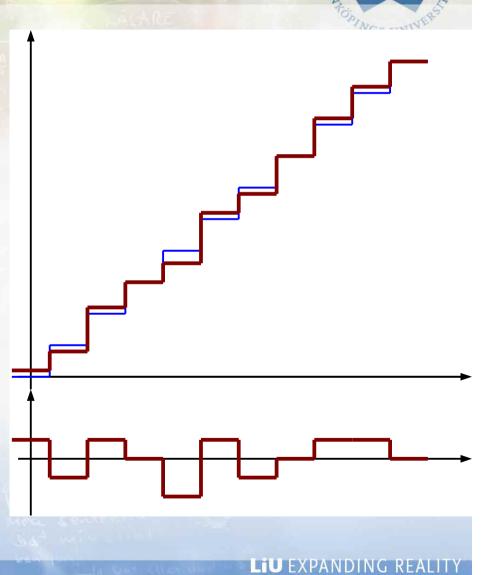

# The quantization process

Distinct levels can be detected (ADC)/represented (DAC)

The quantization error is the deviation from the straight line

Range is 0 to  $V_{ref}$ , which gives stepsize

$\Delta = \frac{V_{ref}}{2^N}$

The quantization error is bounded (as long as we do not saturate):

$$Q \in \left[-\frac{\Delta}{2}, \frac{\Delta}{2}\right]$$

\_0025

TT O LINGS UNIVERSITET O LAND

LIU EXPANDING REALITY

Assume signal-independent (not true for a low number of bits)

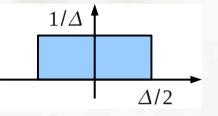

Quantization assumed to be a stochastic process Assume white noise, uniformly distributed in  $\left[-\Delta/2, \Delta/2\right]$

Noise power spectral density

Sigma of the probabilistic noise

Noise model

Remember the superfunction

Power spectral density

2012-02-20::ANTIK\_0025 (P9A

A certain bandwidth contains a certain amount of noise

#### LIU EXPANDING REALITY

Peak power assuming centered around the nominal DC level

$P_{pk} = \left| \frac{V_{ref}}{2} \right|^2$

Maximum, average sinusoidal power

$$P_{avg} = \frac{1}{2} \cdot \left(\frac{V_{ref}}{2}\right)^2 = \frac{1}{8} \cdot V_{ref}^2 = \frac{P_{pk}}{2}$$

Peak-to-average ratio (PAR) for a sinusoid

2012-02-20::ANTIK\_0025 (P9)

$$\frac{PAR = \frac{P_{pk}}{P_{avg}} = 2}{P_{avg}} (1.76 \text{ dB})$$

LIU EXPANDING REALITY

To LINGS UNIVERSITY OF THE STATES

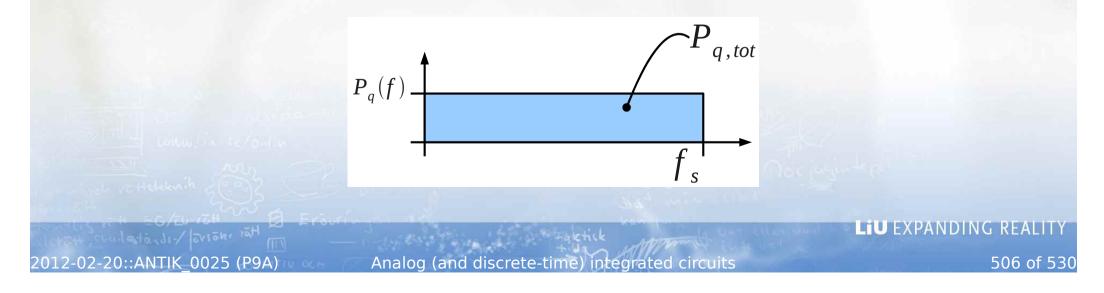

Noise power given by the sigma:  $P_{q,tot} = \sigma^2 = \frac{\Delta^2}{12}$

Signal-to-quantization-noise ratio:  $\frac{\text{SQNR} = \frac{P_{avg}}{P_{q,tot}} = \frac{P_{pk}}{P_{q,tot}} \cdot \frac{P_{pk}}{P_{q,tot}}}$

With values inserted

$$SQNR = \frac{\frac{1}{4} \cdot V_{ref}^2}{\frac{1}{12} \cdot \left|\frac{V_{ref}}{2^N}\right|^2 \cdot PAR} = \frac{3 \cdot 2^{2N}}{PAR}$$

In logarithmic scale

-20…ANTIK\_0025 (P9

SQNR  $\approx 6.02 \cdot N + 4.77 - PAR = 6.02 \cdot N + 1.76$  for our sinusoid.

## D/A conversion as such

Amplitude is generated by scaling the digital bits and summing them

$A_{out}(nT) = \sum_{k=0}^{N-1} w_k(nT) \cdot 2^k$

The scaling does not necessarily have to be binary:

Binary Thermometer Linear Segmented

2012-02-20::ANTIK\_0025 (P9A

LIU EXPANDING REALITY

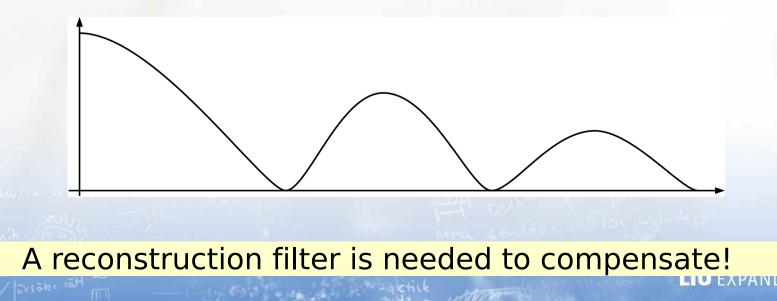

# D/A conversion, cont'd

The output is a pulse-amplitude modulated signal (PAM)

$$A_{out}(t) = \sum a(nT) \cdot p(t-nT)$$

such that the spectrum is

$$A_{OUT}(j\omega) = A \left( e^{j\omega T} \right) \cdot P(j\omega)$$

A common pulse is the zero-order hold, since ideal reconstruction is impossible. In the frequency domain the output will be sinc-weighted:

2-02-20::ANTIK\_0025 (P9A) Analog (and discrete-time) integrated circuits

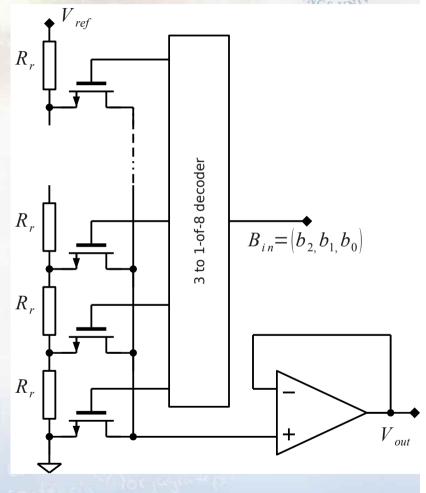

# **D/A converter architectures**

#### **Current-steering**

Outputs summed by weighted current sources. KCL simplifies this

Switched-capacitor (MDAC)

An SC gain circuit with weighted capacitors, c.f. the multiple input OP gain circuit

**Resistor-string**

Select a certain tap out of many and buffer to output

#### R-2R

Utilizes current dividers

And many more

2012-02-20::ANTIK\_0025 (P9A)

Oversampling DACs, etc.

LIU EXPANDING REALITY

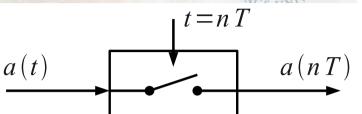

# **A/D** conversion

A/D conversion is essentially a sampling process

$a(nT) = a(t)|_{t=nT}$

Poission's summation formula

$A(e^{j\omega T}) = \sum A(j(\omega - 2\pi k) \cdot T)$

#### Spectrum might repeat and overlap itself!

LIU EXPANDING REALITY

2012-02-20::ANTIK 0025 (P9A)

Analog (and discrete-time) integrated circuits

## A/D conversion, cont'd

To avoid folding:

meet the sampling theorem (theoretically minimizes error) use an anti-aliasing filter (practically minimizes error)

Practically, an amount of oversampling is required to meet the tough filter requirements

Analog input is mapped to a digital code

\_0025

A range of the input mapped to a unique digital code

$$D(nT) = \sum_{k=0}^{N-1} w_k(nT) \cdot 2^k$$

# A/D converter architectures

#### Flash

A set of comparator measures the input and compares it with a set of references.

#### Sub-ranging

Use a coarse stage to quantize the input. Subtract the input from the reconstructed, quantized result, amplify it and quantize again.

**Pipelined**

A set of sub-ranging ADCs

Successive approximation

One sub-ranging ADCs looping in time rather than a straight pipeline.

And plenty of others

Slope, dual-slope, folding, Oversampling ADCs later today

### **Data converter errors, DNL**

THE OPTINGS UNIVERSITET

**Differential nonlinearity** is the deviations from the desired steps

$$DNL(n) = C_n - C_{n-1} - \Delta$$

or

$$DNL(n) = \frac{C_n - C_{n-1}}{\Delta} - 1$$

[LSB]

For full accuracy

2012-02-20::ANTIK\_0025 (P9A

$|\text{DNL}(n)| < 0.5 \text{ LSB } \forall n$

Often, the gain and offset errors are eliminated from the expression.

Analog (and discrete-time) integrated circuits

### **Data converter errors, INL**

Integral nonlinearity is the deviation from the desired "line"

Analog (and discrete-time) integrated circuits

$$\text{INL}(n) = C_n - n \cdot \Delta$$

or  $\text{INL}(n) = \frac{C_n}{\Delta} - 1$  [LSB]

For full accuracy

2012-02-20::ANTIK\_0025 (P9)

$|INL(n)| < 1 LSB \forall n$

One can also show that the INL is the sum of the DNL

#### **Data converter errors, relations**

#### Static measures

INL, DNL Gain, offset

#### Dynamic measures

-02-20::ANTIK\_0025 (P9A

Spurious-free dynamic range, SFDR Signal-to-noise-and-distortion ratio, SNDR Intermodulation distortion, IMD Resolution bandwidth Effective number of bits Glitches

#### Linearity errors are signal dependent!

# **Typical causes of static errors**

#### Mismatch in reference levels

The effective resistor sizes or currents might vary due to mismatch

#### Offset in comparators

2-02-20…ANTIK\_0025 (P9

Any "modern" continuous-time amplifier has signficant offset

#### Nonlinear effects due to unmatched biasing

A power rail will introduce a gradient which will give a nonlinear transfer

LIU EXPANDING REALITY

### Ways to circumvent the errors

#### Coding schemes in DACs

2012-02-20::ANTIK\_0025 (P9A

Thermometer vs binary Effects with respect to mismatch A first glance at a scrambling technique

Digital error correction in pipelined ADCs Revisited later

Analog (and discrete-time) integrated circuits

520 of 530

Integrating

### **Converter trade-offs, speed vs resolution**

A common figure-of-merit:

2012-02-20::ANTIK\_0025 (P9A

$FOM = \frac{4 k T \cdot f_{bw} \cdot DR}{P}$

Some conclusions from this formula

High-speed converters cost power

High-resolution converters cost area

Analog (and discrete-time) integrated circuits

Speed

Flash

521 of 530

### What did we do today?

Data converter fundamentals

DACs

ADCs

2012-02-20::ANTIK 0025 (P9A)

Transfer characteristics

Error measures

Typical architectures

LIU EXPANDING REALITY

### What will we do next time?

#### Data converter

Sigma-delta modulators

Some extras

2012-02-20::ANTIK\_0025 (P9A)

Wrap-up

Analog (and discrete-time) integrated circuits

523 of 530