## **EXAMINATION IN**

-TSEK37/TEN1

# ANALOG CMOS INTEGRATED CIRCUITS

| Date:     | 2014-01-18                |

|-----------|---------------------------|

| Time:     | 8-12                      |

| Location: | U1                        |

| Aids:     | Calculator, Dictionary    |

| Teachers: | Behzad Mesgarzadeh (5719) |

|           | Daniel Svärd (8946)       |

8 points are required to pass.

## Please start each new problem at the top of a page! Only use one side of each paper!

Page 2(8)

Page 3(8)

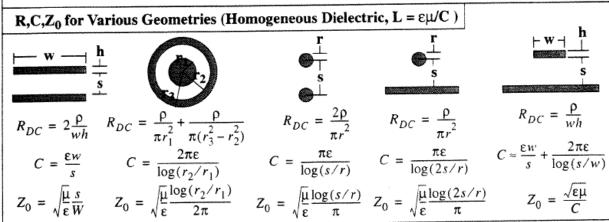

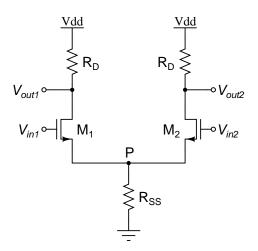

1) Fig. 1 shows a charge pump for a PLL. The switch transistors M1 and M4 have been placed outside the current mirror outputs (M2 and M3) to reduce glitches at the output node.

Fig. 1. Charge pump circuit.

All transistor sizes are 10µm wide and 0.35µm long. Neglect the channel length modulation and the body effect ( $\lambda = \gamma = 0$ ). Assume  $I_{ref} = 10 \ \mu A$ ,  $\mu_n C_{ox} = 150 \ \mu A/V^2$ ,  $\mu_p C_{ox} = 75 \ \mu A/V^2$ ,  $V_{tn} = 400 \ mV$ ,  $V_{tp} = -550 \ mV$  and  $Vdd = 3.3 \ V$ .

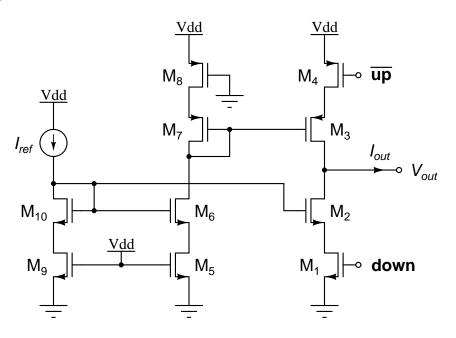

(a) Considering the timing diagram shown in Fig. 2, calculate the current  $I_{out}$  at time  $t_1$  and  $t_2$ , respectively. (2 p)

Fig. 2. Timing diagram for the charge pump.

(b) Calculate the output range of the charge pump. The output range is defined as the voltage range for  $V_{out}$  where  $M_2$  is saturated when the **down** signal is high and  $M_3$  is saturated when the **up** signal is low. (2 p)

Page 4(8)

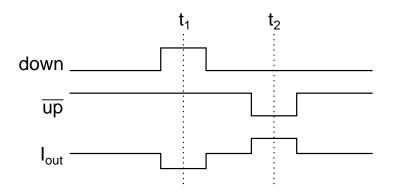

2) The differential amplifier in Fig. 3 is biased with a current source with finite output resistance  $R_{SS}$  (current source is not shown). The transistors in the circuit suffers from transconductance mismatch, i.e.  $g_{m1} - g_{m2} = \Delta g_m \neq 0$ .

Fig. 3. Differential amplifier circuit biased with non-ideal current source.

Determine an expression for the small-signal common-mode rejection ratio (CMRR) of the circuit. Assume the transistors are operating in the saturation region and that the load resistors are matched. Also neglect the channel-length modulation and body effect. (3 p)

Hint: The common-mode rejection ratio is defined as:

$$CMRR = \left| \frac{A_{DM-DM}}{A_{CM-DM}} \right|$$

where  $A_{DM-DM}$  is the gain from a differential input signal to the differential output and  $A_{CM-DM}$  is the gain from a common-mode input to the differential output.

Page 5(8)

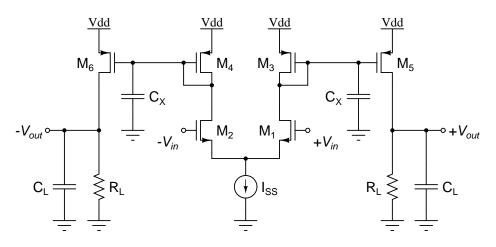

3) Fig. 4 shows a differential amplifier circuit. The amplifier is completely symmetric. Ignore all parasitic capacitances except for  $C_X$  and  $C_L$ . Also neglect the channel-length modulation and the body effect ( $\lambda = \gamma = 0$ ).

Fig. 4. Differential current mirror amplifier.

- (a) Draw the small-signal model and determine the transfer function of the amplifier. (2 p)

- (b) If  $g_{m3}=1.64$  mS,  $g_{m5}=4 \cdot g_{m3}$ ,  $R_L=1.5$  k $\Omega$ ,  $C_L=10$  pF, and  $C_X=0.5$  pF; calculate the value of  $g_{m1}$  to have a unity gain frequency of 2 Grad/s and calculate the phase margin assuming a feedback factor ( $\beta$ ) of 1. (2 p)

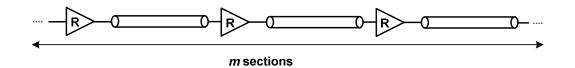

- 4) A 2-mm RC-wire is divided into *m* equal-length sections and *m* identical repeaters are inserted between the sections as shown in Fig. 5. Assume that the delay through an RC wire is  $0.38rcd^2$ , where *d* is wire length and *r* and *c* are resistance and capacitance per unit length. If  $rc = 960 \,\mu\text{s}$  and the propagation delay of each repeater is 50 ps, calculate the required number of sections to build a non-inverting signal propagation through the line with minimum delay. (3 p)

Fig. 5. Inserting repeaters to minimize the delay through the wire.

Page 6(8)

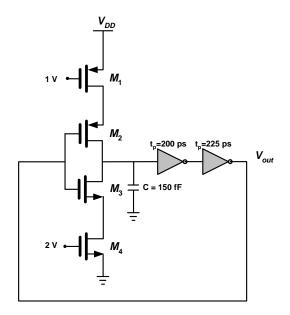

**5)** A 3-stage ring oscillator is shown in Fig. 6. Assume that the second and third stages are ideal inverters with a switching threshold at  $V_{DD}/2$  and their propagation delays are 200 ps and 225 ps, respectively. Furthermore, assume that M<sub>1</sub> and M<sub>4</sub> transistors (in the first stage) are long channel devices and M<sub>2</sub> and M<sub>3</sub> transistors are ideal switches with a switching threshold at  $V_{DD}/2$ . All of the parasitic capacitances of M<sub>1</sub> and M<sub>4</sub> can be ignored. Calculate the oscillation frequency of the oscillator. (4 p)

Fig. 6. A three-stage ring oscillator.

#### **Circuit parameters:**

| $V_{t0n} =  V_{t0p}  = 0.5 \text{ V}$  | $V_{DD} = 3 \text{ V}$ |

|----------------------------------------|------------------------|

| $\lambda_n = \lambda_p = 0$            | $(W/L)_1 = 40$         |

| $C_{ox}\mu_n = 200 \ \mu \text{A/V}^2$ | $(W/L)_4 = 20$         |

| $C_{ox}\mu_p = 50 \ \mu\text{A/V}^2$   | $\gamma=0$             |

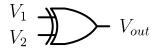

6) An XOR gate is utilized as phase detector in a DLL as it is shown in Fig. 7. Draw the input-output characteristic of the phase detector for the interval of  $[-2\pi, 2\pi]$  assuming that V<sub>DD</sub> is 3 V. (2 p)

**Hint:** Draw the average value of the output voltage  $(\overline{V_{out}})$  with respect to  $\Delta \phi$ , where  $\Delta \phi$  is the phase difference between the input signals.

Fig.7. XOR gate as phase detector.

Page 7(8)

### TRANSISTOR EQUATIONS

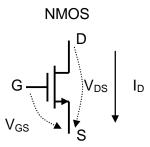

#### **NMOS**

• Cutoff:  $I_D = 0 \qquad (V_{GS} < V_{TN})$

Linear mode:

$$I_D = \mu_n C_{ox} \frac{W}{L} \left( (V_{GS} - V_{TN}) V_{DS} - \frac{V_{DS}^2}{2} \right)$$

$$(V_{GS} > V_{TN})$$

and  $(V_{DS} < V_{GS}$  -  $V_{TN})$

$$I = \frac{1}{2} \mu C \frac{W}{V} (V = V)^2 (1 + 2V)$$

(V = > V = ) and (V

$$I_{D} = \frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} (V_{GS} - V_{TN})^{2} (I + \lambda V_{DS}) \qquad (V_{GS} > V_{TN}) \text{ and } (V_{DS} > V_{GS} - V_{TN})$$

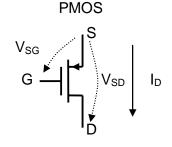

PMOS

٠

- Cutoff:  $I_D = 0 \qquad (V_{GS} < |V_{TP}|) \label{eq:ID}$

- Linear mode:

$$I_{D} = \mu_{p} C_{ox} \frac{W}{L} \left( \left( V_{SG} - |V_{TP}| \right) V_{SD} - \frac{V_{SD}^{2}}{2} \right) \qquad (V_{GS} > |V_{TP}|) \text{ and } (V_{SD} < V_{SG} - |V_{TP}|)$$

• Saturation mode:

**Saturation mode:**

$$I_{D} = \frac{1}{2} \mu_{p} C_{ox} \frac{W}{L} (V_{SG} - |V_{TP}|)^{2} (1 + \lambda V_{SD}) \qquad (V_{GS} > |V_{TP}|) \text{ and } (V_{SD} > V_{SG} - |V_{TP}|)$$

## **TRANSMISSION LINE EQUATIONS**

• Complex characteristic impedance

$$Z_c = \sqrt{\frac{R + j\omega L}{G + j\omega C}}$$

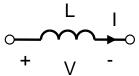

• Inductance voltage-current relation:

$$V = L \frac{dI}{dt}$$

• Characteristic impedance for lossless TL:

$$Z_0 = \sqrt{\frac{L}{C}}$$

• Capacitance voltage-current relation:

$$I = C \frac{dV}{dt}$$

С

LINKÖPING UNIVERSITY Behzad Mesgarzadeh Daniel Svärd Electronic Devices, Department of Electrical Engineering

Page 8(8)

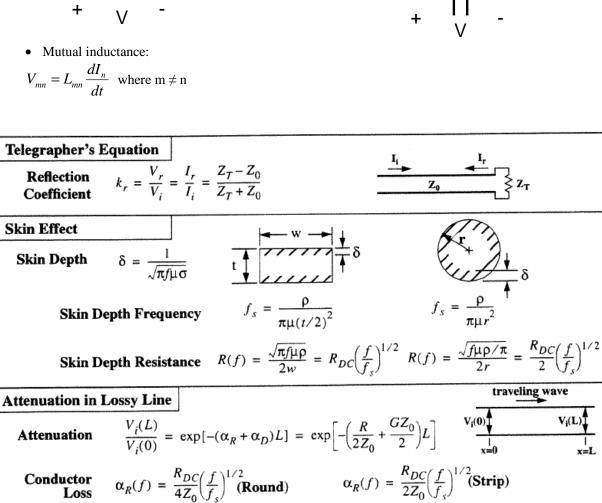

Mutual inductance:

Reflection Coefficient

Skin Effect

Skin Depth

Attenuation

Dielectric Loss (Homogeneous)

$$V_{mn} = L_{mn} \frac{dI_n}{dt}$$

where m  $\neq$  n

$\alpha_D(f) = \frac{\pi \sqrt{\varepsilon_r} \tan \delta}{c} f \qquad \begin{array}{c} \text{Dielectric Loss} \\ \text{Tangent} \end{array} \quad \tan \delta = \frac{G}{\omega C} = \frac{\sigma_{Diel}}{\omega \varepsilon_r} \\ \end{array}$