# VLSI Chip Design Project TSEK06

## Project description and requirement specification

Version 1.0

Project: 100MHz, 10dBm direct VCO modulating FM transmitter

**Project number: 7**

## **Project Group:**

| Name | Project members                  | Telephone | E-mail |

|------|----------------------------------|-----------|--------|

|      | Project leader and designer 1(5) |           |        |

|      | Designer 2(5)                    |           |        |

|      | Designer 3(5)                    |           |        |

|      | Designer 4(5)                    |           |        |

|      | Designer 5(5)                    |           |        |

Customer and supervisor: Amin Ojani

Office: B-house 229:224, Phone: 013-282716, Fax: 013-139282

Email: amin@isy.liu.se

## 1 Background

This document describes the design requirement specification of a direct VCO modulating FM Radio Transmitter. This simple transmitter can link your home entertainment system to a portable FM radio receive. For example, you can play a CD in your living room and listen to it on a portable radio in back yard.

#### 1.1 Project goal

The project goal is to design an integrated circuit (IC) in complementary metal-oxide semiconductor (CMOS) technology. Students, participating in this project as project members and project leaders, should learn the different steps of the IC design flow. That includes the given system architecture analysis, simulation, layout implementation and verification. The project students have an optional choice to manufacture the designed IC circuit on a chip. To test the manufactured chips, another course (TSEK11) is available after the project.

#### 1.2 Milestones and deadline

| 1: Project selection                                                                                   | Week 3      |

|--------------------------------------------------------------------------------------------------------|-------------|

| 2: Pre-study, project planning, and discussion with supervisor                                         | Week 4      |

| 3: High-level modeling design and simulation result (report)                                           | February 11 |

| 4: Gate/transistor level design and simulations result (report)                                        | March 11    |

| 5: Layout, DRC, parasitic extraction, LVS, post-layout simulations, modification and chip evaluations. | May 6       |

| 6: <b>DEADLINE</b> , Delivery of the completed chip.                                                   | May 13      |

| 7: <b>DEADLINE</b> , Final report, and oral presentation                                               | May 24      |

#### 1.3 Parties

The following parties are involved in this project:

- 1- Customer: Amin Ojani

- 2- Project supervisor: Amin Ojani

#### Tasks:

- Formulates the project requirements

- Provides technical support

- Reviews the project documents.

- 3- Project leader: One of the members in the design team.

#### Tasks:

- Responsible for organization of the team and the project planning.

- Divides the design and documentation work in an efficient way

- Organizes the team meetings as well as the meetings between the team and supervisor

#### **Direct VCO Modulating FM Transmitter**

- Keeps the supervisor informed about the progress of the project (at least one e-mail or meeting per week)

- 4- Project design members (including the project leader)

- Are equally responsible for project planning and design.

- Participate actively in all the meetings

- Support the team and the project leader

- Keep the team and project leader informed about the progress of their tasks.

## 2 Project description

#### 2.1 System description

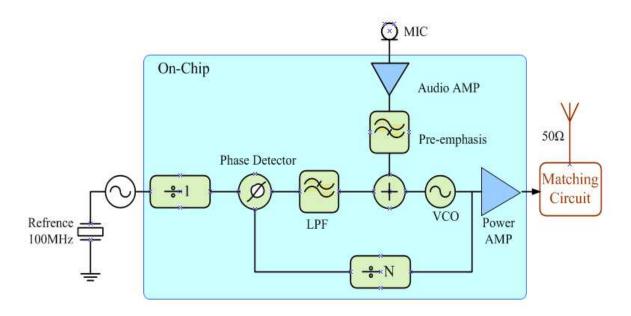

The system block level diagram is shown in Figure 1. The complete system to be built should include the on-chip audio amplifier, low pass filter (LPF), pre-emphasis circuit (optional), phase-frequency detector, VCO (e.g. current steering amplifier based or current starved inverter based voltage controlled oscillator) and power amplifier. The off-chip components include microphone coupling circuit and matching circuit (if needed) for antenna.

The core of transmitter is VCO whose centre frequency can be controlled by controlling the current through CSA (Current Steering Amplifier) or the current through current-starved inverter cells. This VCO do not need on-chip capacitor or inductor, although its phase noise performance is not as good as conventional VCO using inductor and varactors.

The 2<sup>nd</sup> most important component of design is the power amplifier. The class C type power amplifier is one candidate for this application (Razavi Chap-8). However, a simple output buffer might also be used as the power amplifier in this case.

The matching circuit can be resistor-capacitor circuit for simplicity. The more efficient matching circuits employ both L and C components. The MIC is ELECTRET Microphone with SNR better than 50dB. The headphone-mic set used with sound card of PC can also be used.

Figure 1: System Block diagram of 100MHz, 10dBm direct VCO modulating FM radio Transmitter.

#### 2.2 Typical Design Parameters

Power Supply  $3.3V \pm 5\%$

Transmitter Frequency 100 MHz

Out Put Power 10 dBm (10mW)

Modulation Frequency 100 Hz – 5 KHz (Audio)

Frequency Deviation  $\pm$  75 KHz

Audio Input Sensitivity 0.5V rms for +/- 75 KHz

Spurious Emissions Better than -45 dBc (with ref to carrier)

Total Power Consumption  $\leq 100 \text{mW}$

NOTE – Most countries accept emission of 10dBm in FM band including Sweden. So the maximum output power of transmitter is limited to 10 dBm (10mW). This will give more than 100 -200 meters of range with clear reception using typical commercial FM receiver. This is solely an educational project and no approval from any regulation agency is required to build and test this transmitter for educational purposes.

## 3 Area, performance requirements

The table below summarizes the FM transmitter performance requirements. Each requirement has its number, formulated text, and the given degree of priority. Three degrees of priority are used: high, medium, and low. High is a firm requirement with no possibility of relaxation, while medium requirements can be relaxed somewhat after good motivation.

| Requirement | Requirement text                                                                                                       | Priority |

|-------------|------------------------------------------------------------------------------------------------------------------------|----------|

| 1           | Integrate as many components as possible on-chip                                                                       | High     |

| 2           | Schematic and layout must be verified by simulation                                                                    | High     |

| 3           | Simulated chip power consumption < 100mW (3.3V supply)                                                                 | Medium   |

| 4           | Maximum transistor sizing < 200μm                                                                                      | Medium   |

| 5           | Chip core area < 0.27mm <sup>2</sup>                                                                                   | High     |

| 6           | Total project pin count: 12                                                                                            | High     |

| 7           | Design technology is AMS 4-Metal 0.35 μm CMOS                                                                          | High     |

| 8           | The most important system nodes should have off-chip access pins                                                       | Medium   |

| 9           | On-chip current densities < 1 mA/μm                                                                                    | High     |

| 10          | All requirements fulfilled in "typical", "slow", and "fast" process corners and for temperatures between 25 and 110 °C | Medium   |

| 11          | Power supply decoupling capacitors                                                                                     | High     |

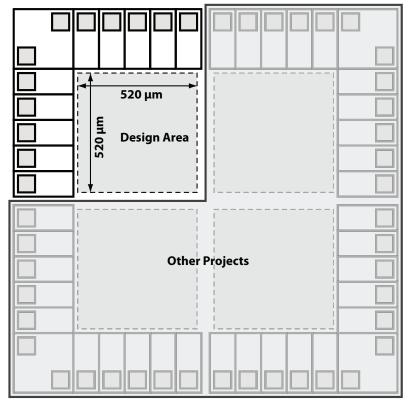

Figure 2: Schematic picture of a  $3\text{mm}^2$  chip with 40 generic pads four  $V_{DD}$  and four  $V_{SS}$  pads (total 48 pads), which will be shared between a number of projects.

#### 3.1 Available resources

- Scientific publication database (available from LiU):

- ♦ IEL IEEE/IEE Electronic Library, http://www.bibl.liu.se/english/databas/

#### 3.2 Tools

♦ Circuit simulation and layout tools from Cadence®, http://www.cadence.com/

#### 4 References

Howard.C.Yang, "A Low Jitter 0.3-165 MHz CMOS PLL Frequency Synthesizer for 3 V/5V operation", IEEE J of Solid State, 1997, Vol.32

Behzad Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill ISBN: 0072380322 (PLL and CMOS amplifier Chapters)

Behzad Razavi, "RF Microelectronics", Prentice Hall PTR, ISBN 0-13-887571-5, 1998 (Power Amplifier and Transmitter Chapters)

It is highly recommended that students taking this project also take the course TSEK02 and TSEK03.

For more literature and references consult with your supervisor.