## SOLUTIONS. Exam March 16, 2009 TSEI05 Analog and Discrete-time Integrated Circuits.

## **Exercise 1.**

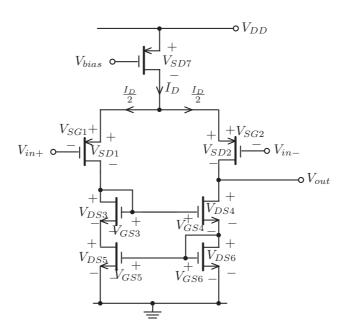

First notice that, because of symmetri, current through M1, M3 and M5 as well as current trough M2, M4 and M6 will be  $I_D/2$ .

$$\begin{aligned} -\mathbf{CMR} &= [V_{in,min}, V_{in,max}]. \\ V_{in,min} &= V_{GS6} + V_{GS4} + V_{SD1,min} - V_{SG1} = V_{eff6} + V_{tn} + V_{eff4} + V_{tn} + V_{eff1} - (V_{eff1} + V_{tp}) \\ &= \sqrt{\frac{I_D}{2\alpha_n}} + \sqrt{\frac{I_D}{2\alpha_n}} + 2V_{tn} - V_{tp} = 2\sqrt{\frac{I_D}{2\alpha_n}} + 2V_{tn} - V_{tp} \\ V_{in,max} &= V_{DD} - V_{SD7,min} - V_{SG2} = V_{DD} - V_{eff7} - (V_{eff2} + V_{tp}) = V_{DD} - \sqrt{\frac{I_D}{\alpha_p}} - \sqrt{\frac{I_D}{2\alpha_p}} - V_{tp} \\ &= V_{DD} - (1 + \sqrt{2})\sqrt{\frac{I_D}{2\alpha_p}} - V_{tp} \\ - \mathbf{OR} &= [V_{out,min}, V_{out,max}]. \\ V_{out,min} &= V_{GS6} + V_{GS4} + V_{SD1,min} - V_{SD2,min} = V_{eff6} + V_{tn} + V_{eff4} + V_{tn} + V_{eff1} - V_{eff2} \\ &= \sqrt{\frac{I_D}{2\alpha_n}} + V_{tn} + \sqrt{\frac{I_D}{2\alpha_n}} - \sqrt{\frac{I_D}{2\alpha_p}} - \sqrt{\frac{I_D}{2\alpha_p}} = 2\sqrt{\frac{I_D}{2\alpha_n}} + 2V_{tn} \end{aligned}$$

$V_{out,max} = V_{DD} - V_{SD7,min} - V_{SD1,min} - V_{GS4} + V_{DS4,min} = V_{DD} - V_{eff7} - V_{eff1} - (V_{eff4} + V_{tn}) + V_{eff4} = V_{DD} - \sqrt{\frac{I_D}{\alpha_p}} - \sqrt{\frac{I_D}{2\alpha_p}} - V_{tn} = V_{DD} - (1 + \sqrt{2})\sqrt{\frac{I_D}{2\alpha_p}} - V_{tn}$

Figure 1: Amplifier.

Answer:

$$\frac{\text{CMR}=\left[2\sqrt{\frac{I_D}{2\alpha_n}}+2V_{tn}-V_{tp},V_{DD}-(1+\sqrt{2})\sqrt{\frac{I_D}{2\alpha_p}}-V_{tp}\right]}{\overline{\text{OR}=\left[2\sqrt{\frac{I_D}{2\alpha_n}}+2V_{tn},V_{DD}-(1+\sqrt{2})\sqrt{\frac{I_D}{2\alpha_p}}-V_{tn}\right]}}$$

### **Exercise 2.**

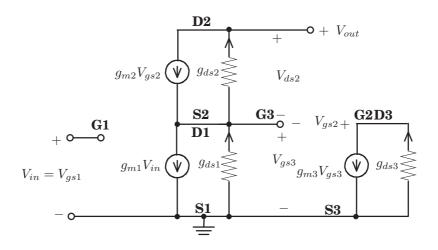

a) **Figure 2** shows a small signal equivalent. As the bias current sources ( $I_{01}$  and  $I_{02}$ ) are ideal they will be replaced by open circuits in the small signal equivalent circuit.

Notice that the current through  $g_{ds2}$  must be  $g_{m2}V_{gs2}$ . Then the current through  $g_{ds1}$  must be  $g_{m1}V_{in}$ . (Also the current through  $g_{ds3}$  must be  $g_{m3}V_{gs3}$ .)

Figure 2: Small signal equivalent.

From the small signal equivalent circuit we get:

$$V_{out} = V_{ds2} + V_{gs3} = -\frac{1}{g_{ds2}} g_{m2} V_{gs2} - \frac{1}{g_{ds1}} g_{m1} V_{in}$$

<sup>(1)</sup>

$$V_{gs2} = V_{G2} - V_{S2} = V_{G2} - V_{G3} = -\frac{1}{g_{ds3}}g_{m3}V_{gs3} - V_{gs3} = -V_{gs3}\left(1 + \frac{g_{m3}}{g_{ds3}}\right)$$

(2)

$$V_{gs3} = -\frac{1}{g_{ds1}} g_{m1} V_{in} \tag{3}$$

Equations (1)-(3) gives:

$$V_{out} = \left(\frac{g_{m2}}{g_{ds2}}\left(1 + \frac{g_{m3}}{g_{ds3}}\right) + 1\right) \left(-\frac{g_{m1}}{g_{ds1}}V_{in}\right)$$

(4)

Assuming that  $g_m >> g_{ds}$  equation (4) gives the transfer function:

$$H(s) = \frac{V_{out}}{V_{in}} = -\frac{g_{m1}}{g_{ds1}} \cdot \frac{g_{m2}}{g_{ds2}} \cdot \frac{g_{m3}}{g_{ds3}}$$

(5)

b) As  $g_m \propto \sqrt{\frac{W}{L}I_D}$  and  $g_{ds} \propto \frac{I_D}{L}$  we get from equation (5):

$$H = K \cdot \frac{\sqrt{\frac{W_1}{L_1}} I_{01} \cdot \sqrt{\frac{W_2}{L_2}} I_{01} \cdot \sqrt{\frac{W_3}{L_3}} I_{02}}{\frac{I_{01}}{L_1} \cdot \frac{I_{01}}{L_2} \cdot \frac{I_{02}}{L_3}}$$

(6)

As all  $L_i = L$  equation (6) can be written:

$$H = K \cdot \frac{\frac{\sqrt{W_1 W_2}}{L} \cdot I_{01} \cdot \sqrt{\frac{W_3}{L} I_{02}}}{\frac{I_{01}^2}{L^2} \cdot \frac{I_{02}}{L}} = \frac{\sqrt{W_1 W_2 W_3 L^3}}{I_{01} \sqrt{I_{02}}}$$

(7)

Answer:

$$f = \frac{\sqrt{W_1 W_2 W_3 L^3}}{I_{01} \sqrt{I_{02}}}$$

#### **Exercise 3.**

- A: M1 forms current mirrors together with M5, M7 and M9, giving the gainstages B, C and D appropriate current. The current through M10 can be changed by changing  $R_{offchip}$ .

- B: Forms a differential gain-stage. Gives the OP-amp. high input resistans. Gives also high gain.

- C: M6 and M7 forms a common source stage (CS-stage), giving high voltage gain.

Capacitor  $C_c$  is a feed-back capacitor that increases phase-margin. (Compensation capacitor.)

D: **M8** and **M9** forms a common drain stage (CD-stage) giving low output resistans to the OP-amp. (The CS-stage has a high ouput resistans, which means that excluding stage D we have an OTA, but in an OP-amp. we want low output resistans.)

#### **Exercise 4.**

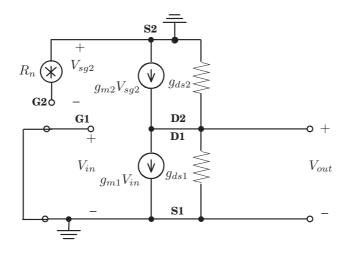

To determine the spectral density  $R_{out}$  on the output, caused by flicker noise at the gate of transistor **M2**, you first have to determine the transfer function from **G2** to output. I.e. you have to determine  $H(\omega) = V_{out}/V_{sg2}$  when  $V_{in}$  is short-circuited. Then you introduce the noise source between **G2** and **S2**.

If the flicker noise has spectral density  $R_n$  then  $R_{out} = |H(\omega)|^2 R_n$ .

Figure 3: Small signal equivalent circuit.

As  $V_{in} = 0$ ,  $g_{m1}V_{in} = 0$ .  $V_{out}$  then can be written

$$V_{out} = g_{m2}V_{sg2} \cdot \frac{1}{g_{ds1} + g_{ds2}} \Rightarrow H = \frac{V_{out}}{V_{sg2}} = \frac{g_{m2}}{g_{ds1} + g_{ds2}}$$

From the formulas at page 7 we have:  $R_n = \frac{K_2}{W_2 L_2 C_{ox2} f}$ Thus

Answer:

$$R_{out}(f) = \frac{g_{m2}^2}{(g_{ds1} + g_{ds2})^2} \cdot \frac{K_2}{W_2 L_2 C_{ox2} f}$$

# **Exercise 5**

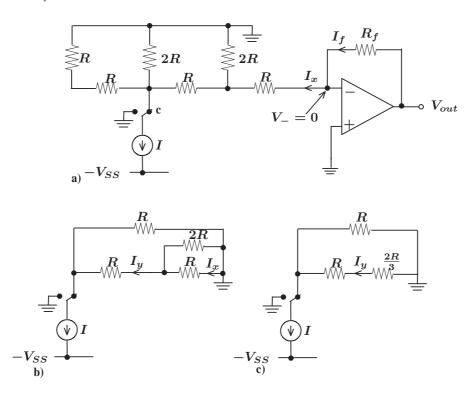

In Figure 4 a) below current  $I_x = I_f$  and voltage  $V_- = 0$  because OP-amp. is ideal. The voltage over  $R_f$  then will be  $V_{out} - 0$ .

Figure 4: D/A-converter.

$$I_x = I_f = \frac{V_{out} - 0}{R_f} \Rightarrow V_{out} = R_f I_f$$

As  $V_{-} = 0$  (virtual ground) the *R*, 2*R* resistor net can be redrawn as figures 4 b) and 4 c) show, to get the relation between currents  $I_x$ ,  $I_y$  and *I*. Current division in Figure 4 c) gives:

$$I_y = \frac{R}{R+R+\frac{2}{3}R} \cdot I = \frac{3}{8}I$$

Using current division and noticing that  $I_x = I_f$  Figure 4 b) gives:

$$I_f = I_x = \frac{2R}{R+2R} \cdot I_y = \frac{2}{3}I_y \Rightarrow I_f = \frac{2}{3} \cdot \frac{3}{8}I = \frac{1}{4}I$$

As  $V_{out} = R_f I_f$  we have, finally

$$V_{out} = R_f \frac{1}{4}I$$

Answer:

$$V_{out} = R_f \frac{I}{4}$$