## Written Test

## Course code: TSTE08, Exam code: TENA Analog and Discrete-time Integrated Circuits (ISY)

| Date:                                                                  | August 25, 2009                                                                                                                                                                                                                                                           |  |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Time:                                                                  | 8-12                                                                                                                                                                                                                                                                      |  |

| Place:                                                                 | G32                                                                                                                                                                                                                                                                       |  |

| Number of exercises:                                                   | 5 (5 points max. for each exercise)                                                                                                                                                                                                                                       |  |

| Grades:                                                                | 10p for 3 (ECTS: C), 15p for 4 (ECTS: B), and 20p for 5 (ECTS:A).                                                                                                                                                                                                         |  |

| Allowed material:                                                      | All types of calcuclators except laptops.<br>All types of official tables and handbooks.<br>Textbooks: Johns & Martin: Analog Integrated Circuit Design.<br>Razavi: Design of Analog CMOS Integrated Circuits.<br>Sedra&Smith: Microelectronic Circuits.<br>Dictionaries. |  |

| Examiner and responsible teacher:                                      | Sune Söderkvist                                                                                                                                                                                                                                                           |  |

| Course administrator:                                                  | Sune Söderkvist. Tel.: 281355, mail: sune@isy.liu.se                                                                                                                                                                                                                      |  |

| Visiting today:                                                        | Around 9.30 and 11.00 a.m.                                                                                                                                                                                                                                                |  |

| Corrrect (?) solutions:                                                | Solutions and results will be on the webb home page for the couse.                                                                                                                                                                                                        |  |

| Creaded energy and returned on energineteriz effect times treaders and |                                                                                                                                                                                                                                                                           |  |

# Graded exams are returned on examinator's office times, tuesdays and fridays at 11.00-13.00, during week no. 37 and 38.

#### **Students instructions**

- The CMOS transistor operation regions, small-signal parameters, and noise characteristics are found on the last page of this exam.

- Generally, do not just answer yes or no to a short question. You always have to answer with figures, formulas etc., otherwise no or fewer points will be given.

- You may write down your answers in Swedish or English.

## **Good Luck!**

#### **Exercise 1.**

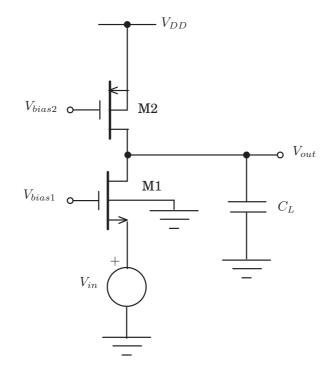

In this example we will study the small-signal properties of the capacitive-loaded amplifier in **Figure 1**. Assume that the transistors small-signal parameters are  $g_{m1}$ ,  $g_{mbs1}$ ,  $g_{ds1}$  and  $g_{m2}$ ,  $g_{mbs2}$ ,  $g_{ds2}$  respectively.

- a) Sketch a small-signal equivalent circuit and determine an exact expression for the transfer function  $H(s) = V_{out}(s)/V_{in}(s)$ . The bulk effect can **not** be neglected. However, all capacitors but  $C_L$  can be neglected. Also, determine the DC gain. (4p)

- b) Determine an exact expression for the small-signal output resistance,  $r_{out}$ . (1p)

Figure 1: Gain stage.

#### **Exercise 2.**

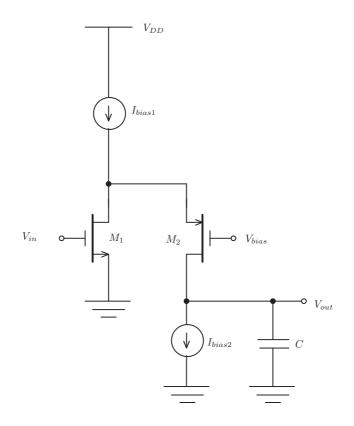

Show that, for appropriate value of  $V_{bias}$ , equal voltage at the output and input can be obtained for the cascode stage i **Figure 2**. Assume that both transistors are operating in the saturated region. The channel-length modulation can be neglected.

The transistors **M1** and **M2** have threshold voltages  $V_{tn}$  and  $V_{tp}$  respectively. The expression for  $V_{bias}$  may include  $V_{in}$ ,  $V_{tn}$  and  $V_{tp}$ ; no other voltages.

Figure 2: Folded cascode stage.

#### **Exercise 3.**

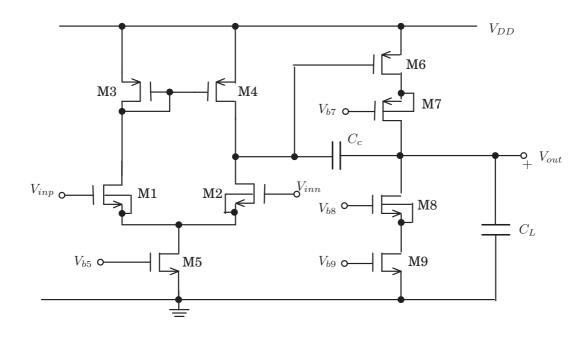

a) Derive the common-mode range, CMR, and the output range, OR, of the circuit in **Fig-ure 3**. You don't know anything about the relationship between sizes of different transistors. Threshold voltages may be different for all transistors. Anyhow all transistors are saturated.

The voltages should be expressed in currents  $I_{Di}$ , constants  $\alpha_i$ , threshold voltages  $V_{tni}$ and  $V_{tpi}$ . (3p)

b) What type of circuit is this?

The circuit can be seen as two different stages that are cascaded. What kind of stages are those two stages?

Why are transistors M7 and M8 included in the construction?

(2p)

Figure 3: Transistor circuit.

#### **Exercise 4.**

Consider the two cascaded common-cource stages in **Figure 4**, where only the thermal noise generated in the transistors is of interest. The current sources are ideal and hence noiseless. Let the output load capacitance be given by  $C_L$  and parasitic capacitances are only given by gate-source capacitance,  $C_{gs2}$ , for **M2**. Further  $I_{bias1} = I_{bias2} = I_{bias}$ . The transistors are identical with the small signal parameters  $g_{m1} = g_{m2} = g_m$  and  $g_{ds1} = g_{ds2} = g_{ds}$ . Both transistors operate in the saturation region.

Figure 4: A noisy multi-stage amplifier.

Determine an expression for the spectral density  $R_{out}$  of the output thermal noise assuming that the noise from the transistors are uncorrelated.

#### **Exercise 5.**

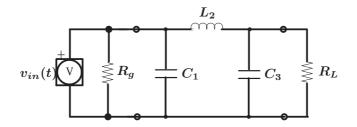

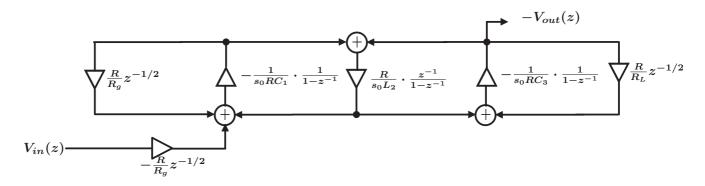

**Figure 5** shows an analog reference filter and a signal flow graph received after first synthesizing a leapfrog filter and then using a LDI-transformation followed by  $z^{-1/2}$  propagation. In next step, intending to realize a SC-filter, the factors  $z^{-1/2}$  in  $\frac{R}{R_g} z^{-1/2}$  and  $\frac{R}{R_L} z^{-1/2}$  are

deleted, among other things. That is actually equivalent to replacing  $R_g$  and  $R_L$  with  $R_g z^{-1/2}$  and  $R_L z^{-1/2}$  respectively.

Now focus  $R_g$  and show that this operation means that  $R_g$  changes to a resistor  $R'_g$  parallel to a capacitor  $C_x$ .

To compensate for that new capacitor you can change the value of capacitor  $C_1$  in the original analog reference filter. Determine the expression for this new capacitor  $C'_1$ !

Also determine the constant  $s_0$  so that a cut-off frequency  $f_{ac} = 100$  kHz for the analog filter will give a cut-off frequency  $f_c = 100$  kHz for the SC-filter. Sample period is  $T = 1 \ \mu$ s.

#### **LDI-transform:**

$$s = s_0(z^{1/2} - z^{-1/2})$$

$$\omega_a = 2s_0 \sin \frac{\omega T}{2}$$

Hint: Study  $\frac{1}{\frac{z^{1/2}}{B_z}}$

Figure 5: Analog filter and signal flow graph.

## Transistor formulas and noise

## **1 CMOS transistors**

Current and threshold voltage formulas and operating regions for an NMOS transistor

| Cut-off:    | $V_{GS} < V_t$                       | $I_D \approx 0$                                                  |

|-------------|--------------------------------------|------------------------------------------------------------------|

| Linear:     | $V_{GS} - V_t > V_{DS} > 0$          | $I_D = \alpha (2(V_{GS} - V_t) - V_{DS})V_{DS}$                  |

| Saturation: | $0 < V_{GS} - V_t < V_{DS}$          | $I_D = \alpha (V_{GS} - V_t)^2 (1 + \lambda (V_{DS} - V_{eff}))$ |

|             | $V_{DSsat} = V_{eff} = V_{GS} - V_t$ |                                                                  |

|             |                                      |                                                                  |

All regions:  $V_t = V_{t,0} + \gamma(\sqrt{2\phi_F - V_{BS}} - \sqrt{2\phi_F})$

#### **Small-signal parameters**

Linear: $g_m \approx 2\alpha V_{DS}$  $g_{ds} \approx 2\alpha (V_{GS} - V_t - V_{DS})$ Saturation: $g_m \approx 2\sqrt{\alpha I_D}$  $g_{ds} \approx \lambda I_D$

**Constants:**

$$\alpha = \frac{1}{2}\mu_{0n}C_{ox}\frac{W}{L}$$

$\lambda = \sqrt{\frac{K_s\epsilon_0}{2qN_A\phi_0}}\cdot\frac{1}{L}$   $\gamma = \frac{\sqrt{2qN_AK_s\epsilon_0}}{C_{ox}}$

## 2 Circuit noise

#### Thermal noise in CMOS transistors

The thermal noise spectral density at the gate of a CMOS transistor is

$$V^2(f) = \frac{8kT}{3} \cdot \frac{1}{g_m}$$

#### Thermal noise in resistors

The thermal noise spectral density of a resistor is modeled as a parallel noise current source

$$I^2(f) = \frac{4kT}{R}$$

#### Flicker noise in CMOS transistors

The flicker noise spectral density at the gate of a CMOS transistor is

$$V^2(f) = \frac{K}{WLC_{ox}f}$$