|     | No |

|-----|----|

| ity | 00 |

Title

Rev P1F Date 2013-02-26

ATIK and ANDA Exercises 2013

Repo/Course **ANTIK**

Page 70

ip jacwi50

## **EXERCISE SECTION 15: TIMING AND MISCELLANEOUS**

## 15.1. Loop filter of a PLL

Find the loop filter gain constant  $K_{lp}$  and  $\frac{\omega_z}{c_1}$  for the circuit with a  $\frac{C_2}{c_2}$  in parallel with  $\frac{R_1}{c_1}$  and  $\frac{C_1}{c_2}$  which are in series.  $\frac{R_1=10}{k}$ ,  $\frac{C_1=0.1\,\mu F}{c_1}$ ,  $\frac{C_2=0.01\,\mu F}{c_2}$ .

## Sources of Jitter and skew 15.2.

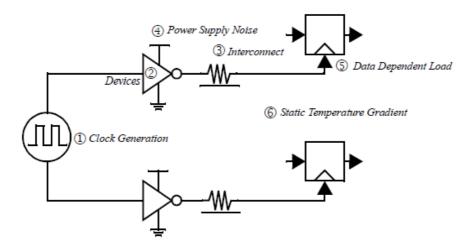

a. A balanced clock distribution scheme is shown in Figure 0.2. For each source of variation, identify if it contributes to skew or jitter. Circle your answer in Table 0.1

Figure 0.2 Sources of Skew and Jitter in Clock Distribution.

| 1) Uncertainty in the clock generation circuit | Skew | Jitter |

|------------------------------------------------|------|--------|

| 2) Process variation in devices                | Skew | Jitter |

| 3) Interconnect variation                      | Skew | Jitter |

| 4) Power Supply Noise                          | Skew | Jitter |

| 5) Data Dependent Load Capacitance             | Skew | Jitter |

| 6) Static Temperature Gradient                 | Skew | Jitter |

Table 0.1 Sources os Skew and Jitter