Projektarbete TSEA83

- Projektet utförs i grupper om 4 teknologer. Ni måste vara godkända på laborationerna innan projektet påbörjas!

- Bilda projektgrupp med fyra teknologer. Inregistrera projektgruppen genom att fylla i en projektanmälan (ska göras elektroniskt). Ni blir sedan införda i den stora tabellen .

- Välj sedan projekt Kursen heter ju Datorkonstruktion och

du kommer att använda FPGA-kortet Nexys3. Detta medför några

underförstådda krav för projektet:

- Projektet ska innehålla en fungerande dator som har signifikant användning, gärna av den typ du träffat på i kursen.

- Projektet ska ge utdata till någon utenhet, t ex kunna visa en rörlig bild på en VGA-skärm.

- Projektet ska kunna ta emot stimuli (insignaler) via någon inenhet, t ex tangentbord, joystick eller liknande.

- De knappar, strömbrytare och displayer som finns på själva Nexys3-kortet räknas *inte* som in/ut-enheter, men kan användas som komplement om man t ex till visa poäng på displayen.

- En grupp med fyra teknologer måste dessutom uppfylla något av följande krav:

- En pipeline-CPU

- Avbrotthantering

- Subrutiner med återhoppsadress på en stack

- Möjlighet att ladda in program via UART

- Snake

- Space Invaders

- Tetris

- Breakout

- Duck hunt

- Bilrally

- Lunar lander

- Skriv en enkel kravspecifikation för ert projekt. Lämna in kravspecen i gruppens kanal i Teams, under Files i katalogen Inlämningar.

- Skriv en enkel designskiss för ert projekt. Ta kontakt med er handledare. Denne godkänner designskissen och ger er utrustning. Lämna i designspecen i gruppens kanal i Teams, under Files i katalogen Inlämningar.

- Kursen avslutas med examination

Demo av tidigare projekt

uprogCPU, embryo för en mikroprogrammerad CPU

Filen uprogCPU.tgz innehåller VHDL-koden för ett litet mikroprogrammerat cpu-projekt. Den enda funktionalitet som finns är en enkel hämtfas som hämtar instruktioner från ett programminne PM till ett instruktionsregister IR. Miniprojektet visar hur man använder sig av hierakisk design med flera ingående VHDL-filer och en testbänk för simulering av konstruktionen. Tanka ned och packa upp filen med kommandot:

tar -xzvf uprogCPU.tgz

Då skapas katalogen 'uprogCPU' med diverse filer som behövs till ett projekt, bl a filen Makefile. Följande tre rader i Makefile är intressanta:

proj.%: S=uprogCPU.vhd uMem.vhd pMem.vhd

proj.%: T=uprogCPU_tb.vhd

proj.%: U=Nexys3_Master.ucf

Alla rader inleds med projektets namn 'proj' i detta fall. Det kan du byta till namnet på ditt eget projekt.

Den första raden innehåller filnamnen på dom ingående implementations-filerna i projektet. Det första filnamnet måste vara själva topp-modulen i projektet, då man gör en hierarkisk konstruktion.

Den andra raden innehåller namnet på testbänksfilen för toppmodulen.

Den tredje raden innehåller namnet på en s k user constraints file, vilken talar om vilka signaler och ben på FPGA:n som ska användas. Du måste själv redigera den filen och avkommentera dom signaler som ska användas i ditt projekt.

För att simulera konstruktionen med den ingående testbänken skriver man kommandot:

make proj.sim

Då startas programmet Modelsim, där ingående VHDL-filer kompileras och laddas in.

pipeCPU, embryo för en pipeline-CPU

pipeCPU.tgzDO-fil, för att slippa starta om Modelsim

Kort video som beskriver nedanstående

När man tröttnat på att starta om Modelsim varje gång man gjort en förändring i VHDL-koden så kan man istället skapa en s k do-fil med dom kommandon som behövs för att automatiskt kompilera om VHDL-filerna (för simulering) i projektet, lägga till önskade signaler i vågformsfönstret och köra om en ny simulering. Följande fil skulle kunna heta t ex uprogCPU.do och placeras i underkatalogen proj-simdir (proj i detta fall för att projektet heter proj). Därefter kör man kommando-filen i Modelsim genom att i kommadorutan skriva:

do uprogCPU.do

Filen uprogCPU.do:

vcom "+acc" ../uprogCPU.vhd ../uMem.vhd ../pMem.vhd

vcom "+acc" ../uprogCPU_tb.vhd

vsim uprogCPU_tb

add wave {sim:/uprogcpu_tb/uut/clk }

add wave {sim:/uprogcpu_tb/uut/rst }

add wave -dec {sim:/uprogcpu_tb/uut/upc }

add wave -hex {sim:/uprogcpu_tb/uut/tb }

add wave -hex {sim:/uprogcpu_tb/uut/fb }

add wave -dec {sim:/uprogcpu_tb/uut/pc }

add wave -hex {sim:/uprogcpu_tb/uut/ir }

add wave -hex {sim:/uprogcpu_tb/uut/u0/uaddr }

add wave -hex {sim:/uprogcpu_tb/uut/u1/paddr }

add wave -hex {sim:/uprogcpu_tb/uut/u1/pdata }

restart -f

run 20 us

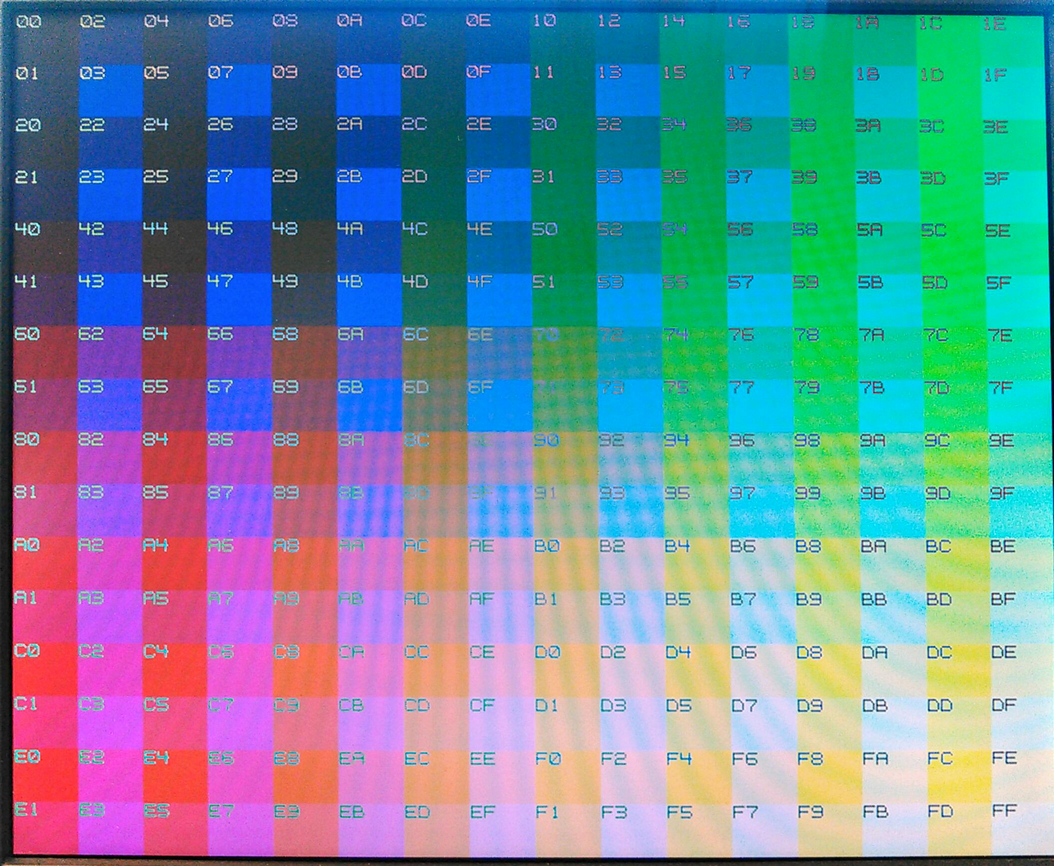

Color Chart

Programmera in följande fil i NEXYS3-kortet för att se en karta över alla de färger (med motsvarande HEX-kod) som kan genereras via VGA-porten:

color_chart.bitProgrammering kan ske med kommandot:

djtgcfg prog -i 0 -d Nexys3 -f color_chart.bit

Man kan aktivera/inaktivera grundfärgerna med switcharna:

sw7 : 1=enable/0=disable red

sw6 : 1=enable/0=disable green

sw5 : 1=enable/0=disable blue

sw1 : 1=altered/0=normal color counting order (in combo with sw0)

sw0 : 1=altered/0=normal color counting order (in combo with sw1)

Versionshantering med Git

För att gemensamt kunna arbeta parallellt med flera filer i projektet och samtidigt få en versionhantering av filerna kan man använda Git via gitlab.

Informationsansvarig: Anders Nilsson

Senast uppdaterad: 2022-02-08

LiU Homepage

LiU Homepage